面向宇航应用的高性能多核处理器S698PM芯片的设计

2016-07-21蒋晓华唐芳福龚永红颜志宇黄小虎

颜 军 蒋晓华 唐芳福 龚永红 颜志宇 黄小虎

珠海欧比特控制工程股份有限公司,珠海 519080

面向宇航应用的高性能多核处理器S698PM芯片的设计

颜 军 蒋晓华 唐芳福 龚永红 颜志宇 黄小虎

珠海欧比特控制工程股份有限公司,珠海 519080

综述了面向宇航应用的SPARC架构嵌入式处理器芯片的发展历程及技术产品,介绍了新一代SPARC架构多核处理器SOC芯片(S698PM芯片)的设计,阐述了其在性能优化和可靠性优化方面的设计方法。S698PM芯片架构采用SMP对称多处理架构,配置四核高性能SPARC V8处理器,具备二级缓存控制,数据吞吐能力大;芯片具备丰富的片上外设及宇航总线接口;支持多款嵌入式实时操作系统(EOS)。 关键词 SPARC V8 处理器;四核SOC处理器;RISC处理器;SMP对称多处理架构;宇航抗辐照芯片;检错纠错(EDAC);三模冗余(TMR);总剂量(TID);单粒子翻转(SEU);单粒子栓锁(SEL)

现代宇航的飞速发展,对航电系统、控制系统、星载计算机、空间站计算机、箭载计算机以及弹载计算机等关键电子系统的处理性能、可靠性、功耗和体积等方面提出了越来越高的要求,采用片上系统集成技术实现多个核心元器件或核心部件的集成设计成为宇航工程的关键技术手段,也是确保型号成功的关键因素[1]。

因行业的特殊性,以及宇航器件出口许可的敏感性及复杂规定,各航天大国对宇航核心器件及部件的国产化率及自主可控尤其注重。综观欧美及中国航天对于嵌入式处理器的应用发展,基本是围绕SPARC架构的RISC处理器来架构其核心电子系统及计算机系统。

1 SPARC宇航处理器的发展

欧空局(ESA)1992年采用SPARC 处理器作为其新一代的宇航处理器架构,并推出了第一款基于SPARC V7指令集的套片ERC32[2],1998年ESA又推出了整合ERC32套片之后的单片TSC695[3]。2002年Leon2[4]核发布;同年ATMEL公司基于LEON2核设计生产了高可靠宇航级芯片AT697[5]。2004年LEON3核由Gaisler公司发布。产品方面,瑞典AeroflexGaisler公司基于LEON3核开发了以GR712RC[6]为代表的宇航芯片。2010年,瑞典AeroflexGaisler公司公布了比LEON3核具有更高性能、更高集成度的LEON4核的设计思路[7]。LEON4核拟采用先进的“Non-blocking”流水线技术、指令流缓存器技术,具有带指令FIFO的浮点控制器,带DMA功能的缓存器控制器,128位处理器交互总线以及整型处理和浮点处理并行的双流水线指令执行系统[8]。LEON4是目前SPARC V8处理器的最新版本。

国内方面,SPARC架构嵌入式处理器和LEON核在2000年左右被引入,如今SPARC架构嵌入式处理器已成为中国航天领域的主流处理器。2003年欧比特公司推出了第一款基于LEON2核的处理器S698[9],之后又于2010年推出了S698-T[10]。2011年推出了基于LEON3核的四核处理器S698P4[11],2013年[12]欧比特公司自主研制了与LEON4核完全兼容的具有抗幅照性能的多核处理器S698PM成功流片,该芯片是世界上第一款兼容LEON4核的SOC芯片,除具有LEON4核所有的优点外,还集成了丰富的片内外设。另外,北京航天自动控制研究所基于LEON2核设计了PLC型箭载芯片[13],北京微电子技术研究所基于LEON2核设计了BM3803宇航芯片[14],北京控制工程研究所基于LEON3核设计了SOC2008[15]和SOC2012[16]宇航芯片。

2 S698PM芯片的主要优势

S698PM[17]芯片采用国际先进LEON4内核,具有以下特征:

1)高性能:采用对称多处理器(SMP)架构,内部集成4个同构的高性能处理器核心,核心与核心、核心与外设之间均通过特定的片内总线进行互联,以实现高速的数据交换;

2)高可靠:采用宽温物理工艺进行流片。采用三模冗余(TMR)技术对内部所有时序逻辑单元进行了冗余加固,采用检错纠错(EDAC)技术对内部存储器和外部存储器接口进行了检错纠错加固的抗辐照加固设计;

3)高集成度:片内集成了丰富的片上外设,包括GPIO、UART、定时器、中断控制器、调试支持单元、存储器控制器、1553B总线控制器、CAN总线控制器、以太网控制器、SpaceWire总线节点控制器、CCSDS遥控遥测控制器、USB2.0主控器、SPI主控器和I2C控制器等功能模块;

4)易使用:片内集成在线调试支持单元(DSU),可以通过UART、以太网或JTAG等接口直接连接DSU来访问芯片的寄存器、存储器和外设,方便进行软、硬件调试和开发。另外芯片支持eCOS,VxWorks及Linux等嵌入式操作系统,可方便地实现高性能多核并行处理系统的设计。

图1 S698PM芯片的结构框图

3 性能优化设计

本节将从芯片的片上总线设计、二级缓存设计等方面入手,阐述S698PM芯片获得高性能的设计方法和途径。

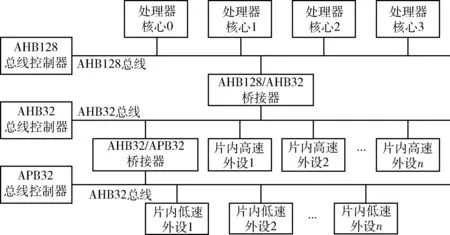

3.1 片上总线的设计

第一款SPARC V8四核并行处理器SOC芯片S698-P4由于内部4个处理器核心以及片内高速外设都通过一条32位带宽的AHB总线互联,结果造成了总线冲突和总线竞争的现象频发,极大地限制了S698P4芯片处理性能的提高。因此在设计S698PM时,对片内总线进行了重新设计(如图2所示):

1)4个处理器核心通过一条128位带宽的AHB总线(简称AHB128)进行互联;

2)采用一条32位带宽的AHB总线(简称AHB32)作为片内高速外设的互联总线;

3)采用一条32位带宽的APB总线(简称APB32)作为片内低速外设的互联总线;

4)AHB128,AHB32以及APB32均具有各自的总线控制器,控制和仲裁总线的访问操作;

5)AHB128总线与AHB32总线间通过AHB128/AHB32桥接器交换数据;

6)AHB32总线与APB32总线间通过AHB32/APB32桥接器交换数据。

图2 S698PM芯片的片内总线连接示意图

从图2可以看出,AHB128总线的主设备为4个处理器核心,从设备为AHB128/AHB32桥接器。AHB32总线的主设备为AHB128/AHB32桥接器,从设备为AHB32/APB32桥接器以及各片内高速外设(如以太网控制器、SpaceWire总线节点控制器和JTAG控制器等)。APB32总线的主设备为AHB32/APB32桥接器,从设备为各片内低速外设(如GPIO、UART、中断控制器和SPI主控器等)。采用上述设计方法提高了数据吞吐效率,从而提高了芯片的整体处理能力。

3.2 二级缓存设计

由于S698-P4处理器核心的一级缓存容量有限,使得处理器在计算过程中需要频繁地访问外部存储器,从而导致整个芯片的效率较低。为了规避此类问题,在S698PM芯片中加入了512KB的二级缓存(L2 Cache)。二级缓存位于外部存储器控制器与CPU互联总线AHB128之间(如图3所示)。AHB128总线是二级缓存的主机,二级缓存是外存储器控制器的主机。这种设计提高了处理器核心访问外部存储器的效率,进而提高了处理器的性能。S698PM芯片二级缓存的用户可用容量为512KB,但由于二级缓存需要支持EDAC功能,故其物理容量为512KB+128KB,其中128KB为EDAC校验码存放区,其对用户透明。

图3 S698PM L2 Cache的位置及连接关系示意图

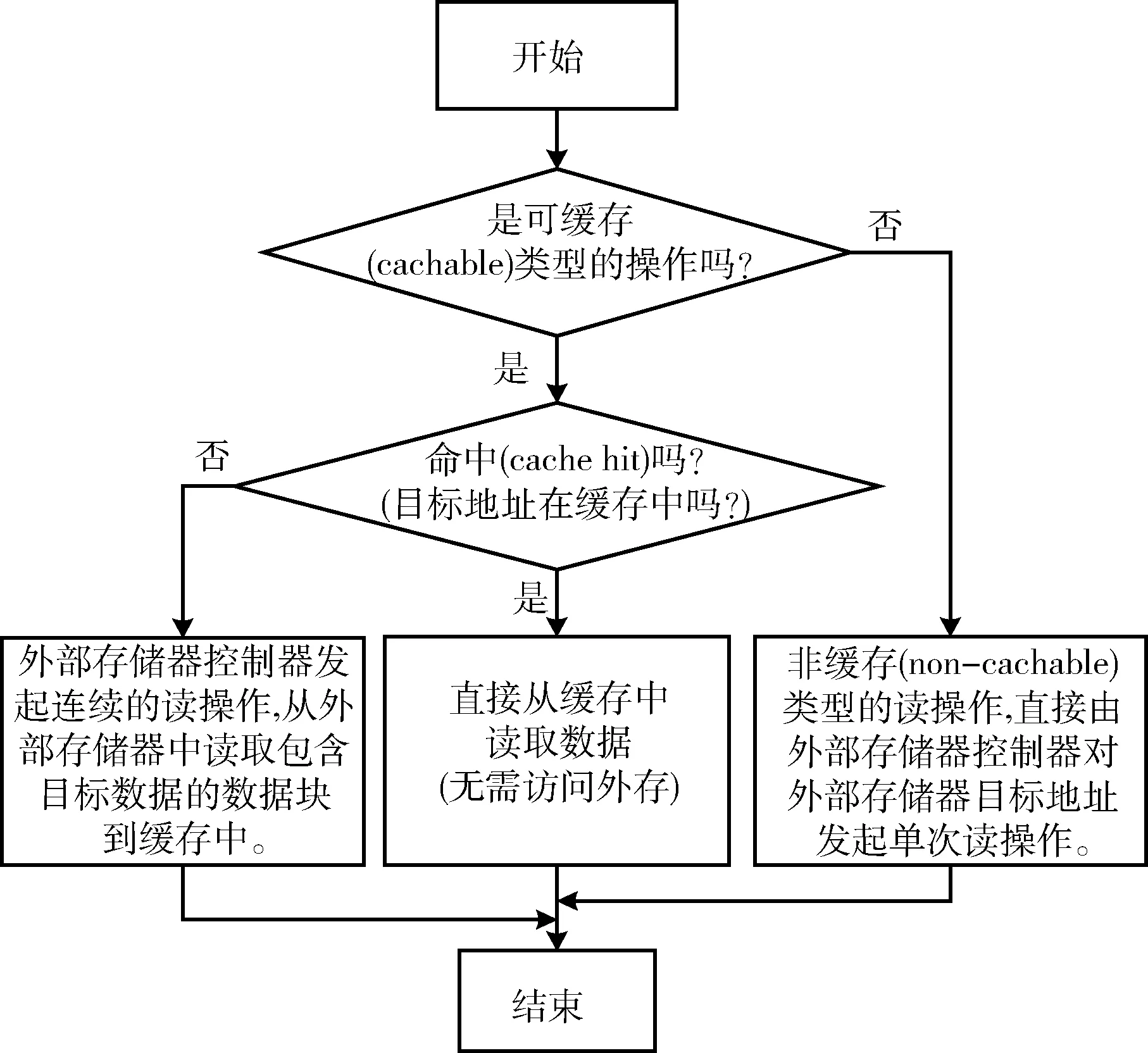

由于引入了二级缓存,S698PM芯片处理器核心对存储器的访问将有所不同,下面就以读数操作为例,描述处理器核心发起的读存储器数据的过程(如图4所示),写数操作与此类似,在此不做赘述。

图4 S698PM芯片二级Cache操作流程图

4 可靠性优化设计

S698PM芯片的目标应用领域是航空航天电子系统,因此要求S698PM芯片除了具有军用集成电路的可靠性指标外,还要具有一定的抗辐照能力,本节主要对S698PM芯片抗辐照加固设计进行阐述。

4.1 时序逻辑的抗辐照加固设计

在太空环境中,集成电路中的时序逻辑电路(主要指各类型的触发器Flip-Flop)可能受到高能粒子或射线的冲击,导致状态翻转,进而可能引起系统的误操作,造成严重后果,因此,需要对集成电路中的时序逻辑电路进行抗辐照加固设计[18]。另外,集成电路中的组合逻辑电路不具有状态记忆或状态保持功能,即使发生瞬间翻转,也会瞬时被输入状态刷新恢复,不会传递到下一级电路,即不会引起错误的传递,因此,不考虑对此类型电路进行抗辐照加固。

采用“三模冗余”(即TMR)[19]的方法对S698PM芯片中的时序各类型触发器进行加固,其原理如图5所示,而基本思路就是用电路b替换电路a(即用“3个同类型的触发器+3取2表决电路”替换1个原来的触发器),达到加固效果。从电路功能层面分析,电路a和电路b的真值表是等同的,故可以用电路b替换电路a。

对于电路a来说,如果在某一时刻,触发器被强射线击中,致使其输出Y发生错误翻转,而且该错误翻转状态至少会保持1个时钟周期,并且此错误翻转还会传递到下一级电路,引起不可预计的后果。

在图5中,电路c为“3选2表决电路”,其逻辑表达式如式(1):

Y=Y1*Y2+Y2*Y3+Y1*Y3

(1)

电路c是一个纯粹的组合逻辑电路,其包含4个标准单元(Standard Cell),即3个二输入与逻辑单元和1个三输入或逻辑单元。但在S698PM芯片中,为了减少“3选2表决电路”带来附加延时,设计了另外一款“3选2表决电路”(如图6所示),该电路由2个标准单元AOI2X3以及OAI2X3组成,其中AOI2X3逻辑表达式如式(2)所示,OAI2X3逻辑表达式如式(3):

D=A*B+C

(2)

D=(A+B)*C

(3)

根据图6所示的连接关系以及式(2)和(3)的逻辑关系,可以得出S698PM芯片的“3选2表决电路”的逻辑表达式,具体如式(4):

Y=Y1*Y2+Y2*Y3+Y1*Y3

(4)

图5 触发器三模冗余加固原理示意图

图6 S698PM“3选2表决电路”原理示意图

显而易见,式(4)与(1)完全一致,这说明图6所示的“3选2表决电路”与图5所示的“3选2表决电路”功能完全相同,但是前者只包含2个标准单元,布局布线后其电路面积、功耗以及延时等性能均优于后者。

4.2 存储器的抗辐照加固设计

在太空环境中,电子系统的存储器(如数据存储器RAM、程序存储器ROM以及片上缓存Cache等)中的存数单元(bit)也可能被高能粒子或射线打翻,发生单粒子翻转(SEU)事故。为了规避此类事故,需对系统的存储器的抗辐照加固。

S698PM芯片采用了检错纠错(EDAC)的方法来实现对片内存储器(如一级缓存、二级缓存等)以及外部存储器的抗辐照加固,其基本思路是:

1)在原存储器主机(如一级缓存控制器、二级缓存控制器、外部存储器控制器等)的后一级增加EDAC模块,使得系统具有自动产生校验码、自动检错、自动纠错和自动报告错误状态等功能;

2)对存储器进行扩展,在原有数据存储器基础上增加校验码存储器,校验码存储器与原有数据存储器共用地址、读有效、写有效以及片选信号,而且二者的存储器类型、操作时序以及地址深度需保持一致。

S698PM芯片对存储器的抗辐照加固设计的目标是“纠一检二”,即若“数据+校验码”发生一位错误,S698PM芯片将自动进行纠正;若“数据段+校验码段”发生两位或两位以上的错误,S698PM芯片将无法对其进行纠正,但要将错误状态以及该错误发生的地址报告给处理器核心。

图7 S698PM存储器检错纠错设计原理示意图

由图7可知,S698PM芯片中存储器检错纠错模块(简称EDAC模块)上包含“校验码生成”和“检错纠错”2个子模块,二者采用的算法都是汉明码(Hamming Code)算法。

5 结束语

综上所述,S698PM是一款高可靠、高性能和高集成度的SPARC V8 SMP架构多核SOC芯片,其片上外设资源丰富,支持嵌入式操作系统,包括:VxWorks,Linux,RTEMS,eCos等,可广泛应用于航空、航天领域,特别适合于需兼顾大量运算和复杂控制的宇航电子系统。测试结果表明当主频配置到500MHz时,芯片峰值处理能力(扣除系统开销因素)可达1652 DMIPS/1015MFLOPS。在可靠性设计方面,其总剂量(TID) 优于300Krad(Si),单粒子翻转(SEU)优于1E-5错误/器件/天,单粒子栓锁(SEL)优于99.8MeV.cm2/mg。因此,在核心宇航元器件的自主、可控、高性能国产化方面,S698PM处理器能够为我国航空航天电子系统提供技术及产品保障。

[1] 蒋彭龙,刘亮亮. 基于SOC的航天系统集成设计技术研究[J].现代防防御技术,2013,41(1):42-46.(Jiang Penglong,Liu Liangliang. Development and Application of SOC Techn-ology in Aerospace Field[J]. Modern Defense Technology,2013, 41(1):42-46.)

[2] J .Gaisler.LEON SPARC Processor The past, present and future[Z]. Gaisler Research,2010.

[3] TSC695F SPAR 32-bit Space Processor User Manual[Z]. Atmel Corporation,Dec,2003.

[4] LEON2 Processor User′s Manual[Z]. Gaisler Research, July 2005.

[5] Rad-Hard 32 bit SPARC V8 Processor AT697E User Manual[Z]. Atmel Corporation,Sep,2006.

[6] GR712RC Dual-Core LEON3FT SPARC V8 Processor User′s Manual. Aeroflex Gaisler AB, Feb 2013.

[7] J.Andersson, J.Gaisler , R.Weigand. Next Generation Multipurpose Microprocessor[J]. Proceedings of Dasia Data Systems in Aerospace, 2010,682:30-33.

[8] Quad Core LEON4 SPARC V8 Processor LEON4-N2X Data Sheet and User′s Manual[Z]. Aeroflex Gaisler AB, May 2013.

[9] 颜军. SPARC 嵌入式系统设计与开发-S698系列处理器实用教程[M].中国标准出版社, 2013.(Yan Jun.SPARC Design and Development of Embedded System[M].China Standards Press,2013.)

[10] S698-T用户手册[Z]. 珠海欧比特控制工程股份有限公司,2013.(S698-T User Manual,2013).

[11] 颜军,梁宝玉,等. 多核处理器S698P-SOC的数据一致性[J].航天控制, 2008, 26(5): 82-86.(Yan Jun,Liang Baoyu,et al. Data Consistency of 698P-SOC[J].Aerospace Control,2008,26(5):82-86.)

[12] 国内首款抗辐射型高性能32位四核并行处理器问市[J].电子产品世界,2013,(12):76.(Rad-hard and High-performance 4-core CPU Release[J].Electronic Engineering&Procuct World,2013,(12):76.)

[13] 宋征宇,刘亮亮.基于硬解题的PLC设计及其在测发控系统中的应用[J].航天控制, 2012, 30(5):78-82.( Song Zhengyu, Liu Liangliang. The Design of PLC Based on Hardware Logic Solver and Its Application in Test and Launch ControlSystem[J].Aerospace Control,2012,30(5):78-82.)

[14] BM3803MG 32位空间处理器用户手册[Z]. 北京微电子技术研究所,2010.(BM3803MG User Manual[Z],2010.)

[15] Liu H, Hua G, Zhang S,et al.Design and Verification of SOC2008 Processor Based on SPARC V8 Architechture For Sparc Applications[J].Electron Devices & Solid-state Circuits, International Conference ofs,2011:1-2.

[16] 北京控制工程研究所推出SoC2012芯片[J].军民两用技术与产品,2013, (12):21-21.(Beijing Institute of Control Engineering Release SoC2012 Chip[J].Dual Use Technologies&Products,2013,(12):21-21.)

[17] S698PM用户手册[Z]. 珠海欧比特控制工程股份有限公司,2016.

[18] 罗雁横,张瑞君.空间辐射环境与光器件抗辐射加固技术进展[J].电子与封装,2009, 9(8):43-47.(Luo Yanheng, Zhang Ruijun.Space Radiation Environment and Resist-Radiation Hardening Technology Progress of Optical Devices[J]. Electronics and Packaging,2009,9(8):43-47.)

[19] 崔媛媛,张洵颖,肖建青. TMR故障注入与验证方法研究与实现[J]. 计算机测量与控制,2014,1(13):13-15(Cui Yuanyuan, Zhang Xunying,Xiao Jianqing.Research and Implementation of Fault Injection in TMR and Verification Technique[J]. Computer Measurement& Control,2014,1(13):13-15.)

Design of High-performance Multi-core S698PM for Space Applications

Yan Jun,Jiang Xiaohua,Tang Fangfu,Gong Yonghong, Yan Zhiyu, Huang Xiaohu

Zhuhai Orbita Control Engineering Co.,Ltd., Zhuhai 519080, China

ThedevelopmentofSPARCarchitectureembeddedprocessorsforaerospaceapplicationsissummarized.Thedesignofanewgenerationofhighperformanceandradiation-hardenedSPARCmulti-coreprocessorSOCchip(S698PM)ispresentedwiththedescriptionofthedesigntechniquesofSOCperformanceandreliabilityoptimization.TheS698PMprocessorisdesignedinSMPsymmetricmultiprocessorarchitecturewithquad-corehighperformanceV8 SPARCprocessorsrunningona128-bithighspeedbus.Itisconfiguredwithtwo-levelcachemechanismwhichenablestheprocessortoachieveamuchhigherdatathroughputcapacity.TheS698PMprocessorhasfeaturesofsuperiorreliabilitydesignandavarietyofembeddedreal-timeoperatingsystems(EOS)isfullysupported.Duetoarichsetofon-chipperipheralsandextensiveaerospacebusinterfacesdesigned,theS698PMprocessorisaidealdesignforaerospaceorientedapplications.

SPARC V8;Quad-coreSoC;RISC; SMParchitecture;Rad-hardenedprocessor; EDAC;TMR; SEU;TID; SEL

2016-06-23

颜 军(1962-),男,山东人,博士,主要研究方向为智能控制、模糊控制、高可靠嵌入式控制器及SOC芯片的设计及产业化;蒋晓华(1978-),男,湖南人,硕士,高级工程师,主要研究方向为计算机智能控制、多核架构芯片设计;唐芳福(1978-),男,湖南人,工程师,主要研究方向为系统集成设计、高可靠SOC设计;龚永红(1977-),男,湖北人,工程师,主要研究方向为嵌入式操作系统;颜志宇(1984-),男,山东人,工程师,主要研究方向为多核芯片应用;黄小虎(1967-),男,山东人,工程师,主要研究方向为多核芯片应用。

TP332

A

1006-3242(2016)04-0089-06