一种12位100MHz流水线ADC采样保持电路

2016-07-05孙海燕北方工业大学电子信息工程学院北京100144

栾 舰,孙海燕北方工业大学电子信息工程学院,北京 100144

一种12位100MHz流水线ADC采样保持电路

栾舰,孙海燕

北方工业大学电子信息工程学院,北京100144

摘要本文设计了一款基于SMIC130nm标准CMOS工艺的应用于12位流水线ADC的采样保持电路。采保(SHA)采用翻转围绕式结构,以减小电容的匹配要求、降低整体功耗;采用增益提高型二级运算放大器,以保证所设计的电路处理信号的速率与精度。通过仿真结果表明,采保电路(SHA)符合12位流水线ADC的性能要求。

关键词流水线ADC;采样保持电路;增益提高运算放大器

采保电路(SHA)对于流水线ADC很重要,其作用是对持续变化的模拟量输入信号的值进行采集,并在输出端对这个采样信号保持一段时间,以保证在给定采样频率下,后续电路对其进行处理,采保电路(SHA)的性能指标直接影响流水线ADC的速率与精度。

本文对采保(SHA)电路进行研究,通过对两种不同类型的采保的分析,最终选择翻转围绕式结构,设计了高性能的增益提高型运放,以满足电路的速率与精度的要求,最终设计实现了应用于12位100MHz流水线ADC的采保(SHA)电路。

1 采保结构的分析与选择

闭环结构的采保(SHA)电路主要有两种结构[1-3]:重分配电荷式和翻转围绕式。在采样相,重分配电荷式采保的采样电容对输入模拟量进行采集;在保持相,对采集信号的电容上的电荷重新分配,使其移动到反馈电容上,从而实现采样保持功能。翻转围绕式采保则是在保持相通过翻转采集信号的电容,实现了采样保持作用。二者相比较,在信噪比相同要求下,重分配电荷式采保电路在采样相与保持相的热噪声均为翻转围绕式采保电路的2倍。且因为重分配电荷式采保电路(SHA)的反馈系数是翻转围绕式采保电路(SHA)的一半,所以在相同建立速率要求下,前者的单位增益带宽是后者的两倍,即前者的运放要比后者的运放功耗大很多。所以综上考虑,本文选择翻转围绕式采保电路。

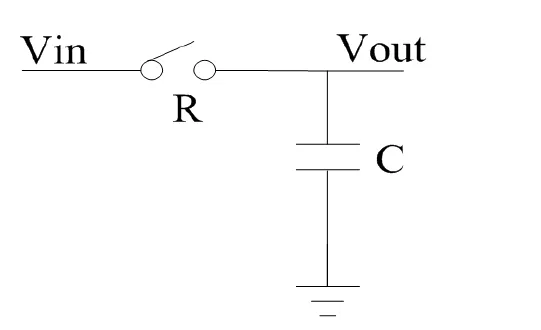

翻转围绕式采保电路由高增益型两级运放,开关和采集信号的电容组成。采保(SHA)电路结构如下图1所示。

图1 采保(SHA)电路结构图

当CLK1,CLK11闭合,CLK2断开,电路进入采样状态,VIN对采样电容Cs充电,当CLK11断开的瞬间,完成对采样电容Cs的下极板采样;随后CLK1断开,接着CLK2闭合,电路进入保持状态,采集信号的电容Cs上存储的电荷被传送到输出,由于两级运放的负反馈和高增益,在输出稳定时,运放的输入点‘虚地’,因为P点电荷不发生改变,所以输出电压VOUT=VIN。

2 误差分析

采保电路(SHA)的偏差基本由以下几点组成:

1)采样保持电路的热噪声。

2)采保电路(SHA)的时钟馈通与电荷注入。

2.1采保(SHA)电路的热噪声

图2 热噪声模型

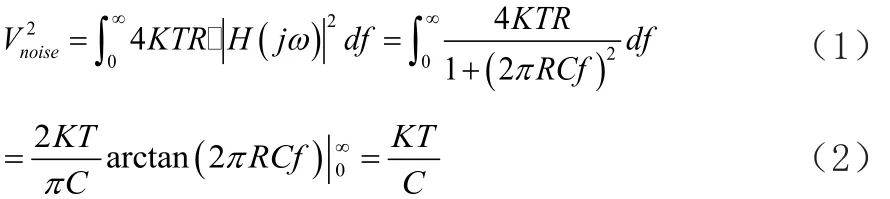

采保电路等效结构图如图2示,设开关的采集信号的电容的值为C,导通电阻值为R。开关导通时的热噪声功率为4kTR,S/H的传输函数为:

总噪声功率为:

而流水线ADC的量化噪声是LSB2/12,LSB=(FS/2n)/12,FS是量化范围,LSB是ADC的最小分辨率。采保电路的噪声要求小于一半的量化噪声,所以由3.1推出的采样电容需满足:

2.2采保电路(SHA)的时钟馈通与电荷注入

当开关管处于闭合状态时,由于界面存在反型层,设值为Q的电荷存在于反型层中,开关打开阶段,电荷Q会通过开关管的漏端泄露出来,注入到Cs中的这部分电荷,使得采集信号的电容存储的电荷值产生偏差。开关管还会通过栅漏之间的重叠电容将时钟信号跳变状态附加到采集信号的电容上,这种变化会给输出电压引入一定的偏差。

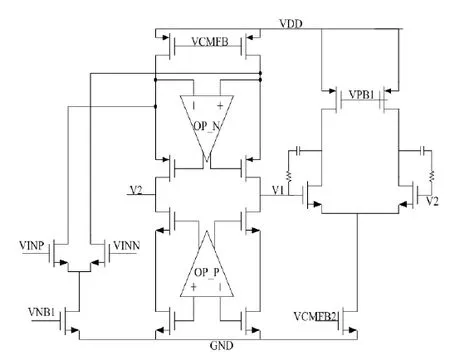

3 运算放大器的设计

图3 高增益型两级运算放大器

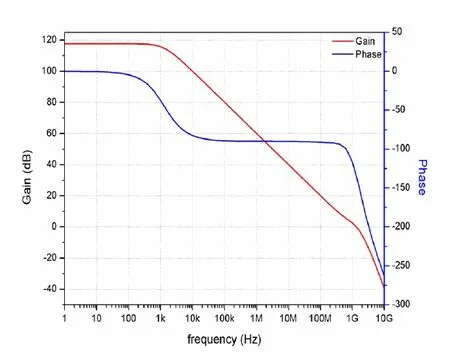

对于12位100MHz的流水线ADC,所需要最小的直流增益为78dB,0dB时所对应的带宽值为800MHz。下面对高增益型两级运放(OTA)进行交流分析,结果如

图4 运放的交流仿真结果

从图中直观的得出高增益两级运放的增益值117.8dB,相位裕度值45°。

4 仿真结构

采保(SHA)电路输出波形。

图5 采保电路(SHA)瞬态输出波形

输入1.02Mhz的正弦波信号,采样频率为100MHz,输出波形如上图,采样波形连续稳定,达到预期目标。

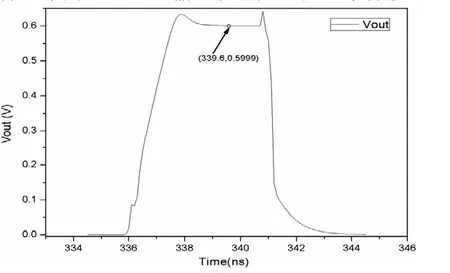

图6 采保电路(SHA)建立时间波形

从图6中可以看出,经过3.96ns,采样精度已经达到12bit精度的0.5LSB。

5 结论

本文在SMIC130nm标准CMOS工艺的支持下设计了一款应用于12位100MHz流水线ADC的采保(SHA)电路,采用翻转围绕式结构,设计了高增益高带宽型两级运放,保证了所设计电路处理信号的速率与精度。通过输入1.02MHz的正弦波信号,在100MHz的采样频率下,仿真结果完全满足设计要求。

参考文献

[1]S.H.Lewis,P.R.Gray. A pipelined 5M sample/s 9-bit an- alog-to-digital converter[J].IEEE Journal of Solid-StateCircuits,1987,22(6):954-961.

[2]W.Yang,D.Kelly, A 3-V 340mW 14-b 75-MS/s COMS ADC with 85-dB SFDR at Nyquist input[J].IEEE Jour-nal of Solid-State Circuits,2001,36(12):1931-1936.

[3]潘星,王永禄,裴金亮.一种高性能采样/保持电路的设计[J].微电子学,2008,38(3):442-444.

中图分类号TP33

文献标识码A

文章编号1674-6708(2016)165-0237-02

作者简介:栾舰,硕士在读,北方工业大学,研究方向为模拟集成电路设计。