基于Cadence的DDR2串扰研究与仿真

2016-06-29马祖杰

董 辉,马祖杰

(浙江工业大学 信息工程学院,浙江 杭州 310023)

基于Cadence的DDR2串扰研究与仿真

董辉,马祖杰

(浙江工业大学 信息工程学院,浙江 杭州 310023)

摘要:随着系统的工作频率及信号边沿转换速率的不断提高,串扰对于信号完整性的影响日益突出.通过对传输线串扰形成机理的分析,使用Cadence仿真软件对系统中的DDR2 SDRAM的数据线进行串扰仿真,给出了合理处理串扰问题的解决方案.对于数据线的近端串扰和远端串扰仿真分析,在理论及仿真结果的基础上,可以通过减小耦合线长度、增大耦合线间距和减小反射等方法降低串扰对于电路的影响.笔者提出了PCB设计中抑制串扰的一些有效措施,对于DDR2 SDRAM的信号完整性设计有一定的指导意义.

关键词:串扰;近端串扰;远端串扰;耦合

当今,信号频率日益提高,电路板的面积越来越小,因此信号完整性问题现象也就越发的凸显出来[1].而在信号完整性的问题中,串扰则是造成其主要的噪声之一.随着数字系统的工作速度的增加,布线密度的增加,串扰对于系统所产生的影响越来越严重.过大的串扰会严重影响系统的性能,造成不可估量的损失[2].伴随着电子系统时钟频率的提高,存储器技术特别是DRAM技术也得到了飞速发展.目前,DDR2高速内存在嵌入式系统的应用中担任着中流砥柱的角色.在DDR2的应用中,信号完整性是必须要重点考虑的问题.由于DDR2传输速度快,传输线较多,由此引发的串扰问题是信号完整性设计中的重点.通过研究串扰的原理,借助cadence仿真软件对于DDR2走线所产生的串扰问题进行研究,并根据仿真结果提出了几种抑制串扰的方法.

1串扰形成的机理

串扰源于不同网络的传输及返回路径间边缘电场所引起的互容以及边缘磁场所引起的互感共同作用引起的噪声干扰[3].串扰会带来两个网络之间的信号完整性问题,在电路中的所有的网络之间都存在着串扰问题,通常将携带噪声的网络称之为攻击网络,而把受其他网络干扰而被动产生噪声的网络称之为受害网络[4].

串扰分为容性串扰和感性串扰.通常,容性串扰和感性串扰是同时发生的.容性耦合源于攻击网络上的电压产生改变,变化的电压在受害网络上引起感应电流进而导致电磁干扰.感性耦合源于攻击网络上的电流产生变化,变化的电流在受害网络上引起感应电压进而导致电磁干扰[5].这就是串扰产生的物理根源.在容性耦合和感性耦合的共同作用下,将接近受害网络近端所产生的串扰称为近端串扰,记为VNE.接近受害网络远端所产生的串扰称为远端串扰,记为VFE.通过部分简化的假设,可以得到串扰在理论上的计算公式[6].

近端串扰总噪声为

(1)

远端串扰总噪声为

(2)

其中:CmL为单位长度互容;LmL为单位长度互感;CL为信号路径上单位长度电容;LL为信号路径上单位长度电感;v为信号传输速度;L为两条耦合线之间耦合区域的长度;RT为干扰源的上升时间.

互连系统中,所有的主要部件(例如:PCB、封装、连接器等)都可能产生较大的串扰,从而对系统系能造成损伤[7].由以上分析可知:影响串扰的因素主要包括线间距、耦合长度、干扰源信号频率、传输线阻抗以及反射等,下面将通过仿真对比研究这些因素对于串扰的影响.

2DDR2串扰分析

设计采用两片型号为MT47H64M16的DDR2 SDRAM,其中每一片的MT47H64M16中包含16 bit数据线,故2片MT47H64M16共有32 bit的数据总线与DSP互连.数据线采用点对点连接的方式,而2片DDR2 SDRAM则共享地址线和控制命令线.

根据DDR2 SDRAM的技术文档可知:MT47H64M16数据总线的高电平电压门限值为VREF+0.25,低电平电压门限值为VREF-0.25,其中VREF为数据线的参考电平(0.9 V).设计要求串扰电压与噪声叠加到数据线上以后,不会影响门限电压对高低电平的判决,由以上计算可得,为不影响对于低电平的判断,其峰值应小于0.65 V,为不影响对于高电平的判断,其峰值应大于1.15 V.根据DSP的技术文档可知,TMS320DM6437与DDR2 SDRAM数据总线所连接的引脚电平类型为SSTL_18,而SSTL_18高电平门限电压为VREF+0.125,低电平门限为VREF-0.125,其中VREF为参考电平(0.9 V).同样设计要求串扰电压与噪声叠加到数据线上以后,不会影响门限电压对高低电平的判决,故可知不影响低电平判断的峰值应小于0.775 V,不影响高电平判断的峰值应大于1.025 V[8].

3仿真分析串扰

3.1建立串扰仿真模型

采用Cadence公司的SigXplorer信号完整性仿真软件对DDR2 SDRAM的数据线的串扰进行仿真.首先获取器件MT47H64M16和TMS320DM6437的IBIS模型,并利用Cadence公司的Model Integrity将IBIS模型转换成DML模型.然后提取MT47H64M16的数据线与DSP引脚相连的实际拓扑结构进行仿真.通常相邻最近的两条攻击网络对于受害网络产生的噪声最严重,一般只考虑受害网络与两条临近的攻击网路之间的耦合,就可以包括总噪声值的95%[9].故给出三平行传输线串扰模型如图1所示.

图1 三平行传输线串扰模型Fig.1 Three parallel transmission line crosstalk model

3.2耦合长度对串扰的影响

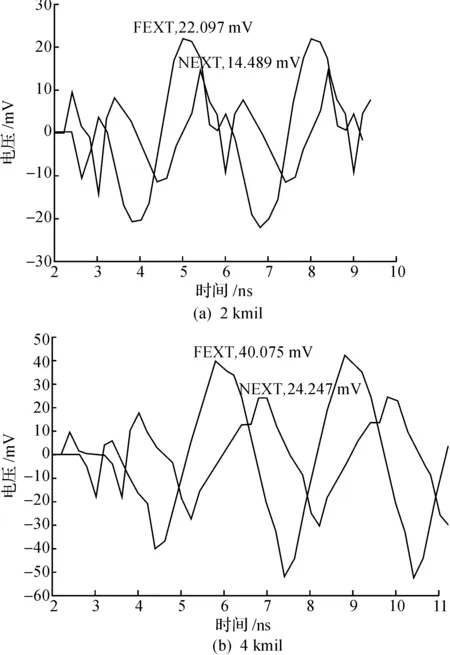

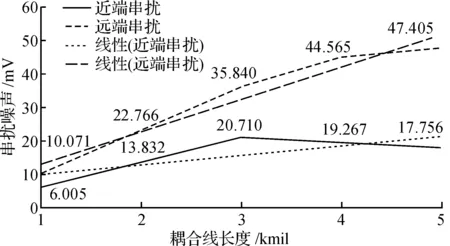

由式(2)可知:信号的耦合长度与传输线的远端串扰成正比关系,即耦合长度越长,传输线的远端串扰越严重.图2为耦合间距为10 mil情况下不同的耦合线长度的仿真结果,图3为串扰噪声与耦合线长度的关系曲线.

图2 耦合长度Fig.2 The coupling length

由图2可见:当线间距固定以后,串扰噪声与耦合线的长度为正比例关系.当信号的耦合线长度增加时,信号所受到的远端串扰总噪声急剧增加.图3表明串扰噪声在耦合线长度小于3 kmil时的值较小,当耦合长度达到3 kmil时,串扰噪声的值急剧增加.由式(2)可知:耦合线的长度对于远端串扰的影响较大,所以在满足设计条件的情况下,要尽量控制平行走线的长度,以此达到减小串扰噪声的目的.

图3 串扰噪声与耦合线长度关系曲线Fig.3 Crosstalk noise and coupling curve

3.3耦合线间距对串扰的影响

由式(1)可知:串扰噪声与互感和互容值的大小有关,而互感和互容值随着耦合线的间距增大而减小,故当其他条件不变时,串扰噪声与耦合间距有关.图4耦合线长度为3 000 mil时不同的耦合线间距的仿真结果,图5为串扰噪声与耦合线间距的关系曲线.

图4 耦合线间距Fig.4 The coupling line spacing

由图4可得:串扰噪声随着耦合线间距增大而减小,尤其对于远端串扰的影响是巨大的.在其他因素不变的条件下,耦合间距增大一倍,串扰幅值约减小一倍.减小串扰噪声的有效方法包含适当增大导线之间的间距,当导线之间的间距大于等于线宽的两倍时,可以保证达到最坏情况下的串扰噪声值控制在5%以下[10].由图5可得:当布线空间较小时,可以采用2 W原则,当耦合线间距满足2 W原则时,串扰的噪声下降较多,可以满足系统的设计要求.

图5 串扰噪声与耦合线间距关系曲线Fig.5 Crosstalk noise and coupling curve

3.4反射对串扰的影响

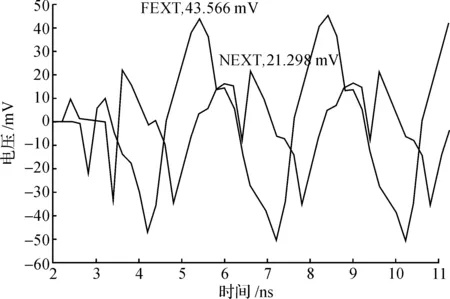

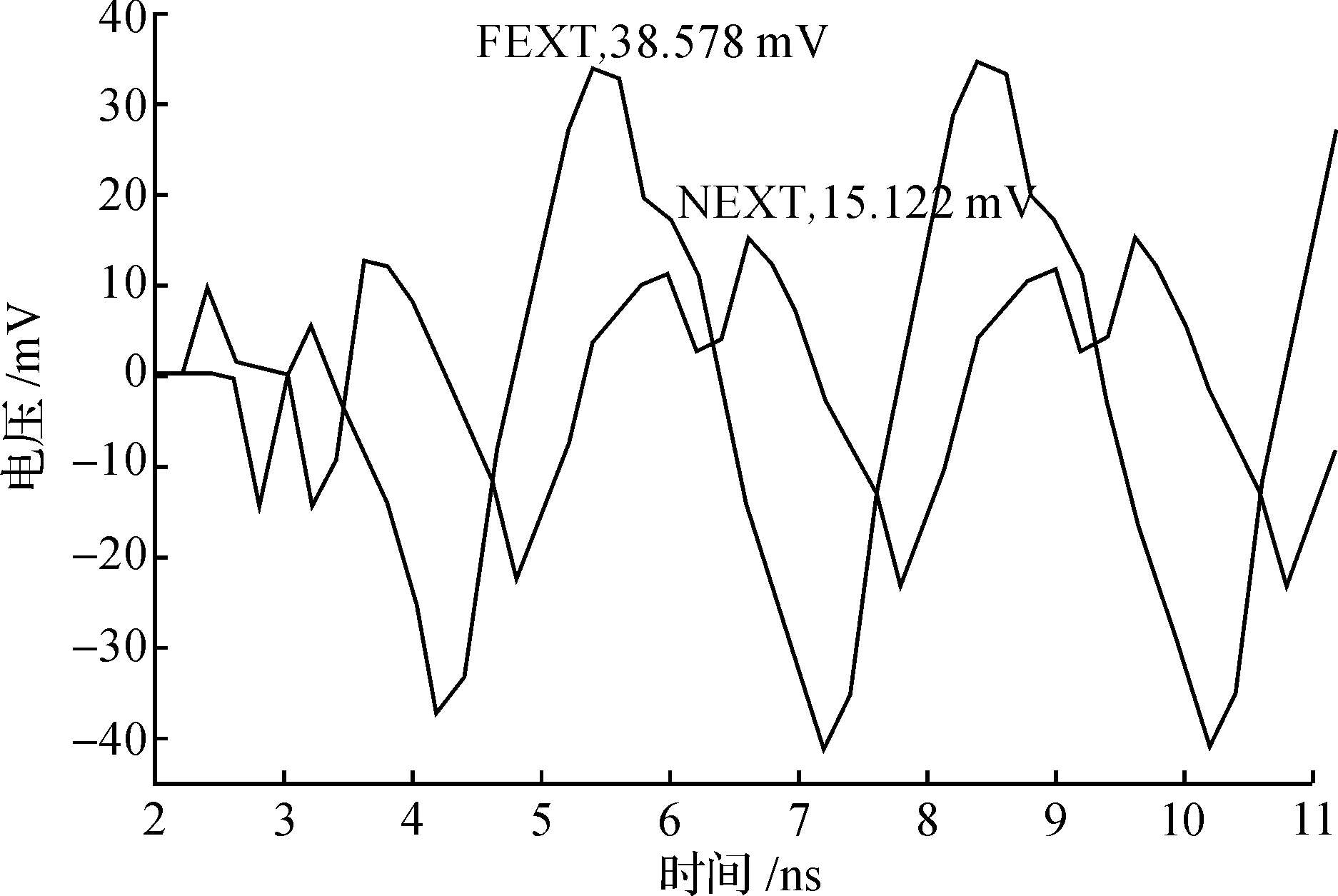

分别对于攻击线及受害线采取都未端接电阻、仅攻击线端接、仅受害线端接及攻击线和受害线都端接电阻的情况下进行仿真,研究反射对于串扰的影响,图6~8为不同端接情况下串扰噪声的仿真结果.

图6 都未端接Fig.6 All are without impedance matching

图7 被干扰源未端接Fig.7 Victim line without impedance matching

图8 全部串联60 Ω电阻Fig.8 All series 60 Ω resistance

由图6~8仿真结果可知:当未采取任何端接时,传输线上由于阻抗不匹配会引起反射问题,此时反射最大,串扰也是最大.当受害线与攻击线都端接时,传输线实现了阻抗匹配,此时反射最小,系统串扰最小.

4结论

对DDR2 SDRAM互连线之间的串扰问题进行研究,理论分析了一些参数对于串扰的影响,通过Cadence公司的SigXplorer仿真软件对PCB整板进行布线后仿真,根据仿真分析的结果可得减少串扰的一般规则:在布线空间允许的条件下,尽量加大相邻走线之间的线间距,减小平行走线的长度;相邻信号层的走线尽量垂直,以减小相邻层的耦合;加入端接匹配电阻可以减小串扰的幅度;减小信号层与电源层或地层之间的介质厚度可以有效减小串扰;布线空间允许的条件下,对于高速信号提供包地可以减小两条信号线间的耦合,进而减小串扰.

参考文献:

[1]李胜朝,张江鑫.高速电路中时序问题的分析和处理[J].浙江工业大学学报,2009,37(5):499-502.

[2]郭德亮,郭淑琴,鲍卫兵.基于突发光信号的高速数据采集系统的设计与研究[J].浙江工业大学学报,2010,38(1):46-48.

[3]张松松,刘飞飞.高速电路板级信号完整性设计[J].电子·电路,2013,26(10):105-109.

[4]田广锟,范如东.高速电路PCB设计与EMC技术分析[M].2版.北京:电子工业出版社,2008.

[5]李胜朝.基于Cadence的信号完整性设计及其在嵌入式系统中的应用[D].杭州:浙江工业大学,2009.

[6]DOUGLAS B. Signal integrity issues and printed circuit board design[M].刘雷波,赵岩,译.1版.北京:机械工业出版社,2005.

[7]STEPHEN H H,HOWARD L H. Advanced signal integrity for high-speed digital designs[M].张徐亮,鲍景富,张雅丽,等译.1版.北京:电子工业出版社,2011.

[8]安平凹,尹达一.CMV2000高速大面阵信号处理和完整性仿真分析[J].应用科技,2015,42(3):1-6.

[9]董辉,卢建刚,黄豪佑.Cadence高速PCB设计与仿真分析[M].5版.北京:北京航空航天大学出版社,2006.

[10]ERIC B. Signal Integrity:simplified[M].李玉山,李丽平,侯彦宾,等译.2版.北京:电子工业出版社,2005.

(责任编辑:刘岩)

Research and simulation of DDR2 crosstalk based on the Cadence

DONG Hui, MA Zujie

(College of Information Engineering, Zhejiang University of Technology, Hangzhou 310023, China)

Abstract:With the increase of the operating frequency and the signal edge conversion rate, the influence of crosstalk on signal integrity is becoming more and more prominent. Through the analysis of the formation mechanism of the transmission line crosstalk, the Cadence simulation software is used to simulate the crosstalk of DDR2 SDRAM in the system, It gives a reasonable solution to the problem of crosstalk process. Based on the simulation analysis of the near-end crosstalk and far-end crosstalk of the data line, it can be concluded that the influence of crosstalk on the electric circuit can be reduced through reducing the coupling line length, increasing the spacing of coupling line, and reducing reflection. At the end of this paper, some effective measures to restrain crosstalk in PCB design are proposed. It will have some guidance for the design of signal integrity of DDR2 SDRAM.

Keywords:crosstalk; near-end crosstalk; far-end crosstalk; coupling

收稿日期:2015-11-19

作者简介:董辉(1979—),男,浙江永康人,副教授,研究方向为嵌入式系统技术,E-mail:hdong@zjut.edu.cn.

中图分类号:TN972

文献标志码:A

文章编号:1006-4303(2016)03-0266-04