一种低成本纳卫星星载计算机容错方法

2016-06-01朱明俊周宇杰

朱明俊 周宇杰

(南京理工大学机械工程学院,南京 210094)

一种低成本纳卫星星载计算机容错方法

朱明俊 周宇杰

(南京理工大学机械工程学院,南京 210094)

为了提高纳卫星星载计算机系统的可靠性,减少体积、质量及功耗等多方面因素的影响,文章提出了一种软硬件结合的低成本容错设计方法。将星载计算机硬件采用双机冗余冷备份方案,通过现场可编程门阵列(FPGA)对故障处理器进行仲裁切换;软件容错通过错误检测与纠正(EDAC)信息容错技术的实现,对星载计算机整体程序进行纠错检错,以对抗单粒子翻转事件。结果表明:该方法能够对星载计算机系统进行有效的故障切换处理,并降低单粒子事件的不良影响,可以在纳卫星系统中推广应用。

纳卫星;双机冗余;仲裁器;错误检测与纠正

1 引言

近年来,纳卫星设计逐渐标准化,生产周期短、研制成本低成为微小卫星领域的研究热点[1-2]。随着空间任务对微纳卫星高性能需求的日益增强,现有的宇航级/883B级抗辐照电子元器件价格昂贵,批量小,制造周期长,集成性能升级慢,难以应付越来越复杂的空间任务需求。与此同时,高性能商用现货器件(COTS),包括工业级和商业级,在空间任务的应用日益增多。COTS器件既可满足空间系统性能不断提高的需求,也使得微纳卫星具有价格低、体积小、质量轻、功耗低的优势。同时,在轨试验证明,COTS器件辅以必要的防护和容错技术是完全可以经受住低轨道高能粒子辐照影响的[3]。

星载计算机作为卫星的核心部件之一,其高可靠性是保证卫星任务顺利完成的前提。由于采用了COTS器件,星载计算机的抗辐照能力低,产品不具有可追溯性,容易受太空辐射和单粒子效应影响而引发错误,产生不可估量的后果。为了对抗太空辐射对卫星电子器件的不良影响,并延长卫星的工作寿命,通常须要对卫星系统进行容错设计[4]。

本文针对纳卫星提出了一种软硬件结合的容错设计方法,硬件通过采用高性能COTS器件,高度集成在10cm×10cm的单块电路板中,实现双机冷备份容错,并通过错误检测与纠正(EDAC)软件技术对星载计算机代码进行纠错检错,以对抗器件发生单粒子翻转,提高星载计算机的可靠性。

2 系统容错设计

目前,对抗单粒子翻转有许多解决措施,如系统级冗余方法、抗辐射组件方法、软件容错方法等[5]。纳卫星作为一个微型化的平台,质量、功耗、空间资源等都受到制约。对星载计算机采取系统级冗余和抗辐照组件可以提高可靠性,但是会带来系统规模增加的问题,对纳卫星而言,并不是可行的方案。而随着集成电路技术的提高,COTS器件的功能不断增强,体积不断缩小,使得在同等大小的电路板中可以集成更多的器件。如果将系统级冗余进行改进,直接对星载计算机系统核心器件(如CPU,SRAM等)进行冗余,就能够实现在10cm×10cm的电路板中完成多个电路的冗余设计。

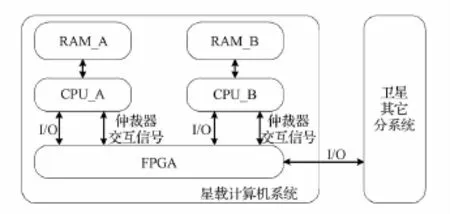

本文对纳卫星星载计算机系统的硬件采用双机冗余冷备份容错设计,硬件结构如图1所示。通过带有仲裁功能的FPGA在CPU出现故障时切换至备份CPU,可避免卫星任务中断。星载计算机系统的软件部分通过EDAC信息容错对抗太空辐射造成的单粒子事件,能够提高星载计算机系统软件的可靠性。

图1 星载计算机系统硬件结构框图Fig.1 Hardware structure block diagram of on-board computer system

3 双机冗余硬件设计

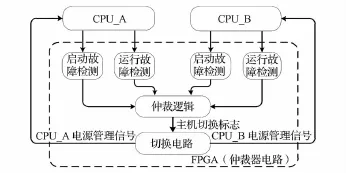

双机冗余容错系统功能结构如图2所示,虚线框部分为在FPGA内部实现的仲裁器电路。CPU_A和CPU_B是星载计算机系统软件运行的处理器芯片,采用冷备份的冗余方式。

仲裁器作为双机冷备份结构的核心,为了保证该电路的可靠性,可以选择反熔丝型FPGA或者对该部分电路采取三模冗余设计[4],本文重点在于介绍仲裁器电路的设计。

图2 双机冗余容错系统结构框图Fig.2 Dual redundant system structure diagram

3.1 仲裁器电路

仲裁器电路负责监测CPU的运行状态,在CPU状态异常时,切换至备份CPU。仲裁器电路内部结构分为4部分:启动故障检测模块、运行故障检测模块、仲裁逻辑模块和切换电路模块[6],所有模块通过硬件描述语言实现。

3.1.1 启动故障检测模块

CPU在启动过程中须要完成模块上电、内存初始化等工作,在启动时可能会出现电源故障或内存受到单粒子效应影响无法完成初始化的情况,从而导致CPU启动失败。启动故障检测模块对CPU启动状态进行监测,在故障发生时即时通知仲裁逻辑,对CPU进行切换处理。

CPU的启动流程如图3所示,CPU的启动故障检测主要分为两个部分:电源检测和初始化检测。启动故障检测模块首先等待来自切换电路模块的CPU_ON信号,通知CPU的电源模块上电处理。在电源模块正常启动后会发出POWER_GOOD信号,通知启动模块等待CPU初始化完成信号,否则启动模块直接发出START_ERR信号,并终止后续检测。若在规定时间内CPU发出INIT_DOWN信号,则认为CPU初始化成功,启动模块会发出START_OK信号,否则发出START_ERR信号。只有在CPU顺利初始化成功后,才发出IO_EN信号,允许CPU的信号对外输出。

3.1.2 运行故障检测模块

运行故障检测模块用来检测CPU的运行状态,采用“看门狗”机制实现。“看门狗”本质上是一个计数器,“喂狗”操作会使计数器清零,否则计数器计数到预定值会产生溢出标志,利用该标志可以响应预先设定的事件。

在星载计算机程序运行正常情况下,会周期性地发出“喂狗”信号WDG_FEED。如果程序发生异常,比如因单粒子事件导致程序跑飞,该周期信号便无法产生。当“看门狗”溢出标志发生时,该检测模块向仲裁逻辑模块发出WDG_IRQ信号,通知CPU运行故障情况。为了防止信号扰动产生误判断,可以设置“看门狗”溢出标志多次发生时再发出WDG_IRQ信号。

3.1.3 仲裁逻辑模块

仲裁逻辑模块是仲裁器的核心,完成双机冗余的故障切换策略,具体流程如图4所示。

仲裁逻辑接收启动故障检测模块和运行故障检测模块的状态输出。在启动过程中若出现故障则跳过运行故障检测,仲裁逻辑直接切换CPU。若在CPU运行过程中出现故障,仲裁逻辑同样进行CPU切换。在等待各检测模块的状态输出时,仲裁逻辑只对当前CPU的状态进行响应,以防止备份CPU产生误操作信号。

仲裁逻辑模块将切换CPU的标志发送至切换电路模块,由切换电路完成CPU的硬件切换工作。

3.1.4 切换电路模块

切换电路模块接收仲裁逻辑模块的CPU切换标志,负责给相应CPU的电源管理模块发送使能信号,并等待当前CPU启动完成时发出的START_OK信号。

CPU完成初始化需要一定时间,在初始化过程还有可能出现故障,产生错误的IO信号,因此在CPU正常启动之前须要关断当前CPU的IO信号输出,防止对卫星的其它系统产生误操作。在接收到START_OK信号后,即表明CPU启动正常,切换电路模块打开IO的输出使能,至此,CPU可与外界进行通信。

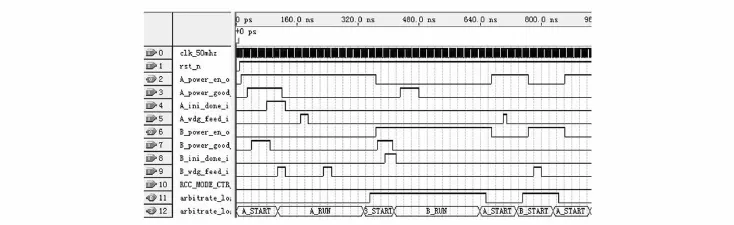

3.2 仲裁电路仿真

在Quartus II软件中实现仲裁器的逻辑功能,并得到图5所示的功能仿真。图5首先仿真了CPU_A的启动过程,根据启动流程可以看出CPU_A成功启动,由A_START进入了A_RUN状态,由于在运行过程中未能周期性地出现“喂狗”信号,因此仲裁器判断CPU_A出现了故障,从而切换至CPU_B启动过程,CPU_B启动与CPU_A相似。在CPU启动过程中未在相应时间内给出启动流程中各阶段所需信号,即判定启动失败,如图5后半部分仿真所示,仲裁器直接作出了切换处理。同时可以看出,当前CPU不会被另一CPU的信号干扰,仲裁器及时检测到了所有过程中的故障,并按照设定的切换策略进行故障处理,完成切换工作,满足双机冷备份的设计要求。

图5 仲裁器功能仿真图Fig.5 Function simulation diagram of the arbitrator

4 EDAC软件容错设计

单粒子事件对卫星存储器引起的故障是不可忽视的,严重时可导致卫星运行异常。星载计算机程序在随机存储器(RAM)中运行,该区域受到单粒子事件的影响较大,因此,对该区域必须采取一定的防护措施。

对抗单粒子事件中的单粒子翻转通常采用EDAC信息容错技术,可以通过增加外部硬件实现,也可以增加具有纠错检错功能的软件来实现。硬件EDAC方法会占用纳卫星有限的空间资源,增加卫星功耗,而软件EDAC技术只须要增加相应的程序。在美国的“先进研究和全球观测卫星”(ARGOS)项目的空间试验中,就使用了软件EDAC容错技术进行代码的检错纠错[7],可靠性虽然比硬件方案低,但是占用系统资源少,不增加硬件,实现灵活。本文采用软件实现EDAC的方法进行软件容错设计。

4.1 软件EDAC技术实现

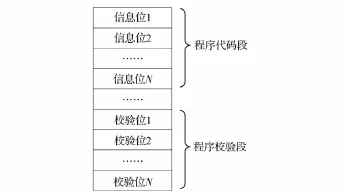

在星载计算机CPU上电之后,程序代码将从非易失存储器加载至程序存储区运行。程序运行时,数据段中存放的变量会不断变化,但是代码段是固定不变的,因此可以将代码段作为原始数据,进行EDAC编码,生成校验位,并另外开辟一段内存进行存储[8],程序代码段和校验段存放结构如图6所示。

本文采用(12,8)海明码[9],1字节的码字需要4个校验位。由于该码字较短,只存在256种情况,可以将校验码存放在常量表中,采取映射的方法产生校验码,该表作为常量存放在代码段中。

为了实现软件EDAC功能,本文将该纠错检错功能作为操作系统的一个进程。在CPU上电之后首次运行该进程时,先初始化校验位内存区,并对程序代码段进行EDAC编码存储,之后周期调用该进程。为了提高校验效率,在该进程周期调用时,将代码信息位再次生成校验位,与预存的校验位进行比较,若相同则认为该代码信息位和校验位未受到单粒子翻转的影响,若不同,则进行解码纠错,并回写正确的信息位和校验位。对于软件EDAC进程的优先级设置较高可以增强纠错效果,运行周期设置应当以不影响星载计算机系统功能为前提,在软件调试过程中不断提高该进程的运行周期直至符合系统运行要求。

单粒子效应如果出现在检验码常量表或EDAC相关程序段时,可能会造成EDAC功能发生错误,甚至可能误判断正确数据,造成严重后果。为了解决上述问题,文献[7]采用两个EDAC进程互相校验的方式保证进程的正确性,相比于上述做法,由于本设计所有的代码段都进行了EDAC的纠错检错,包括EDAC自身代码段以及检验码常量表,可认为该方法的检错纠错功能和结果都具有较高可信度,能够提高星载计算机的软件可靠性。因此,本设计的方法更加简单有效。

图6 软件EDAC存储区结构图Fig.6 Memory area structure diagram of software implemented EDAC

4.2 软件EDAC故障注入测试

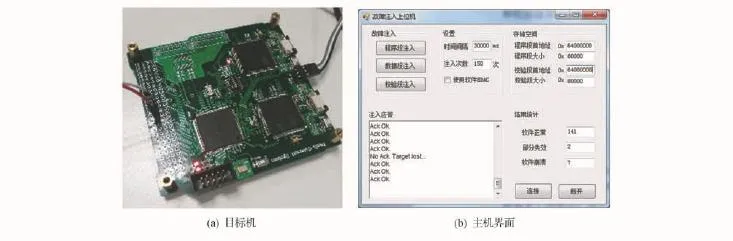

为了检验软件EDAC的可靠性,本文采用故障注入的方法,对软件EDAC的纠错性能进行测试。软件EDAC测试环境由目标机和主机构成,目标机为星载计算机原理样机,主机随机生成单粒子故障,并向目标机内存注入。

本文的EDAC方法仅针对程序代码段,为了模拟单粒子效应在内存中发生的随机性,验证增加软件EDAC功能后系统的抗单粒子效应能力,本次测试将针对整个内存区进行故障注入。在本文设计的目标机中,占用的内存有程序段、数据段和校验段,其余内存区因未使用故作不对星载计算机程序造成影响情况处理,测试过程如图7所示。

图7 软件EDAC测试Fig.7 Software implemented EDAC test

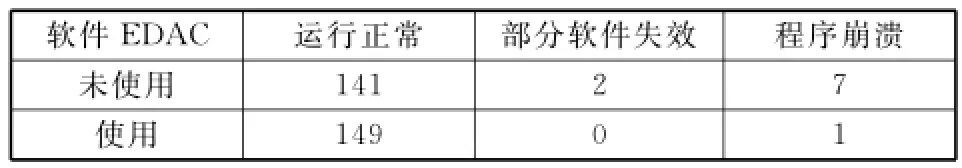

表1为增加软件EDAC功能前后的故障注入测试结果,故障注入150次,注入时间间隔为30s,其中的部分软件失效表示注入故障后程序中出现了错误,但是仍然能够继续运行未发生崩溃的情况。从相应结果可以看出,相比于未使用EDAC,星载计算机软件异常情况次数明显减少,而且能够纠正单粒子翻转错误位对软件带来的潜在威胁。由于软件EDAC比硬件EDAC实时性低,仍存在故障未能及时纠正而导致程序崩溃情况,但是总体上看还是具有较高的抗单粒子翻转能力。

表1 故障注入测试结果统计表Table 1 Fault injection test result statistics

5 结束语

本文提出的星载计算机的软硬件容错方法,具有高度集成化的特点,可以解决采用COTS器件后纳卫星星载计算机的低可靠性问题。仲裁电路的仿真结果表明:CPU出现故障后仲裁电路能够进行切换处理,软件EDAC故障试验验证了该方法对单粒子事件具有一定的容错能力,能够提高星载计算机系统的可靠性,但是存在实时性的问题,对纠错实时性要求严格的设计可以选择硬件EDAC方案。由于全部采用COTS器件,本文的设计方法成本低、可靠性高,在纳卫星领域将具有较好的应用前景。

(

)

[1]李军予,伍保峰,张晓敏.立方体纳卫星的发展及其启示[J].航天器工程,2012,21(3):80-87 Li Junyu,Wu Baofeng,Zhang Xiaomin.Development of CubeSat and its enlightenment[J].Spacecraft Engineering,2012,21(3):80-87(in Chinese)

[2]林来兴.立方体星的技术发展和应用前景[J].航天器工程,2013,22(3):90-98 Lin Laixing.Technology development and application prospects of CubeSat[J].Spacecraft Engineering,2013,22(3):90-98(in Chinese)

[3]付剑.星载计算机的硬件容错设计与可靠性分析[D].长沙:国防科学技术大学,2009 Fu Jian.Hardware fault tolerance design and reliability analysis of on-board computer[D].Changsha:National University of Defense Technology,2009(in Chinese)

[4]郭林.基于FPGA的星载机容错技术研究与设计[D].北京:清华大学,2009 Guo Lin.Studyand design on fault-tolerant system of satellite on-board computer based on FPGA[J].Beijing:Tsinghua University,2009(in Chinese)

[5]陈国林,孙义,章立生.基于uC/OS-Ⅱ的软件容错设计[J].计算机应用与软件,2007,24(7):1-2 Chen Guolin,Sun Yi,Zhang Lisheng.Design of fault-tolerant based on uC/OS-Ⅱ[J].Computer Applicantions and Software,2007,24(7):1-2(in Chinese)

[6]郭林,张涛,宋靖雁,等.基于FPGA的双机容错仲裁器研究与设计[J].微计算机信息,2010,26(14):113-115 Guo Lin,Zhang Tao,Song Jingyan,et al.Study and design of dual-computer fault-tolerant arbiter based on FPGA[J].Control &Automation,2010,26(14):113-115(in Chinese)

[7]Shirvani P P,Saxena N R,McCluskey E J.Software-implemented EDAC protection against SEUs[J].IEEE Transactions on Reliability,2000,49(3):273-284

[8]刘小汇,伍微,欧钢.软件错误检测与纠正技术可靠性研究[J].信号处理,2011,27(8):1140-1146 Liu Xiaohui,Wu Wei,Ou Gang.Study of the reliability for software-implemented EDAC technology[J].Signal Processing,2011,27(8):1140-1146(in Chinese)

[9]于海雯.海明码的原理及其构造方法[J].计算机与现代化,2001(2):148-150 Yu Haiwen.The R.Hamming Redundancy Code's theory and the method of construction[J].Computer and Modernization,2001(2):148-150(in Chinese)

(编辑:李多)

Method of Fault-tolerant On-board Computer for Low-cost Nano-satellite

ZHU Mingjun ZHOU Yujie

(School of Mechanical Engineering,Nanjing University of Science and Technology,Nanjing 210094,China)

The reliability design of the Nano-satellite has been restricted by volume,weight and power consumption.In order to improve the reliability of the computer system and reduce the influence of the above factors,a new low-cost method of combining software and hardware is presented in this paper.The system uses FPGA as an arbitrator to switch to the backup processor in case of failures.Fault-tolerant software is realized by software fault tolerance technology of the error detection and correction,to fight against single event upsets.Experimental analysis shows that the method can effectively handle failover for onboard computer system,reduce the adverse effects of single events,and can be widely applied to the system of Nano-satellite.

Nano-satellite;dual-computer redundancy;arbitrator;error detection and correction

V474

A

10.3969/j.issn.1673-8748.2016.02.009

2015-11-23;

2016-01-22

教育部科技发展中心博士点基金(20133219120030)

朱明俊,男,硕士研究生,从事立方星星载计算机容错系统研究。Email:zhumj1991@163.com。