基于FPGA多模时间同步触发系统的研究与设计

2016-05-25纪龙蛰邢园丁张继军

邹 虹,纪龙蛰,邢园丁,赵 艳,张继军

(西北核技术研究所,陕西 西安 710024)

基于FPGA多模时间同步触发系统的研究与设计

邹虹,纪龙蛰,邢园丁,赵艳,张继军

(西北核技术研究所,陕西 西安 710024)

摘要:分布式测试系统需要对不同基站的测试触发脉冲进行时间同步,利用卫星导航系统的授时功能可以实现高精度的时频校准和同步定时. 本文设计了由GPS/BD2双模接收机和本地高稳晶振组成的多模时间同步触发系统,用FPGA作为主控制器进行系统与上位机的数据通信和指令操作,完成了系统的硬件电路研制与用户界面编程,实现了对不同测试基站的高精度授时与同步脉冲触发功能.

关键词:分布式测试系统; 卫星授时; FPGA; 同步脉冲触发

0引言

分布式测试系统具有容错力强、 可靠性高、 安全性好等优点,广泛应用在爆炸探测、 卫星发射、 导航制导、 无线通信、 目标跟踪、 定位识别等领域. 在特殊的应用环境和测试范围下,为了使多个测试基站能够同步实时捕获到含有高频成分的动态被测信号,需要为各测试基站提供准确度较高的时间同步触发脉冲,以保证整个分布式测试系统协同可靠地工作[1-3].

利用卫星导航系统的精密授时功能完成地面站点的定时服务和时间同步已越来越多地应用在武器装备、 移动通信、 电力系统、 大地测量、 金融市场等国防建设和国民经济的各个方面,在时间基准和频率传递中发挥了重要的基础性作用[4-6].

本文采用GPS/BD2双模授时接收机和高稳恒温晶振作为本地时钟源的多模式组合方式,设计了基于FPGA的分布式测试时间同步触发系统. 系统中包含的GPS、 BD2和本地晶振3种授时信号源互为备份,统一驯服到与基准秒脉冲(1 PPS)上升沿对齐,为分布式测试系统中的各基站提供可控、 可测的高精度时间同步触发信号.

1系统原理与总体设计

1.1多模同步触发的基本原理

随着卫星导航技术的发展,用户终端的定位与授时精度越来越高,不同站点的接收机通过结算卫星发播的授时信号获得当前时间信息的误差通常可以控制在纳秒量级,可以满足一般的分布式测试系统对于时间同步的精度要求,各测试基站在配置导航授时接收机后就可以通过统一溯源的方式实现本地时钟的精准对齐[7,8].

在某些特定场合(如山洞、 隧道、 丛林、 深谷等),常因接收不到卫星信号而导致时间同步功能中断,为保证测试系统的精密守时,需要设置守时备份单元,并不断对其进行测试和校准,使得驯服后本地守时钟的输出信号与卫星钟的时刻精确对齐. 这个过程包括频率比对、 闭环控制、 相位差计算、 时间间隔测量等技术环节,经过校准的本地守时钟就可以作为导航卫星在一段时间内的替代者,完成对分布式测试系统各基站的时间同步触发功能[9,10].

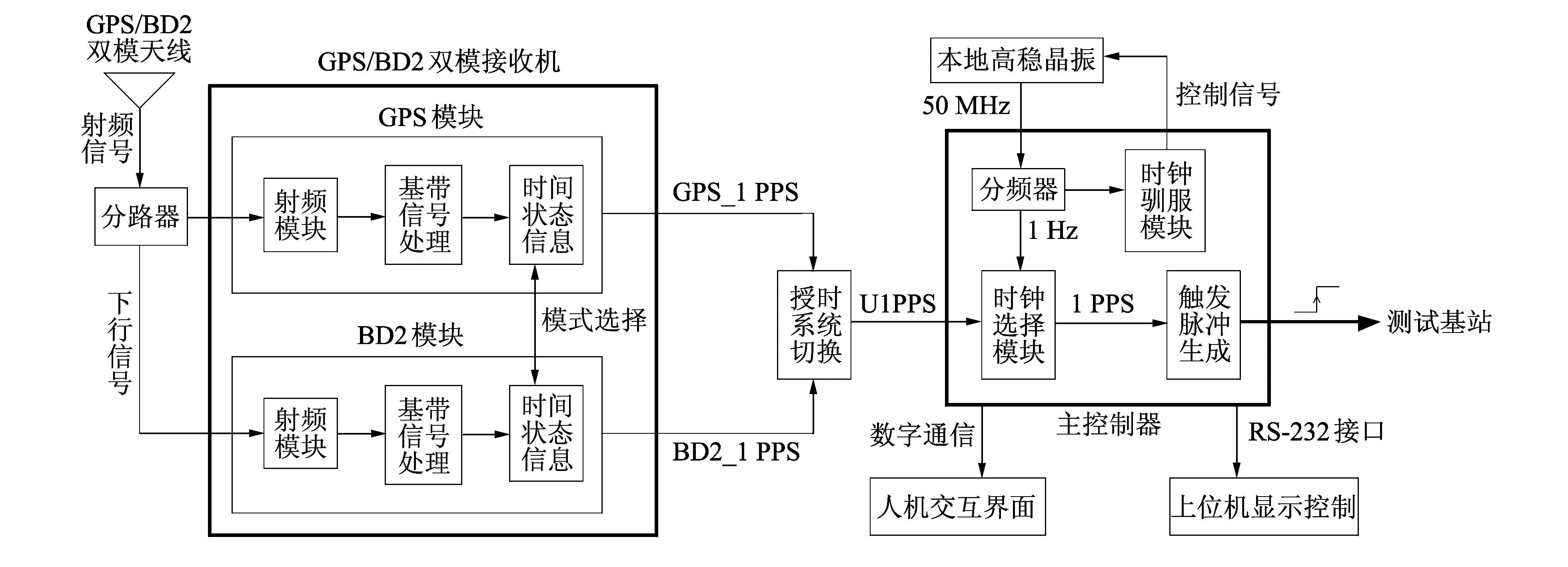

1.2系统总体方案设计

多模时间同步触发系统的总体方案设计如图1 所示.

图1 时间同步系统总体方案设计Fig.1 The scheme design of the time synchronization system

系统采用双模导航授时用户终端同时接收GPS系统和BD2系统的卫星信号,经过基带处理后输出两路秒脉冲信号GPS_1 PPS和BD2_1 PPS,均溯源到协调世界时(UTC). 主控制器同时采集经过优选后的秒脉冲信号U1PPS和经过晶振50 MHz输出分频后得到的OCXO_1 Hz时钟信号,利用时间间隔测量的方法比对二者之间的相位差,通过控制信号对晶振的压控调谐作用,逐步减小它们之间的差值. 经过闭环控制过程的不断校准和修正,最终使得卫星接收机输出的U1PPS和晶振输出的1 Hz时钟的上升沿对齐,再经过信号的调理和放大等后端处理环节生成可以用于分布式测试基站的触发脉冲,从而实现时间同步的目的[11].

整个时间同步触发系统中,来自导航卫星的基准时间作为授时钟使用,而系统的守时钟由本地高稳晶振和时钟驯服模块组成. GPS_1 PPS,BD2_1 PPS和OCXO_1 Hz时钟信号同时提供给测试系统,根据3者的时间精度设定优先级从高到低分别为: GPS_1 PPS≥BD2_1 PPS≥OCXO_1 Hz,当某一系统的授时信号出现较大偏差或者因测试环境条件限制而无法接收授时信号时,主控制器通过时钟选择模块自动切换到另一系统进行不间断授时,保证整个分布式测试系统的连续可靠运行[12].

在同步触发系统的总体方案设计中,主控制器通过RS-232或其它数字通信接口与上位机连接,在上位机的指令控制下进行数据传输和信息交换. 同步触发系统还应设置人机交互界面及配套的监视显示控制软件,以实现系统的高精度测试、 自动化运行和优化升级等功能.

2系统硬件设计

2.1器件选型

双模授时接收机选用芯星通公司的高性能SoC芯片UM220-T,它能够同时接收GPS的L1和BD2的B1两个频点的卫星信号,支持单系统独立使用和双系统联合使用两种工作方式,无需外接CPU即可直接输出标准NMEA 0183导航电文,具有3个RS-232串行通信接口,提供1个输出脉宽和极性均可调节的1 PPS秒脉冲信号.

主控制器选用Xilinx公司的Spartan 6系列FPGA芯片,它的内部存储资源丰富,具有高速的外部数据接口,可在Xilinx ISE 12.3开发平台通过VHDL或Verilog HDL两种硬件描述语言进行程序设计,完成对双模接收机输出信号的处理、 对本地晶振的实时校准以及同步触发时间的设定等功能.

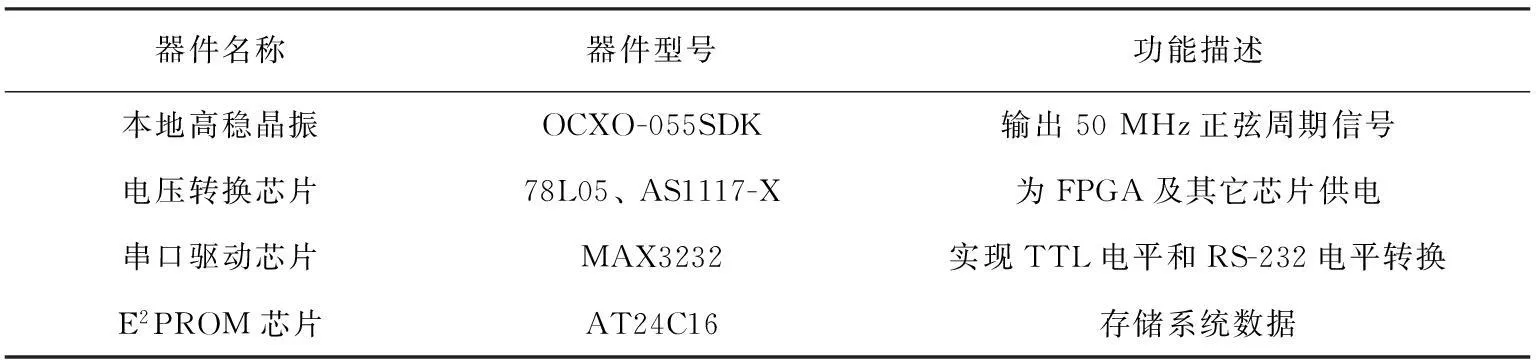

其它外设器件的选型及功能参见表1 所示.

表1 硬件系统中的器件选型

2.2硬件电路设计

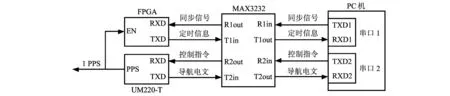

基于FPGA的多模同步触发系统的硬件电路组成如图2 所示(图中只显示授时模块、 FPGA,MAX3232等主要模块和芯片,其余外围芯片略去).

图2 同步触发系统硬件电路示意图Fig.2 The circuit diagram of the triggering system

在图2 中,同步触发系统各部分之间的硬件连接和工作过程为: 78L05芯片、 AS1117-3.3芯片和AS1117-1.2芯片分别将+12 V的系统输入电压转换为+5 V,+3.3 V和+1.2 V,提供给FPGA及其它外围芯片使用. 系统加电后,UM220-T模块通过2 491.75 MHz射频天线同时接收GPS系统和BD2系统的卫星导航授时信号,通过内部的RF输入匹配、 SAW滤波、 解扰解调、 数字基带处理等环节解算出标准格式的NMEA 0183导航电文,同时由数字通信接口将电文传输到FPGA中进行处理. FPGA接收到UM220-T的输出信号后,对电文内容进行分析,提取其中的时间、 经纬度、 定位精度及卫星数量、 编号、 载噪比等信息,恢复出卫星提供的协调世界时(UTC),并将其转换为标准北京时间(BJT). UM220-T通过PPS管脚将1PPS标准秒脉冲信号输出,该管脚由SMA射频信号线引出,作为频率测试参考信号直接使用,同时与FPGA的输入I/O口EN连接,作为计时同步信号对本地晶振的周期分频进行上升沿校准. MAX3232芯片实现TTL电平与RS-232电平的转换和串口驱动功能,将其T1in和R1out管脚分别与FPGA的TXD和RXD管脚相连,T1out和R1in管脚分别与计算机的RXD1和TXD1相连; 将其T2in和R2out管脚分别与UM220-T的TXD和RXD管脚相连,T2out和R2in管脚分别与计算机的RXD2和TXD2相连. UM220-T输出的导航电文通过RS-232串行通信接口输入到计算机中,作为显示控制软件的实时数据使用; 用户手动发送的导航模式切换、 启动方式选择等操作指令也通过RS-232接口发送到UM220-T中. FPGA中运行的VHDL程序通过JTAG下载器烧录,计算机中显示控制软件发送的定时、 计数、 触发信号和时间同步等信息通过RS-232接口输入到FPGA中进行数据处理.

3系统软件设计

双模接收机UM220-T输出的卫星电文格式是基于NMEA 0183通信协议产生的,该协议采用ASCII码进行数据传输,将位置、 速度、 时间等信息通过串行通信接口送至计算机中. 计算机通过RS-232接口与UM220-T模块进行数据通信,可以从NMEA消息语句中提取用户所需要的位置、 时间等信息,再将ASCII码表示的字符转换为图形或数字显示的形式,同时能够向UM220-T发送规定格式的指令进行模式设置、 配置信息查询等操作,这样便完成了测试与控制系统用户界面的设计.

3.1显示控制软件人机界面设计

上位机的显示控制软件是在Borland C++ Builder平台上利用C++语言编程并通过MSComm控件的串口通信功能来实现的. 串口调试完毕后,UM220-T模块输出的电文数据通过RS-232接口传输到计算机中,存储在输入输出缓冲区中等待读取命令; 接收完成后,计算机将这些信息与通信协议进行比对,提取出位置、 时间等参数信息.

图3 同步触发系统显示控制软件Fig.3 The consumer software of the triggering system

对各控件进行编程实现导航电文的数字化和图形化显示,时间同步触发系统的显示控制软件人机界面,如图3 所示,其中包括了当前北京时间、 用户所在经纬度、 定位有效标识、 定位精度因子、 解码后的导航电文等信息,另外可以通过相应按键发送指令进行导航模式、 启动方式、 串口参数的选择操作. 基于C++ Builder 和MSComm控件设计的该显示控制软件界面友好、 信息量充足、 测试精度高、 软件修改简便、 连续性与实时性强,利用图形和数码显示的方式进行数据处理分析具有更强的可读性和直观性.

在进行时间同步触发工作时,用户通过“开始时间”对触发脉冲发出的时刻进行设定(图3中的“开始时间: 16时52分20秒”),软件可以自动计算该时刻与当前时刻(图3中的“北京时间: 16时51分04秒”)的间隔(图3中的“剩余时间: 76秒”),当本地时间等于设定的“开始时间”时,系统通过硬件电路发出触发脉冲,驱动各基站设备进行同步测试. 软件系统在计算出时间间隔后,将其转换为16进制码(图中的“HEX码: 4C”)并通过RS-232接口将该数据传输到FPGA中,FPGA启动对晶振输出脉冲的分频计数和触发信号定时程序,即将50 MHz 分频为1 Hz后开始计时,当累积计到76 s时FPGA控制触发电平生成电路发出触发信号. 通过上述过程,系统即可实现由导航卫星和本地晶振相互备份进行定时的冗余功能,即便系统无法收到卫星发播的无线电信号,也不会因频率失锁造成计时的混乱,而是在检测到卫星信号丢失后自动切换授时模式,依靠经过驯服和校准后的本地晶振继续完成定时工作,这就达到了分布式测试系统“多模时间同步触发”的设计目的.

3.2本地守时晶振的驯服

通过VHDL语言编程实现对本地高稳晶振的驯服和校准. 当FPGA的EN端口检测到1 PPS的上升沿时,程序控制对晶振输出的50 MHz脉冲进行分频计数,通过设定计数器的初始赋值来改变分频后的周期与占空比(本系统设定的周期是1 s,占空比是50%),这样就可以达到晶振分频后输出的OCXO_1 Hz 脉冲与卫星时钟的1 PPS上升沿精确对齐,以实现对守时钟的驯服和校准.

上述驯服和校准过程并不是在主程序运行的整个阶段不间断进行的,而是根据系统对于同步触发精度的要求而定时工作的,这样每次校准后,都能够保证在后续的一段时间内分频得到的OCXO_1 Hz脉冲与1 PPS上升沿精确对齐,误差控制在很小的范围内,并且在下一次校准时将误差清零,重新开始分频计数,避免了由于晶振较差的长期稳定性或频率的漂移所造成的误差积累导致同步精度的逐渐降低.

4实验结果及分析

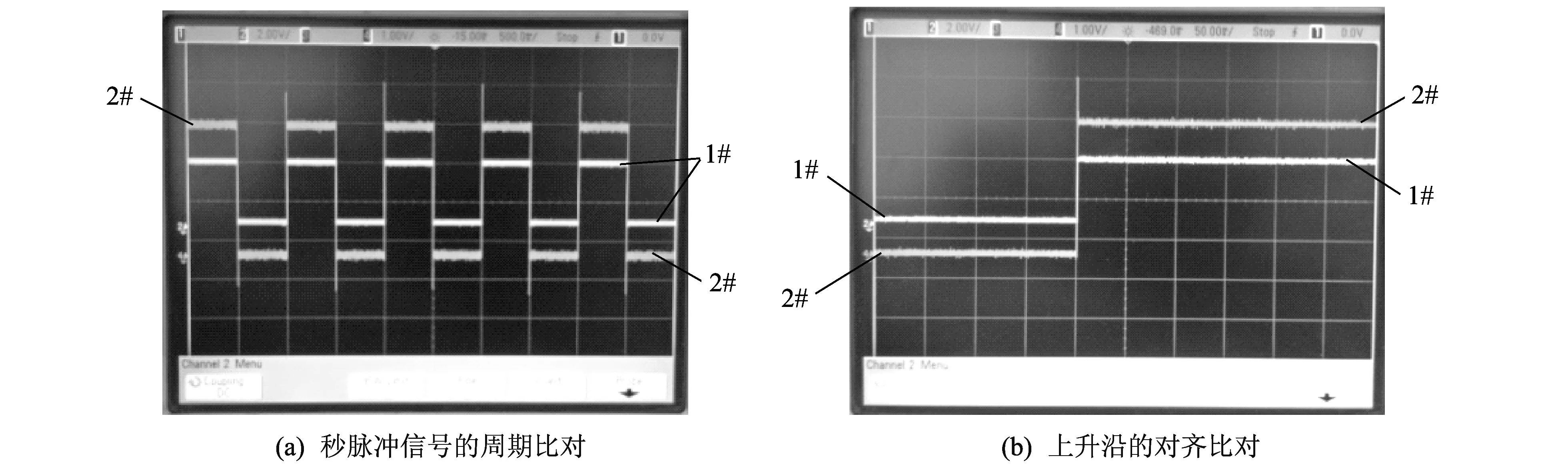

将本文中设计的两台多模同步触发系统(1#与2#)分别部署在两个测试基站进行实验,用示波器观察两路输出信号并进行上跳沿的比对,结果如图4 所示,其中1#曲线表示的测试通道所采集的是1#多模同步触发系统的输出信号,而2#曲线表示的测试通道所采集的是2#多模同步触发系统的输出信号.

图4 两台系统输出秒脉冲比对Fig.4 The output pulse contrast between two systems

从图4 中可以看出,两台多模同步触发系统均输出连续稳定的1 Hz周期信号,在每个计数周期内,信号的上升沿均可对齐,误差控制在5 μs以内,这样就保证了两个不同测试基站的多模同步触发系统的触发脉冲信号在时间和频率上的高度同步.

5结论

本文研制了基于FPGA作为主控制器的多模时间同步触发系统,完成了系统的硬件电路、 操作界面和程序代码的设计,通过接收GPS和BD2两个卫星导航系统发播的授时信号对本地守时钟进行校准,统一驯服到与1PPS上升沿对齐,利用卫星钟的授时信号和本地晶振的输出信号对触发脉冲的启动时间进行设定,其备份和冗余设计有利于在各种环境和试验条件下保证系统工作的连续性和可靠性. 经测试,通过实时校准,两台多模同步触发系统输出信号的同步误差控制在微秒量级,触发脉冲质量和系统连续运行时间均满足分布式测试系统对同步脉冲的精度要求.

参考文献:

[1]李卓,开百胜. 一种用于靶场多台站的时间同步电路设计[J]. 四川兵工学报,2014,35(2): 55-58.

Li Zhuo, Kai Baisheng. Design for multi-target station time synchronization circuit[J]. Sichuan Weapon Industry Journal, 2014, 35(2): 55-58. (in Chinese)

[2]张九宾,张丕状,杜坤坤. 无线分布式测试系统时间统一技术的研究[J]. 核电子学与探测技术,2010,30(3): 380-384.

Zhang Jiubin, Zhang Pizhuang, Du kunkun. The research of wireless distributional test system time synchronization technology[J]. Nuclear Electronics & Detection Technology, 2010, 30(3): 380-384. (in Chinese)

[3]刘洋. 分布式瞬态信号采集电路设计[D]. 太原: 中北大学,2013.

[4]马艳,叶玮. 分布式导弹测试系统设计[J]. 现代电子技术,2012,35(21): 41-44.

Ma Yan, Ye Wei. Design of distributed missile test system[J]. Modern Electronics Technique, 2012, 35(21): 41-44. (in Chinese)

[5]陈威,张丕状. 分布式测试系统同步时钟校准的频率测量方法[J]. 探测与控制学报,2009,31(5): 69-76.

Chen Wei, Zhang Pizhuang. Frequency measurement method of synchronization clock calibration in distributed testing system[J]. Journal of Detection & Control, 2009, 31(5): 69-76. (in Chinese)

[6]李本亮,王厚军,师奕兵. 基于PTP的无线分布式测试系统时钟同步研究[J]. 电子科技大学学报,2010,39(4): 556-559.

Li Benliang, Wang Houjun, Shi Yibing. Clock synchronization of wireless distributed measurement system based on PTP[J]. Journal of University of Electronic Science and Technology of China, 2010, 39(4): 556-559. (in Chinese)

[7]陈丕龙. 分布式测试系统中的GPS时钟同步系统设计[D]. 太原: 中北大学,2011.

[8]闫逢春. 分布式测试系统中GPS同步方案研究[J]. 电子测量,2013,1(2): 105-107.

Yan Fengchun. Research of GPS synchronous scheme on distributed testing system[J]. Electronic Test, 2013, 1(2): 105-107. (in Chinese)

[9]郭彬,单庆晓,肖昌炎. 电网时钟系统的北斗/GPS双模同步技术研究[J]. 计算机测量与控制,2011,19(1): 139-141.

Guo Bin, Shan Qingxiao, Xiao Changyan. A study of Bei-dou and GPS dual-mode synchronization technology for electric power system clock[J]. Computer Measurement & Control, 2011, 19(1): 139-141. (in Chinese)

[10]周大勇,刘鹏,刘树昌. BD2/GPS高精度同步时钟装置的设计与应用[J]. 吉林大学学报,2014,32(3): 262-266.

Zhou Dayong, Liu Peng, Liu Shuchang. Design and application of high-precion time synchronous device based on BD2/GPS[J]. Journal of Jilin University, 2014, 32(3): 262-266. (in Chinese)

[11]姚利红. 基于FPGA的电力系统GPS/北斗时间同步装置[D]. 济南: 山东大学,2013.

[12]王宽,粟欣,曾捷. 一种多体制通信时间同步算法及其FPGA实现[J]. 电子产品世界,2010,8: 37-42.

Wang Kuan, Su Xin, Zeng Jie. Timing synchronization algorithm for multimode communication and implementation in FPGA[J]. Electronic Equipment World, 2010, 8: 37-42. (in Chinese)

Research and Design of Multi-Mode Time Synchronization Triggering System Based on FPGA

ZOU Hong, JI Longzhe, XING Yuanding, ZHAO Yan, ZHANG Jijun

(Northwest Institute of Nuclear Technology, Xi’an 710024, China)

Abstract:It is needed to synchronize trigger pulses of different base stations in a distributed testing system. Utilizing the timing service of the satellite navigation systems can implement high precise time and frequency calibration. A multi-mode time synchronization triggering system which was made up of GPS/BD2 dual-mode receiver and local steady crystal oscillator was designed , and FPGA was used as the micro controller to complete the data communication and instruction operation between the system and computer , which achieved the devising of hardware circuits and user interface, realized thehigh precise timing and synchronize triggering functions among different testing base stations.

Key words:distributed testing system; satellite timing; FPGA; synchronized pulse triggering

中图分类号:TN919.6

文献标识码:A

doi:10.3969/j.issn.1671-7449.2016.02.004

作者简介:邹虹(1979-),女,工程师,硕士,主要从事信号与信息处理等研究.

收稿日期:2015-10-21

文章编号:1671-7449(2016)02-0114-06