一种无运放高电源抑制比的带隙基准设计

2016-05-19刘俐

刘 俐

(中国电子科技集团公司第58研究所,江苏无锡214035)

一种无运放高电源抑制比的带隙基准设计

刘俐

(中国电子科技集团公司第58研究所,江苏无锡214035)

摘要:为满足集成电路中高电源抑制比/低温度系数的要求,设计了一款没有运放的精简的带隙电压电路。相比传统有运放结构,电路芯片面积更小且具有更低的电流损耗。并在0.5 μm CMOS工艺下进行了仿真,仿真结果表明,在-40℃~+100℃温度范围内电路的温度系数为17×10(-6),电源抑制比PSRR在100 kHz以下达到-50 dB,在1 kHz以下能达到-80 dB,而整个电路在3.3 V电压下电流损耗仅为24 μA。

关键词:电源抑制比;带隙基准;PTAT;无运放;温度系数

1 引言

电压基准模块是模拟电路设计中不可或缺的一个基本单元,它为系统提供直流参考电压,并可通过电流镜像得到偏置电流。它的精确性、温度稳定性及抗噪能力决定了整个系统能否达到最佳性能。

随着集成电路技术的迅猛发展,低温度系数、高电源抑制比、低电源调整率、低压低功耗的带隙基准源的设计变得十分关键。传统带隙的基本原理是利用一个PTAT电压与PN结电压的负温度电压相补偿,其中为得到PTAT电流经常利用一个运放进行箝位,而运放的使用一方面会使得输出电压受到运放失调电压的影响,另一方面也会消耗更多的功耗[1]。

本文提出了一种无运放的高电源抑制比的带隙基准,对电路的工作原理进行了详细的分析和推导,并给出了电路中核心器件的参数设置。这种结构无运算放大器,避免了运放失调电压的影响,结构简单、占有芯片面积小、功耗低,可以广泛应用于各种集成电路中。

2与电源无关的PTAT设计

如果两个双极晶体管在不相等的电流密度下工作,那么它们的基极-发射极电压的差值就与绝对温度成正比[2]。假设两个不同大小的晶体管偏置的集电极电流相同,n为Q1和Q2的发射极面积之比,忽略它们的基极电流,则有:

如果设计IBE1=IBE2,并且IS2=8×IS1

因此,VBE的差值△VBE与绝对温度成正比,表达式中没有电源项,所以就得到了与电源无关的电压,此电压作用在阻值已知的电阻上就得到了与电源无关的PTAT电流。原理图如图1所示。

图1 与绝对温度成正比的电压产生原理图

但图1电路并不能实现R1电阻上的恒定压降,虽然MOS管M1和M2均工作在恒流源区,并且它们的沟道长度也较长(L=8 μm),消除了由于两MOS管的不同而产生的沟道长度调制效应,但是在R1上并没有得到恒定的压降。观测M1和M2的电流发现(见图2),M1的电流和M2的电流在VCC全电压范围以内并不能完全相等,尤其是VCC电压大于3 V以后。这是由于M2管的栅端被VBE1电压箝位,当VCC电压进一步上升时,M2管就工作在了线性区,电流随VCC上升的速率变慢,导致I1≠I2,破坏了设定的VBE1=VBE2的初始条件,所以在R1上并不能得到恒定的压降,无法实现PTAT电流。

图2 M1和M2的IDS电流

如何使M2不进入线性区成为需要克服的问题,所以M2管的栅极不能直接与Q1的基极相连。但是如果不相连又要保证Q1管的基极和集电极短接,保持Q1管的二极管特性,所以就需要使得Q1管的BC结“虚短”。Q1管的基极现在比“地”高一个VBE,如果再加上一路三极管Q3对地的通路,并且使得NPN管的发射极接地,Q3的基极和Q1的集电极相连,就可以实现Q1管的BC极虚短。根据原理图设计的可行的电路图见图3。

图3 根据原理图设计的可行的电路图

仿真结果如图4所示,从图中可以看出R1上的压降约为54 mV。

图4 PTAT电流随电源电压变化

3 与温度无关的基准设计

从上面的分析可知,Q1和Q2的发射极面积之比为8,电阻上的电压△VBE=VTln8,对正温度电压求温度的偏导数可得:

可以看出正温度系数与电源电压无关,只和温度成正比。

下面考虑负温度系数的产生。三极管的BE结就是一个天然的负温度系数电压,负温度电压温度系数为[2]:

其中m=-1.5,Eg=1.12 eV是硅的带隙能量,当VBE=750 mV、T=300 K时,∂VBE/∂T≈-1.5 mV/℃,考虑到其他因素,一般取∂VBE/∂T≈-2.2 mV/℃的经验值。并且VBE电压的温度系数本身与温度有关[2],因此如果正温度系数是一个固定值,与温度无关,那么在带隙电压基准中的温度补偿就会产生误差,减小此误差就需要设计高阶(比如二阶曲率)补偿。在一般的应用场合,一阶的补偿已经足够,为了减小二阶的误差,在R1的设计中需要考虑加入微调的修调电阻。

图3的线路结构并不能实现正温度系数电压和负温度系数的叠加,因为正负温度系数电压处于两个互不相干的支路中。考虑在Q1和Q2发射极的公共端串接一个电阻R2到地,就可以实现正负温度系数的叠加,如图5所示。

图5 增加了R2的电路图

通过该结构完成VBE和ΔVBE的加权相加,在输出端产生和温度无关的基准电压VBGP。

通过PMOS管电流镜M1、M2、M3的限制,使得IBE1=IBE2=IBE3=I,所以

由公式(3)得到VT的温度系数为mV/℃,VBE1的温度系数为-2.2 mV/℃,为了达到零温度系数,须满足:

所以取R2/R1=4,可以保证VBGP的温度系数为0。此条件下带隙电压的中心值为:

图6所示为输出电压VBGP随温度的变化情况,在电源电压为3.3 V的条件下,25℃时输出基准电压为1.2475 V,温度从-40℃~+100℃变化时,输出基准变化在1.4 mV左右,由此可算出基准电压的温度系数为17×10-6。

图6 带隙电压的温度特性

4 电源抑制比提高考虑

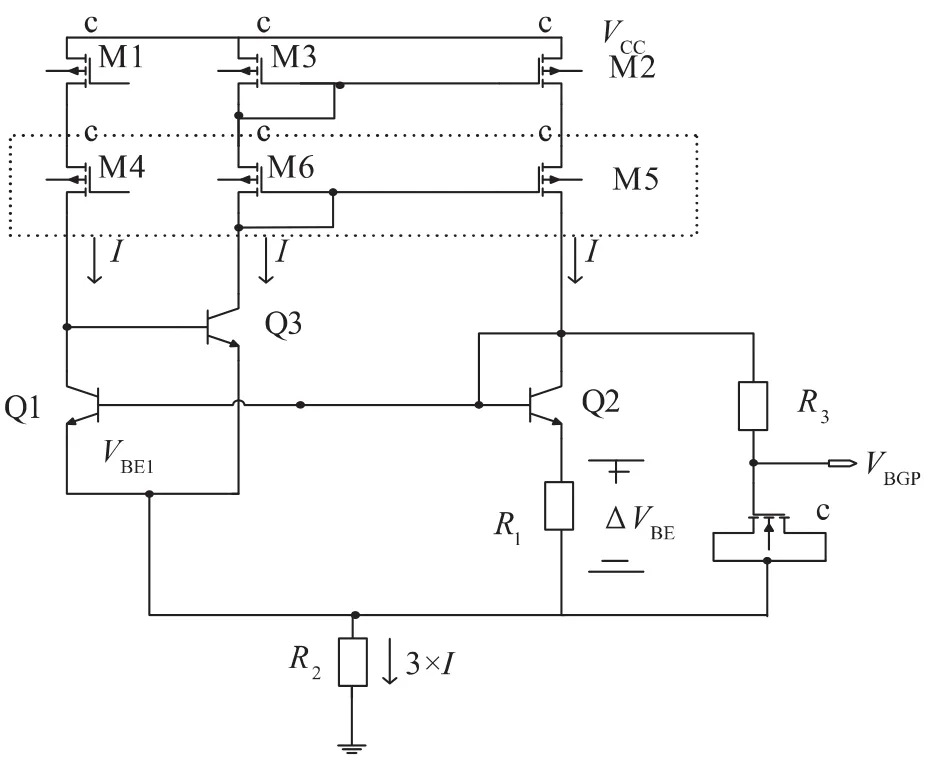

实际上电源抑制比考虑的是电源电压变化对输出基准电压的影响程度。由于电源抑制比和电源上叠加的交流频率相关,是频率的函数,所以主要考虑交流通路。电源到基准的交流小信号阻抗越大,同时基准对地的交流小信号阻抗越小,电源抑制比PSRR越大。降低输出节点到地的小信号电阻有两种方法,一种是增加对地并联支路数,另一种是增加对地单支路的电流。总之就是减小基准输出的对地阻抗,但这会造成静态功耗的增加。所以增加基准输出到电源的小信号电阻的方法是比较可行的,而共源共栅结构可以提高电源到基准电压的阻抗,从而提高PSRR[3]。增加了共源共栅结构的带隙电路图见图7。

有无共源共栅结构的PSRR性能对比图如图8所示,电源抑制比PSRR在100 kHz以下达到-50 dB,在1 kHz以下能达到-80 dB。增加了共源共栅结构,提高了带隙的启动电压,使带隙的启动点从1 V左右提高到了3 V,虽然带来了不利的影响,但PSRR的提高却是明显的。

尽管电源抑制比有所改进,但在1 kHz~1 MHz范围内产生了较大程度的减小,可能要通过其他诸如提高带隙基准的环路增益来提高电路在高频时的PSRR。

图7 增加了共源共栅结构的带隙电路

图8 有无共源共栅结构的PSRR性能对比

5 启动电路设计

为了使带隙电路能够稳定可靠地启动,需要设计一个启动电路来保证,启动电路的要求是:在电源电压较低、带隙电压还没有产生的时候给带隙核心电路注入电流,使核心电路能逐渐脱离零电流区并向稳定的工作点转移,同时也要保证带隙电压产生后能够自动断开与带隙核心电路的连接,并把静态电流消耗减小到0。

Istart电流加入点也要加以考虑,加入点选择Q3的基极。Q3的基极对地有直流通路,并且Q3的集电极对电源也有通路,能够使得带隙核心电路迅速进入直流工作点所确定的工作状态。

启动电路也需要设计反馈,在带隙核心电路工作以后能够将启动电路关断。反馈电压选择Q1的基极,也是带隙电压的产生点。当带隙电压逐渐建立时,反馈电压能将下拉到地的NMOS管M11逐渐开启,使得产生Istart的直流通路上的NMOS管M10逐渐关断,Istart电流对基准核心电路的注入逐渐减小,直至为0,启动结束。图9是完整的带隙电压产生电路。

图9 完整的带隙电压产生电路

6 版图实现与结果

在设计中保证Q1和Q2能流过适当的电流非常重要,从三极管的电流公式可以看出,两个NPN管的反向饱和电流之比为两个管子面积之比,因而其三极管的版图布局至关重要,为了增加版图的匹配性,将与M1串联的一个NPN管Q1放在中心位置,将与R1串联的8个并联的晶体管Q2放在四周,这样的布局可以让所有在外圈的管子在工艺和温度等效性上达到一致。如果面积允许,在所有三极管的外面再布上一圈配管,使得中心的1个管子和外面的8个管子在工艺上误差小。NPN管结构采用工艺线提供的发射区面积5 μm×5 μm标准版图,避免采用发射区面积过小的BJT,防止大的电流变化影响带隙的精准。

另外还要考虑电阻的冗余设计及布图方法。工艺上很难实现对电阻等无源器件绝对值的控制[4],利用版图的比例对称,成比例的电阻相对精度可以控制在10%以内,所以采用等比例复制及串并联的方法实现所需的阻值,降低工艺误差的影响。将较大尺寸的电阻分成若干个等长的电阻并联,然后使用叉指法放置,以实现严格的匹配。

本文设计的带隙基准源整体版图如图10所示,面积为120 μm×150 μm。

对所设计的基准电压源电路进行性能的后仿真分析。取环境温度为25℃,电源电压在1.8~5 V范围内变化时,输出基准电压的摆动仅为1.8 mV,说明电路具有良好的电源电压稳定性。对于不同工艺角,输出的基准电压变化较小,仍具有较高的温度稳定性。

图10 带隙基准版图

7 结论

本文设计了一款在3.3 V电压下工作的带隙基准电路,采用0.5 μm CMOS N阱工艺条件进行电路设计,在温度系数和电源抑制比方面进行了一些考虑,并使用Cadence Spectre工具进行了仿真验证,达到了较好的结果。仿真结果表明,它能很好地抑制电源电压和工艺参数的变化造成的基准电压漂移,并且其功耗很低,静态电流不超过24μA。电路在-40℃~+100℃温度范围内达到17×10-6的温度系数,电源抑制比PSRR在100 kHz以下达到-50 dB,在1 kHz以下能达到-80 dB。通过此基准进一步产生的其他基准电压和电流没有涉及。本文设计的带隙基准电路结构简单,由于减少了运放的使用,消除了运放失调电压对带隙精度的影响,具有较强的适应性,可应用于对功耗要求较高的电路中。

参考文献:

[1]胡养聪,等.一种无运放电流模式带隙基准设计[J].现代电子技术,2010, 4:19-22.

[2]毕查德·拉扎维.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2004.

[3]程春来,等.一种低压低功耗CMOS折叠-共源共栅运算放大器的设计[J].中国集成电路,2007,100:40-44.

[4] DAN Clein . CMOS IC Layout concepts,Methodologies, and tools[M].北京:电子工业出版社,2006.

刘俐(1974—),女,安徽淮北人,工程师,长期从事集成电路设计工作,负责过DSP及AD等多个模拟电路的设计研发。

Design of a High PSRR Bandgap Reference without Using an Opamp

LIU Li

(China Electronic Technology Group Corporation No.58 Institute,Wuxi 214035,China)

Abstract:In order to meet requirement of high PSRR,low temperature coefficient in the integrate circuit,a compact bandgap reference without op-amp is designed. The design can reduce power consumption and chip area. Under the condition of 0.5 μm CMOS technology, the simulation result shows that the temperature coefficient of the circuit is 17×10(-6)between the temperature range of -40℃~+100℃.PSRR is -50 dB at 100 kHz and -80 dB at 1 kHz. Its total consumption is only 24 μA with 3.3 V voltage supply.

Keywords:PSRR; bandgap reference; PTAT; without op-amp; temperature coefficient

作者简介:

收稿日期:2015-12-15

中图分类号:TN402

文献标识码:A

文章编号:1681-1070(2016)04-0024-05