一种基于Scanchain的Block RAM的MBIST设计方法

2016-05-19丛红艳张艳飞

丛红艳,闫 华,胡 凯,张艳飞

(无锡中微亿芯有限公司,江苏无锡214072)

一种基于Scanchain的Block RAM的MBIST设计方法

丛红艳,闫华,胡凯,张艳飞

(无锡中微亿芯有限公司,江苏无锡214072)

摘要:基于March C+算法,设计了一种基于Scan chain的Block RAM为测试对象的串/并行BIST电路。在电路内部自身生成测试向量,不需要外部施加激励,并依靠自身决定得到测试结果是否正确。该电路既可以有效对Block RAM进行准确校验和故障定位,又不会因BIST测试增加PAD的数量。最后,对设计方法结果进行了仿真验证。

关键字:MarchC+算法;BIST电路;故障定位

1 引言

FPGA电路测试中,测试激励的多种测试方法都有一定局限性,不能找出所有的故障,而且随着设计规模和设计难度的增加,FPGA电路中Block RAM (BRAM)模块在其中所占面积的比例也越来越大,使得FPGA可以存储越来越复杂的程序和数据,这种趋势不但增加软硬件协同设计的难度,在芯片的成品率控制和故障检测方面也引发了新的技术难题。因此,本文采用了一种基于Scan chain的内建自测试Memory bist测试方法,完成对BRAM模块故障的检测和定位。虽然Memory bist电路会占用芯片面积,但是可以有效缩短测试时间,在BRAM模块测试中起着很大的作用。

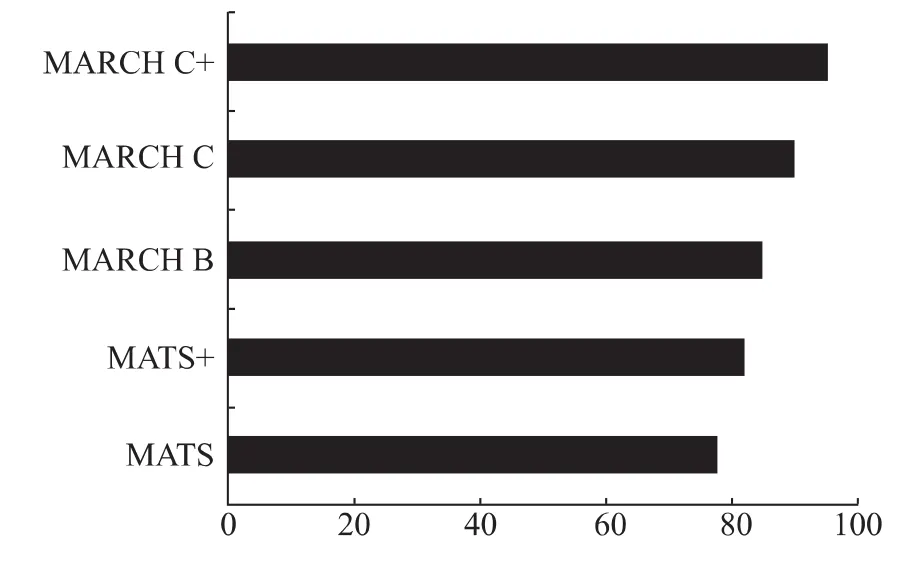

2 MBIST算法

目前,MBIST算法主要有5种,分别是MATS算法、MATS+算法、March B算法、March C算法、March C+算法。一般来说,没有一种算法是限于一种特定结构的,然而不同的算法却限定了不同的故障类型[1]。一方面,面向图形敏感故障而进行的周围数据扰乱和API测试,这些算法对实际故障覆盖率较低,而且测试时间很长。另一方面,面向耦合故障的算法可以提供出色的物理缺陷和实际故障覆盖率且耗时短,因此耦合故障是一种很好的故障模型。选择好故障模型,究竟采取哪种测试算法最能有效地检测出Block RAM中的故障,需要对上述5种算法的故障覆盖率做一个分析研究,如图1所示。

图1 各种算法的故障覆盖率

从图1可以看出,March C+算法故障覆盖率最高,是一种很好的存储器测试算法,因此根据Block RAM结构的故障类型来确定采用March C+算法。

采用基于March C+算法把整个测试分成6个阶段[2]:

(1)按照存储器地址升序对存储器每个地址位的存储空间写0操作;

(2)按照存储器地址升序对存储器每个地址位的存储空间读0写1读1操作;

(3)按照存储地址升序对存储器每个地址位的存储空间读1写0读0操作;

(4)按照存储器地址降序对存储器每个地址位的存储空间读0写1读1操作;

(5)按照存储器地址降序对存储器每个地址位的存储空间读1写0读0操作;

(6)按照存储器地址降序对存储器每个地址位的存储空间读0操作。

即可表示为:

(1)(写0)↑;

(2)(读0写1读1)↑;

(3)(读1写0读0)↑;

(4)(读0写1读1)↓;

(5)(读1写0读0)↓;

(6)(读0)↓。

由此可见,March C+算法是改进的March C算法,是对存储器单元按照地址升序或降序逐个向存储单元写入测试向量,同时将响应读出,这个算法的故障覆盖率高达95%,可以包括固定故障[3]、状态转换故障、寻址故障以及耦合故障[4]等。

3 MBIST设计与实现

18 kbit真双口BRAM采用基于SMIC 40 nm工艺的Artisan Memory Compiler软件编译产生。由Artisan Memory Compiler产生的1 k×18 bit的Memory称作BRAM18K,BRAM18K的Basic pins作为用户实现BRAM逻辑功能的pins脚,BRAM18K的BIST Multiplexor pins与Mbist模块连接关系如图2所示。

图2 Mbist模块与BRAM 1k×18模块端口对应关系

在整个Mbist模块电路中有4个外部输入信号。分别是b_te,b_rst_n,b_clk,ram_read_out[17:0]信号,其中b_te为Mbist测试使能信号,高电平有效,表示电路进入测试模式。b_rst_n为Mbist复位信号,低电平有效。输出信号为b_done,b_fail,b_done=1,表示测试已经完毕,b_fail=1表示发现数据错误,整个电路停止工作,b_fail=0表示芯片测试无错误。

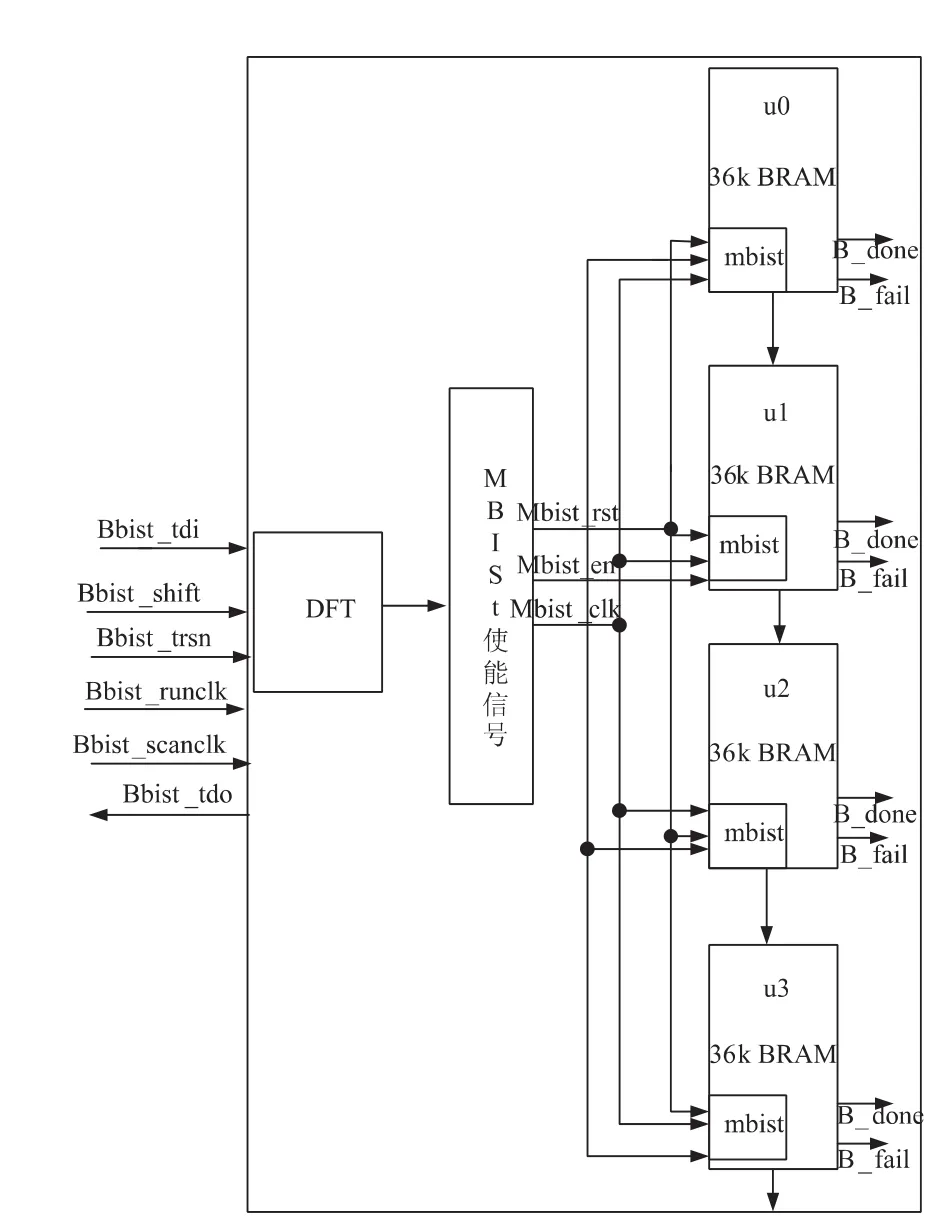

本设计中BRAM以36 kb为基本单元共用一个bist,144 kb串/并行测试,Bram1k×36支持A port bist功能,其简化关系如图3所示。

图3 Mbist模块与BRAM 1k×36模块简化对应关系

其中MBIST模块的test_ctrl_in信号来自Scan chain信号,各个Scan chain信号既可以串联成一个Scan chain,也可以并联起来,其串或并行测试的机理图如图4所示。

图4 Scan chain控制MBIST结构图

首先在Bbist_shift信号有效、Bbist_scanclk上升沿的条件下,数据由Bbist_tdi输入到Mbist使能模块中,产生Mbist测试使能信号Mbist_en,Mbist复位信号Mbist_rst,Mbist时钟信号Mbist_clk,控制一部分的Mbist工作,测试完成后结果由Bbist_tdo输出。本设计中BRAM以36 kb为基本单元共用一个bist,u0模块的输出信号bbist_tdo连接到u1模块的输入信号bbist_tdi,u1模块的输出信号bbist_tdo连接到u2模块的输入信号bbist_tdi,u3模块的输出信号bbist_tdo作为测试完成后的输出结果,最终可实现4个36 kb BRAM同时并行或串行测试。测试过程中,等待bist_done_u(0,1,2,3)=1信号时,bbist_shift信号拉低,如果bist_fail_u(0,1,2,3)=0,输出Test_pass_u(0,1,2,3)表示芯片测试无错误;否则,Test_fail_u(0,1,2,3)表示芯片测试发现数据错误。整个Memory BIST结构简单清楚,使用方便。

4 仿真验证

采用基于verilog行为级描述的RTL代码Bist_dp_Bram_1kX36.v,建立整个仿真验证环境,利用Cadence公司仿真工具NC进行设计仿真验证。其中图5为March C+算法,图6为Block RAM的MBIST设计结果。

从图5的仿真结果可以看出,March C+算法根据存储器的故障类型来确定算法,data_test [35:0]、ram_read_out[35:0]交替进行写0、写1、读0、读1操作。

图5 March C+算法

从图6的仿真结果可以看出,测试信号b_done=1表示测试结束,b_fail=0表示BRAM没有故障存在,整个设计是正确的。

图6 Block RAM的MBIST设计结果

5 小结

本文采用March C+算法应用于MBIST可以对双端口BRAM进行串或并行测试,且检测的速度很快,该BIST结构简单易用,不需要外部施加激励,并向系统返回测试结果,增加了整个测试的灵活性,能够满足大规模FPGA电路BRAM的测试需要,实现对BRAM的准确检测和故障定位,并且DC综合面积是36 kB BRAM面积的1%,并不影响整个芯片的面积,从而达到了预想的结果。

参考文献:

[1]申志飞,梅春雷.基于March C+改进算法的Mbist设计[D].合肥工业大学,2011.

[2]殷景华.基于March C+算法的存储器内建自测设计与仿真[D].哈尔滨理工大学,2009.

[3] PRINCE B. Semiconductor memories [M]. New York: John Wilry,1991.

[4] VAND G. Using march test to test SRAM [J]. IEEE Design &Test ,1993,10(1):8-14.

丛红艳(1983—),女,山东威海人,硕士,工程师,研究方向为千万门级FPGA设计与验证。

A Design of MBIST Based on Scan Chain Block RAM

CONG Hongyan, YAN Hua, HU Kai, ZHANG Yanfei

(East Technologies, Inc, Wuxi 214072, China)

Abstract:In the paper, the algorithm based on March C+ designing a serial/parallel BIST of Based onScan chain dual port Block RAM. The cirtuit generate the test vector, not require an external stimulus, and rely on their own decisions and get the test result is correct, the circuit notonly can be effective for BRAM accurately check and fault location, but also cannot increase the number of PAD. Finally, the paper show the system simulation.

Keywords:the algorithm based on March C+; BIST cirtuit; fault local

作者简介:

收稿日期:2016-1-28

中图分类号:TN402

文献标识码:A

文章编号:1681-1070(2016)04-0021-03