基于FPGA的铁路异物检测算法的硬件实现

2016-05-09余祖俊王中卫李长春

王 尧, 余祖俊, 王中卫, 李长春

(北京交通大学 机械与电子控制工程学院, 北京 100044)

随列车运行速度不断提高,对列车运行安全提出了更高的要求,开展铁路异物检测的研究对保证列车安全运行具有非常重要的意义。目前针对高速铁路中的异物侵限,国内外提出了很多的异物检测技术和方法[1-4]。异物侵限检测的方式可分为接触式和非接触式[5]。接触式检测主要采用防护网,通过检测导线判断防护网上是否有物体落入。该方式维护工作量大,需要申请天窗时间,效益较低。非接触式检测利用雷达、激光、红外和机器视觉等方式检测物体的位置和大小。机器视觉以其检测范围广、结构安装简单和准确性较高等特点十分适合铁路现场异物检测,通过采集视频图像进行图像处理,完成异物的检测、分类和跟踪。

目前,已经有研究者提出了一些基于图像处理的异物检测算法,这些算法通常是以视频分析中的前景提取算法为基础,并采用软件编程实现。部分算法可以实现较好的检测效果,在视频数据量较少的情况下,处理速度也可以接受,但在同时处理多路视频时,处理速度将大大下降。铁路异物检测系统在沿线安装了大量相机,通常可以包含上百个相机,如果所有相机的视频图像都集中到监控中心利用服务器软件进行处理,则需要较多数量的高性能服务器,硬件成本将非常巨大,且可靠性受到影响。若在每个相机端安装一台视频处理计算机,成本将更高。

因此本文提出基于现场可编程门阵列(FPGA)和ARM处理器的铁路异物检测硬件平台。该平台在相机端对视频进行处理,实现异物检测,将检测结果发生到监控中心,实现视频图像的分布式处理。该平台利用FPGA对图像进行处理检测可疑异物并提取异物特征,将可疑异物的特征发送给ARM,ARM利用模式识别方法对特征进行分类识别,确认异物并对异物进行分类。使得平台能够在较高的检测速度下,保证检测的准确性。该平台采用低成本的FPGA和ARM处理器,硬件成本较低,可以在前端大量安装。

由于FPGA的特点实现较为复杂的算法比较困难,因此应用FPGA进行异物检测的难点在于算法的硬件实现。近年来,运动目标检测与跟踪算法的硬件实现成为了研究热点[6-10],但存在算法实现复杂、资源占用大和实时性差等问题。文献[6]提出了一种运动目标的实时监测系统,利用运动目标分割和聚类背景更新模型提取运动目标,但背景更新复杂,影响处理速度。文献[7]提出了单次扫描连通域标记算法,设计单次扫描逻辑有效实现连通域合并和特征提取,光斑个数和面积计算正确,但数据表和标号合并表需要占用大量存储资源,对FPGA资源和时序要求较高。文献[8]提出了基于FPGA的连通域标记算法,借助数组将标记结果和参数合并存储,图像处理时间短,适合实时检测,但参数提取信息少,影响误警剔除效果,且不利于异物分类和跟踪。文献[9-10]提出了基于背景差分的目标位置质心计算的算法,去除中间结果的存储,图像处理速度快,精度和速度满足实时检测要求,但同样无法提取更多的异物特征参数。

针对现有运动目标检测的FPGA硬件实现方法的不足,本文提出基于FPGA的铁路异物检测及特征提取算法,并在搭建的异物检测平台上实现。利用背景差分法提取异物目标,并提出了简化的自适应背景更新模型完成背景的更新,结合文献[7]和文献[8]单次扫描连通域标记算法的设计,提出了存储多参数的二维数组结构,建立了基于异物几何特征的筛选机制完成误警的剔除,从而满足实时检测的要求,多参数的特征提取可用于异物的分类和跟踪。

1 铁路异物检测硬件平台结构

铁路异物检测硬件平台由CCD相机、视频输入处理器、SRAM(静态随机存储器)、FPGA和ARM等组成,见图1。

CCD相机和视频输入处理器完成图像的采集。CCD相机获取图像信息,输出模拟视频信号,经视频输入处理器采样、解码完成A/D转换,将数字视频信号送入FPGA处理。一帧数字视频信号为720×576 Byte、8位256阶灰度图像。此外,解码产生的视频同步信号同时提供给FPGA,从而完成视频有效像素的正确采集。

FPGA主要完成以下4个工作:(1)FPGA通过I2C总线初始化配置视频输入处理器控制CCD相机图像的采集;(2)FPGA产生地址信号和读写控制信号给外部SRAM,完成图像的存储与读取;(3)FPGA对采集的图像进行处理,提取异物的特征参数(质心坐标、面积、灰度平均值和外接矩形);(4)FPGA通过基于握手机制的通信协议将异物特征参数和图像数据传给ARM微处理器。

FPGA在整个硬件平台中起协处理器的作用,主要任务是对图像进行处理检测可疑异物并提取异物特征,将可疑异物的特征发送给ARM,而ARM处理器作为硬件平台的主控制器,主要负责高层图像处理ARM利用模式识别方法对特征进行分类识别,确认异物并对异物进行分类。同时ARM处理器还负责与远程服务器的通信以及对FPGA采集和处理的控制。本文主要说明FPGA实现异物检测与特征提取的方法。

2 异物检测算法

铁路异物检测硬件平台的异物检测算法流程图见图2。

算法的前半部分,即FPGA异物检测与特征提取由前景提取、背景更新、连通域标记、特征提取和异物的初步判断5部分组成,它是整个铁路异物检测算法的基础和关键技术。其检测结果和特征提取的准确性直接影响整个监测平台的检测结果。为满足这个检测平台运行速度的要求,FPGA异物检测算法需要有较高的检测速度,同时要保证较高的异物初步检测的准确性,并对外界环境(光照,动态背景等)的变化有较好的适应性,否则会加大ARM处理的负担,从而降低整体检测速度。另外为了提高ARM处理器对可以目标识别的准确性,FPGA需要同时、准确地提取可疑目标的多个特征,本文算法提取的特征包括:质心坐标、异物面积、灰度平均值和外接矩形。

前景提取过程利用背景差分法[11]通过设定灰度阈值,提取图像中的前景,并将图像进行二值化处理。假设背景帧像素为fb(x,y),当前帧像素为fc(x,y),二值化结果为fd(x,y),如果差分结果大于阈值T,则认定为前景点,否则为背景点,即

( 1 )

背景差分法的关键在于得到一个可靠的背景模型。根据背景差分结果将当前帧像素以一定比例的权重增加到背景像素灰中,即背景像素灰度值由原灰度值与当前帧像素的灰度值线性表示,完成背景的更新操作,从而解决光照、扰动等场景变化对背景模型的影响。情景模型为

( 2 )

式中:α为背景更新系数,根据经验和实际需要选取合适的值。

连通域标记算法[13-14]对图像进行一次从左至右、从上至下的扫描,对图像每一个像素进行标记,将同一目标的像素点标记成一个区域,标记为同一个标号的像素认定为连通的。本文采用的4连通算子见图3,当前像素C四连通域内上边像素A和左边像素B已经完成标记,当对C进行标记时,读取A和B的标记结果,根据设定的标记规则完成标记。

由于异物具有明显区别于其他误警物体的几何特征[15],所以提取了异物的多个几何特征,进而完成异物的初步判断。本文使用异物的面积大小S1、外接矩形面积大小S2、长宽比P和面积比Q等几何特征以及异物的平均灰度值G,设定经验阈值,剔除不符合要求的连通区域,见式( 3 )。如果经初步判断不存在异物,那么继续检测下一帧图像;否则,FPGA向ARM发出报警。

( 3 )

式中:xmin、xmax、ymin和ymax为外接矩形极值坐标;sumg为灰度值和,特征参数的临界值为经验阈值。满足条件的连通区域将作为目标异物并提取其特征参数,特征参数包括质心坐标、异物面积、灰度平均值和外接矩形。

其中算法的后半部分目标识别分类、目标跟踪和异物报警3部分由ARM处理器实现。FPGA发出报警后,ARM负责图像的高级处理。根据FPGA提取的特征参数,利用支持向量机SVM(Support Vector Machine)分类器完成目标识别分类,区分列车和异物;如果识别结果为正常行驶的列车,那么给FPGA发出继续检测下一帧图像的指令,否则利用卡尔曼滤波器进行目标跟踪,判断其是否侵限;如果异物进入了划定的警戒区域,那么判断为侵限异物,ARM通过以太网接口向服务器终端发出报警信息,否则给FPGA发出继续检测下一帧图像的指令。

3 算法的FPGA实现

FPGA异物检测算法硬件结构见图4,由5个功能模块组成:异物检测算法主控制器、SRAM读写控制模块、目标检测模块、连通域标记模块和异物特征提取控制模块组成。

3.1 目标检测模块

考虑到算法的硬件实现,本文背景差分法选用了固定阈值,根据目标和背景灰度值的差异完成图像二值化。该方法计算简单、运算效率较高、速度快,非常适合FPGA的实现。

背景差分模块设计1个8位减法器和和1个1位二进制比较器组成的组合逻辑,能完成背景差分和图像的二值化。为了提高检测系统处理速度,外部存储器采用了3块SRAM的存储结构,完成数据处理的乒乓操作,其中SRAM0存储背景帧,SRAM1和SRAM2存储相邻的两帧图像,见图5。当通过SRAM输入切换单元将采集的图像数据存入SRAM1时,通过SRAM输出切换单元读取SRAM2中的图像数据,并送入背景差分模块与SRAM0读取的背景帧图像进行差分运算。当SRAM2的图像处理完成,且SRAM1中图像数据写入完毕之后,SRAM输入切换单元再次切换,SRAM2存储下一帧图像,同时SRAM输出切换单元再次切换,读取SRAM1中的图像进行处理,如此周而复始,从而完成图像采集与图像处理并行完成的流水线结构。

根据式( 2 )的背景更新公式,设计两个8位乘法器和1个16位加法器组成的组合逻辑获得背景的更新值。由于α为小数,而Verilog硬件描述语言不支持小数数据类型,所以需要用特定的方法实现RTL设计中的小数运算。虽然小数的定点化表示会降低处理精度,但小数点位置固定,资源占用少且处理速度快。根据前期的算法仿真结果,小数的定点化处理精度可接受,算法性能满足要求,故选用定点小数。

考虑到灰度值为8位二进制数据,故小数的表示形式为〈8.8〉,即整数位数和小数位数都为8位,整数的表示形式为〈8.0〉,即整数位数为8位,小数位数为0位。由于并没有存储小数的位置信息,所以需要根据先前的约定对最后的结果进行截取,见式( 4 )。最后的运算结果为24位,低8位为小数部分,而利用Verilog的位操作运算截取中间8位即为更新后的灰度值。

〈8.8〉×〈8.0〉+〈8.8〉×〈8.0〉=〈16.8〉

( 4 )

3.2 连通域标记模块

考虑到硬件实现对于资源和速度的要求,本文采用了基于单次扫描的连通域标记算法,并在扫描过程中记录下目标的多个特征参数。见图4。连通域标记分为连通域标记主控制器、图像标记模块、参数存储模块、参数合并模块和参数压缩模块5部分。

3.2.1 图像标记

图像标记为每个像素标记标号,标号都是非负整数,背景像素标号为0。相同标号对应的像素属于同1个连通域,标记完成后把图像分割成不同区域。图像标记对1帧图像从左至右、从上至下逐像素扫描。

A和B寄存器存储当前像素邻域内的标号,行标号存储器用于存储上1行像素的所有标号,其地址为像素的列坐标。图像标记控制单元根据A和B寄存器的标号产生当前像素的标号和等价标号。令当前像素C的二值结果为BinC,标号为LC,等价标号为Ec,上边像素A标号为LA,左边像素B标号为LB,当前最大标号为N,标记规则如下

LC,Ec=

( 5 )

图像标记控制单元按上述规则完成标记后,由行列坐标发生器产生下一个像素的行列坐标值图像标记。而连通域标记控制器产生锁存信号,参数存储模块寄存产生的标号、等价标号和行列坐标,用于特征参数的存储。

3.2.2 参数存储

参数存储控制单元根据寄存的标号和等价标号以及二值化结果,读取存储器中的参数信息,更新参数信息并写回参数临时存储器中。本算法采用二维数组M[i][j]记录标号、等价关系和特征参数,即以标号作为列地址,每个列地址中又有9个行地址,每个行地址中存储一个参数,第0行存储等价关系,第1~8行分别存储x坐标和、y坐标和、面积、灰度值和、x坐标最小值、x坐标最大值、y坐标最小值和y坐标最大值。等价关系存储在双端口RAM中,8个特征参数存储在8个不同的单端口RAM中,RAM存储器初始值均为0。

参数更新过程为:如果当前像素二值结果为0,则不更新存储器;否则,以标号为地址读取单端口RAM中的特征参数,累加行列坐标更新x坐标和sumx、y坐标和sumx,累加像素个数sum、灰度值和sumg,比较x、y极值坐标和行列坐标更新x、y极值坐标xmin_0、xmax_0、ymin_0和ymax_0,更新式为

( 6 )

式中:L为标号;col为像素列坐标;line为像素行坐标;gray为像素灰度值;xmin_i、xmax_i、ymin_i和ymax_i为原x、y极值坐标。

同时,以标号和等价标号为地址读取双端口RAM中的等价关系,根据更新规则将参数更新到正确的地址中。更新规则如下:

(1) 如果等价标号为0,则确定以标号为地址读取的等价关系。如果等价关系为0,表示是新的区域,那么更新到以该标号为地址的双端口RAM中,此时x、y极值坐标更新为当前行、列坐标;否则更新到以该等价关系为地址的双端口RAM中。

(2) 如果等价标号不为0,则取以标号和等价标号为地址读出的两个等价关系中较小的值为地址更新参数。

更新过程需要两个时钟周期完成,第1个时钟周期读取参数信息,利用上述更新公式完成更新,第2个时钟周期将更新后的参数信息写到对应的RAM中。更新完成后,主控制器通过SRAM读写控制模块读取下一个像素进行处理。如果此时已经处理完整幅图像,那么主控制器产生开始信号使能参数合并模块,对参数临时存储器中的参数信息进行整理。

3.2.3 参数合并

参数存储完后,以不同的标号为地址中仍存储着同1区域的参数信息,因此需要根据双端口RAM中的等价关系对同1区域的不同部分进行合并,同时需要整理特征参数,完成合并操作,参数合并见图6。参数合并模块从地址1到最大标号N开始遍历二维数组M[i][j],重复执行L=M[0][L],直到M[0][L]=L,此时将执行操作前的特征参数与此时地址对应的单端口RAM中的特征参数进行合并,即更新属于同一连通区域的最小标号为地址的列,合并公式与更新公式类似,不再赘述。

3.2.4 参数压缩

虽然同一区域的特征参数已经存储在最小标号为地址的RAM中,但是RAM大量的地址中存储着合并前的参数信息。为了节约存储空间,需要对参数压缩存储,参数压缩见图6,参数压缩控制单元从地址1到最大标号N以自然数递增方式开始读取RAM中的等价关系,如果读出的数据(等价关系)与地址不一致,则处理下一个地址;否则,标记最终标号并利用除法运算计算质心坐标和灰度平均值,以该标号为地址将参数信息写入参数压缩存储器中。

令P[m][n]为最终的二维数组,如果符合上述情况,则P[0][n]执行操作

M[0][j]=j;P[0][Label]=j

( 7 )

式中:j为地址;Label代表最终的标号。

当处理一帧图像后,主控制器产生开始信号启动参数合并模块,即启动S0-S1-S2过程。当参数合并完成后,主控制器产生开始信号启动参数压缩模块,即S0-S1-S3过程。当参数压缩完成后,状态机回到初始状态S0。

3.3 异物特征提取控制模块

参数整理完成后,主控制器使能异物特征提取控制模块,进行异物的初步判断。该模块从地址1到最终最大标号以自然数递增方式读取参数压缩存储器,将参数送入由比较器组成的组合逻辑电路,剔除不符合的连通区域。异物特征提取过程与参数压缩同步进行。

在实际应用中,可以选择前文所述5个判断标准中的若干个组合作为筛选条件对异物进行初步判断。如果不存在异物,那么FPGA不发出报警信息,切换下一帧图像继续检测;如果存在异物,那么向ARM发出报警信息(中断信号),并等待ARM指令完成下一步操作。根据ARM指令的不同,FPGA将执行以下不同的操作:即只发送异物特征参数、只发送图像数据、发送异物特征参数和图像数据。FPGA与ARM完成数据传输后,等待ARM信号重新开始异物检测。

4 实验结果及分析

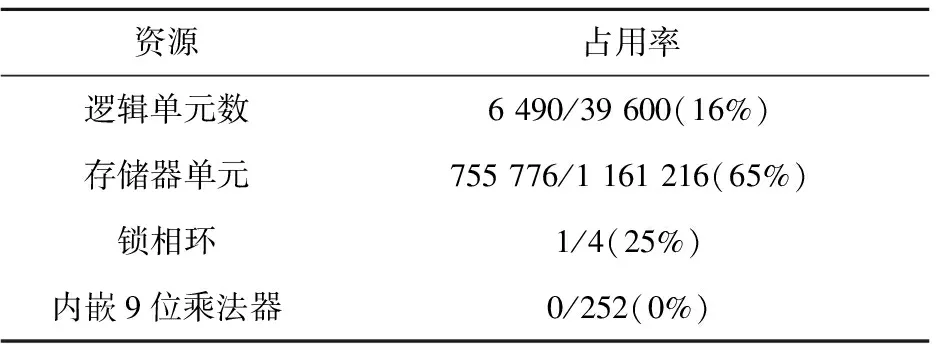

整个工程采用模块化设计,利用Verilog硬件描述语言编写,在Quartus II 11.1综合开发软件中完成编译,并在Modelsim中完成功能仿真,最后在铁路异物检测硬件平台上配置实现。FPGA芯片选用Altera公司的低成本FPGA系列Cyclone III,型号为EP3C40Q204C8,工作频率为50 MHz,处理的图像大小为720×576 byte,工程资源占用率见表1。

表1 资源占用率

可见,本文提出的硬件实现方法消耗的资源较少,可以采用低成本的FPGA芯片实现。降低了硬件处理平台的成本,为大批量安装提供了必要基础。

为验证异物检测算法的效果,在实验室室外进行了验证试验。图7为室外异物检测结果,从上到下、从左到右依次为背景帧、当前帧、标记外接矩形框的二值图像和异物的局部放大图。由图7可知,本文采用的异物检测算法有效的检测出了异物,并剔除了误警,实现了异物的初步判断。

另外,利用PC机上与硬件平台上完成通信,实时显示标记有外接矩形框的二值图像,并在工作空间里存储FPGA处理得到的异物特征参数信息和图像数据。利用Matlab编写验证程序,对获取的二值图像进行软件处理,并与硬件实现结果进行对比,以验证异物特征参数提取的正确性。

图7中,标记矩形框的目标视为异物,图中存在2个异物,假定二值图像中间的异物为异物1,右上角的异物为异物2。FPGA和Matlab处理结果对比见表2和表3,为了简化对比结果,选取外接矩形一组对角线端点坐标进行对比。

表2 异物1的 FPGA和Matlab处理结果对比

表3 异物2的 FPGA和Matlab处理结果对比

根据表2和表3的对比结果,对于异物的4项特征参数,本文采用的算法检测结果与Matlab处理结果基本一致,只有质心坐标和面积的计算存在极小的误差,质心坐标的相对误差均小于0.4%,面积的相对误差均小于2%,对后续ARM处理器的识别结果几乎不产生影响,满足实际应用要求。

在工作频率为50 MHz的条件下,FPGA的处理时间为45.8 ms,整个铁路异物检测平台的检测帧率达到15帧/s,满足铁路异物检测的要求。

为了进一步验证异物检测算法的效果和可行性,在北京北站铁路沿线进行了现场试验。现场试验环境较实验室环境更为复杂,光照变化较大,且由于大风等天气因素影响,容易出现误检的情况。图8为现场试验选取的背景。

由于正常行驶的列车和行人等其他异物都有可能被初步判断为异物,进而需要ARM完成异物的识别,现场试验时分别选取了异物为列车和行人的检测结果,见图9。图9(b)为列车的检测结果,图9(d)为行人的检测结果。

由现场试验结果看出,本文算法有效检测出进入铁路现场的异物,异物的初步判断准确。虽然试验现场光照条件多变,但从检测结果可知,算法有效消除了光线变化对试验的影响。此外,算法剔除了图9(a)中存在的误警,说明基于异物几何特征的筛选机制准确可靠。异物的多参数提取可用于异物的识别、分类和跟踪,从而区分正常行驶的列车和侵限异物,完成异物检测的报警。现场试验提取的异物特征参数见表4。

表4 现场试验提取的异物特征参数

5 结束语

本文提出了一种基于FPGA的铁路异物检测算法。该算法利用背景差分法提取异物目标,通过改进的单次扫描连通域标记完成连通域的提取,并记录异物的多个特征参数,最后根据基于异物几何特征的筛选机制完成异物的初步判断。

利用上述算法的铁路异物检测硬件平台首先在实验室室外进行了验证试验,验证了异物特征参数提取的正确性和异物检测的实时性。最后在铁路沿线进行了现场试验,能够有效检测异物,参数提取正确,但速度比软件算法快大约1倍,可以满足实时检测的要求。而使用的FPGA资源适中,能在中低密度的FPGA上实现。此外,多参数的提取可用于异物的分类和跟踪。

本文对算法进行了如下简化和修改:背景差分的阈值是根据经验设定的固定值;背景更新中的更新系数进行了小数的定点化操作;没有设计形态学处理的模块,对差分得到的二值图像缺少腐蚀和膨胀操作,影响连通域的标记结果;将传统的连通域标记算法的2次扫描改为1次扫描,并在扫描的同时记录多个特征参数。基于以上原因,本算法的运算准确度和精度都要低于软件,因此FPGA的实现性能有所下降。

参考文献:

[1] 王彤,史宏,王前,等. 客运专线异物侵限监控系统技术的研究[J].铁路计算机应用,2009,18(7): 8-10.

WANG Tong,SHI Hong,WANG Qian,et al. Research on Intrusion Monitoring System for PDL[J]. Railway ComputerApplication,2009,18(7): 8-10.

[2] NARAYANAN A H,BRENNAN P,BENJAMIN R,et al. Railway Level Crossing Obstruction Detection Using MIMO Radar[C]//Proceedings of European Radar Conference (EuRAD).Pairs: EuRAD,2011:57-60.

[3] MIYAYAMA H,OHYA T,KATORI T,et al. Obstacle Recognition From Forward View Images from Trams[C]//Proceedings of the 11thInternational Conference on Computer System Design and Operation in the Railway and other Transit Systems.Toledo Spain: Wessex Institute Technology,2008:617-627.

[4] 董宏辉,葛大伟,秦勇,等. 基于智能视频分析的铁路入侵检测技术研究[J].中国铁道科学,2010,31(2):121-125.

DONG Honghui,GE Dawei,QIN Yong,et al. Research on Railway Invasion Detection Technology Based on Intelligent Video Analysis[J]. China Railway Science,2010,31(2): 121-125.

[5] 郭保青,朱力强,史红梅. 基于快速DBSCAN聚类的铁路异物侵限检测算法[J]. 仪器仪表学报,2012,33(2):241-247.

GUO Baoqing,ZHU Liqiang,SHI Hongmei. Intrusion Detection Algorithm for Railway Clearance with Rapid DBSCAN Clustering[J]. Chinese Journal of Scientific Instrument,2012,33(2): 241-247.

[6] KRYJAK T,KOMORKIEWICZ M,GORGON M. Real-time Moving Object Detection for Video Surveillance System in FPGA[C]//Proceedings of IEEE 2011 International Conference on Design and Architectures for Signal and Image Processing. New York: IEEE,2011:1-8.

[7] JOHNSTON C T,BAILEY D G. FPGA Implementation of a Single Pass Connected Components Algorithm[C]//Proceedings of the 4th IEEE International Symposium on Electronic Design,Test and Applications.New York: IEEE,2008: 228-231.

[8] 谭许彬,谢宜壮,陈禾,等. 基于FPGA的连通域标记设计与实现[J].信号处理,2011,27(11):1 729-1 733.

TAN Xubin,XIE Yizhuang,CHEN He,et al. Design and Implementation of the Connected Component Labeling Based on FPGA[J]. Signal Processing,2011,27(11):1 729-1 733.

[9] 余祖俊,王尧,朱力强,等. 多光点位置实时检测系统及其应用[J].控制理论与应用,2012,29(12):1 537-1 542.

YU Zujun,WANG Yao,ZHU Liqiang,et al. Real-time Measurement System for Central Positions of Multiple Light Spots and Its Application[J]. Control Theory & Applications,2012,29(12):1 537-1 542.

[10] SANCHEZ-FERREIRA C,MORI J Y,LLANOS C H. Background Subtraction Algorithm for Moving Object DETECTION IN FPGA[C]//Proceedings of 2012 VIII Southern Conference on Programmable Logic (SPL). New York:IEEE,2012:1-6.

[11] 孙猛,袁小龙,王丽红. 基于FPGA的混合高斯背景建模实现[J]. 电子技术应用,2011,37(9): 60-63.

SUN Meng,YUAN Xiaolong,WANG Lihong,et al. Implementation of Real-time Gaussian Mixture Models Based on FPGA[J]. Application of Electronic Technique,2011,37(9): 60-63.

[12] 桑红石,傅勇,张天序,等. 一种适合硬件实现的多值图像连通域标记算法[J].华中科技大学学报(自然科学版),2005,33(9): 1-4.

SANG Hongshi,FU Yong,ZHANG Tianxu,et al. A Connected Components Labeling Algorithm for Multi-value Image that Suitable for Realization in VLSI[J]. Journal of Huazhong University of Science and Technology:Nature Science Edition,2005,33(9):1-4.

[13] 马益杭,占利军,谢传节,等. 连通域标记算法的并行化研究[J].地理与地理信息科学,2013,29(4): 67-71.

MA Yihang,ZHAN Lijun,XIE Chuanjie,et al. Parallelization of Connected Component Labeling Algorithm[J]. Geography and Geo-Information Science,2013,29(4): 67-71.

[14] 龚志成,曾惠翼,裴继红. 基于邻域分析的海洋遥感图像舰船检测方法[J].深圳大学学报理工版,2013,30(6): 584-591.

GONG Zhicheng,ZENG Huiyi,PEI Jihong. A Method for Ship Detection Based on Neighborhood Characteristics in Remote Sensing Image[J]. Shenzhen University Science and Engineering,2013,30(6): 584-591.