一种片上低触发电压高耐压NMOS ESD防护结构设计*

2016-04-25陈迪平陈思园

陈迪平,刘 杏,何 龙,陈思园

(湖南大学 物理与微电子科学学院,湖南 长沙 410082)

一种片上低触发电压高耐压NMOS ESD防护结构设计*

陈迪平†,刘杏,何龙,陈思园

(湖南大学 物理与微电子科学学院,湖南 长沙410082)

摘要:设计了一种触发电压低于10 V,HBM耐压超过4 kV的低触发、高耐压NMOS ESD防护结构.通过带钳位的栅耦合RC网络来适当抬升ESD泄放管栅压与衬底电压.在提高泄放能力与降低触发电压的同时,依然保持了较高的二次击穿电流It,从而增强了MOS防护结构在深亚微米CMOS电路中的ESD防护能力.该结构最终在CSMC HJ018工艺流片,并通过TLP测试平台测得触发电压低于10 V,二次击穿电流3.5 A,达到设计要求.

关键词:ESD;衬底触发;栅耦合;TLP

随着CMOS工艺技术的发展进入到深亚微米阶段,片上ESD防护设计已成为集成IC可靠性设计的关键.一般民用HBM耐压标准为2 kV,测试电压抬升率为2 kV/10 ns.军用HBM耐压标准参照美军军标MIL-STD-883Gmethod 3015.7,HBM耐压标准为4 kV以上,测试电压抬升率4 kV/10 ns.[1]深亚微米工艺下器件耐压能力的降低,向设计高ESD防护能力器件提出了挑战.本文旨在设计一种触发电压低于10 V,HBM耐压达到军用标准的MOS ESD防护器件.

GGMOS防护器件由于和COMS工艺兼容,设计简单,可移植性强,已成为目前通用集成电路中最常用的ESD防护器件.随着集成电路工艺技术不断发展,器件特征尺寸不断缩小,金属氧化物半导体的栅氧厚度越来越薄,晶体管耐压能力降低,对片上ESD防护结构也提出了更低触发电压的要求.典型GCMOS单元采用栅耦合电容技术可降低典型GGMOS触发电压,提高泄放能力.但随着栅耦合电压的提高,典型MOS防护器件的耐压能力降低[2],因此,同时达到高耐压等级与低触发电压成为典型MOS ESD防护结构设计中一大难题.文献[3-4]研究表明,对GGMOS结构衬底端进行电流注入能在降低其触发电压的同时提高其二次击穿电流It.本文所设计结构在此基础上,同时利用栅耦合电容技术,设计栅电压控制模块,减小栅电压对MOS管耐压能力的影响,在降低了GGMOS结构触发电压的同时,保证了该结构的高耐压能力,完成了一种改进型片上低触发电压高耐压NMOS ESD防护结构的设计.

1低触发、高耐压NMOS ESD防护结构原理分析

1.1结构分析

图1为柯明道教授等人利用衬底触发技术于2003年提出的ESD泄放结构“衬底触发GGMOS”剖面图[3].采用对MOS晶体管回滞击穿的泄放机制,泄放电流主要为体电流i1与i2.[5-6]

图1 衬底触发GGMOS剖面结构图

该结构利用电容耦合ESD电压信号抬升主泄放管MN2/MN3衬底电位,对衬底注入电流i0与i3,同时MN2/MN3栅极接地,使其在正常工作时关闭,防止漏电.研究发现,随着注入电流的增加,二次击穿电流It也得到相应提升.[4]

该结构主要泄放机制仍然为击穿主泄放管MN2/MN3漏极与衬底间PN结,因而典型工艺下触发电压较高,且通过衬底的泄放能力有限.为了取

得更低触发电压、更高泄放能力的MOS泄放结构,本文在此结构的基础上,将原本接地的主泄放管栅端接入R0与C0构成的触发网络,利用电容耦合抬升主泄放管栅极电位[7],使其在高压下处于微导通状态.图2为本文改进型结构的剖面示意图.改进主要集中在A和B两处,将泄放管MN3与MN2的栅极接入触发电路,并在触发电路中增加钳位管mn0,限制栅极电位上升的幅度.

图2 改进型衬底触发GGMOS剖面图

主泄放管MN2/MN3的微导通,使泄放能力更强的沟道也成为ESD能量的泄放通道,增加了沟道泄放电流i4与i5,从而增强该结构的泄放能力.同时,由于处于微导通状态的MOS管具有更低的击穿电压,从而使抬升栅电位后的结构具有更低的触发电压[8].但是,主泄放管栅电位的抬升,也增加了端口正常工作时的漏电.同时,主泄放管的栅电位的过度爬升会降低主泄放管二次击穿点电流从而降低其耐压能力[3].为了尽量减小漏电,保证泄放管的耐压能力,需要合理设计栅端电位的抬升量,使正常工作信号输入时,栅电位抬升较小,减小漏电; 而在ESD信号输入时,栅电位抬升较大,使主泄放管导通.同时需加入钳位机制限制栅端电位的上升,结合抬升衬底电位可提高MOS管二次击穿电流It这一特征[4].可适当增加注入衬底的电流量来抵消抬升栅电位对主泄放管耐压能力的影响,最终使得该结构在达到较低触发电压的同时,还能保持较高的耐压能力.

1.2主要电路设计

电位抬升单元是本文电路设计的重点,忽略MN0/MN1管与主泄放管MN2/MN3寄生,该电位抬升电路如图3(a)所示为一阶高通电路.

图3 电路等效模型

当Va输入为线性时变电压V(t)=V′t时(其中V′为电压变化率),Vb结点抬升电位ΔV的响应可表示为:

ΔV=V′RC[1-exp(-t/RC)].

(1)

针对实际电路,考虑MOS管寄生栅漏电容C0后,等效模型如图3(b)所示,修正后的关系可表示为:

ΔV=V′RC{1-exp[-t/R(C+C′)]}.

(2)

寄生电容C′的引入改变了时间常数,但未改变最终ΔV最大抬升值,因此本文设计忽略C′对电压抬升带来的影响,选取合适的RC来抬升栅压.

图3中参数R由图2中电阻R0,衬底电阻与图2中饱和导通管mn0及主泄放管衬底与源端PN结组成,参数C主要为图2中修调电容C0.其中mn0管为栅电压钳位管,降低触发栅电位受脉冲变化率的影响.mn0管和衬底电阻的并联结构与电阻R0和MN1管栅源电容的并联构成分压关系抬升衬底电压,降低栅电位对二次击穿点(主泄放管耐压能力)的影响,同时提高泄放管泄放能力.

在ESD信号输入时,由于mn0管与衬底PN结的导通,衬底电阻被短路,衬底端电位保持一个阈值电压Vt,假设主泄放管栅端最大可抬升为VGmax,则RC电路的抬升量为ΔVm=VGmax-Vt,因此,此时图2中参数R0与C0满足关系式:

ΔVm>V′R0×C0.

(3)

在正常信号输入时,由于mn0管与衬底PN结均未打开,图3中电阻R由图2中衬底电阻Rsub与R0串联构成,主泄放管栅端最大可抬升电压VGmax由端口所允许的最大漏电流IDmax决定,IDmax与VGmax满足MOS管亚阈值区电流关系式:

IDmax=Ispecexp[(VGmax-Vt)/nVT].

(4)

式中:Ispec=2nμCox(W/L)VT2;Vt为NMOS阈值电压;n为晶体管的斜率因子;VT=KT/q为热力学电压.此时,由最大允许漏电流得出的VGmax与图2中参数R0与C0同样满足关系式(3).

本文最终在CSMC HJ018工艺下设计并验证了该ESD泄放结构.针对4 kV HBM应用,电压变化率V′=4 kV/10 ns=400 V/ns.针对75 MHz 3.3 V端口应用,上升沿1~2 ns,电压变化率约V′=3.3 V/ns,且最终根据版图尺寸得出的等效体电阻约为1 kΩ[5].在最大漏电流不超过1 μA的情况下,由式(3)(4)得出的C0小于50 fF时,R参数小于10 kΩ,此时R参数值即Rsub与R0之和.

2测试分析

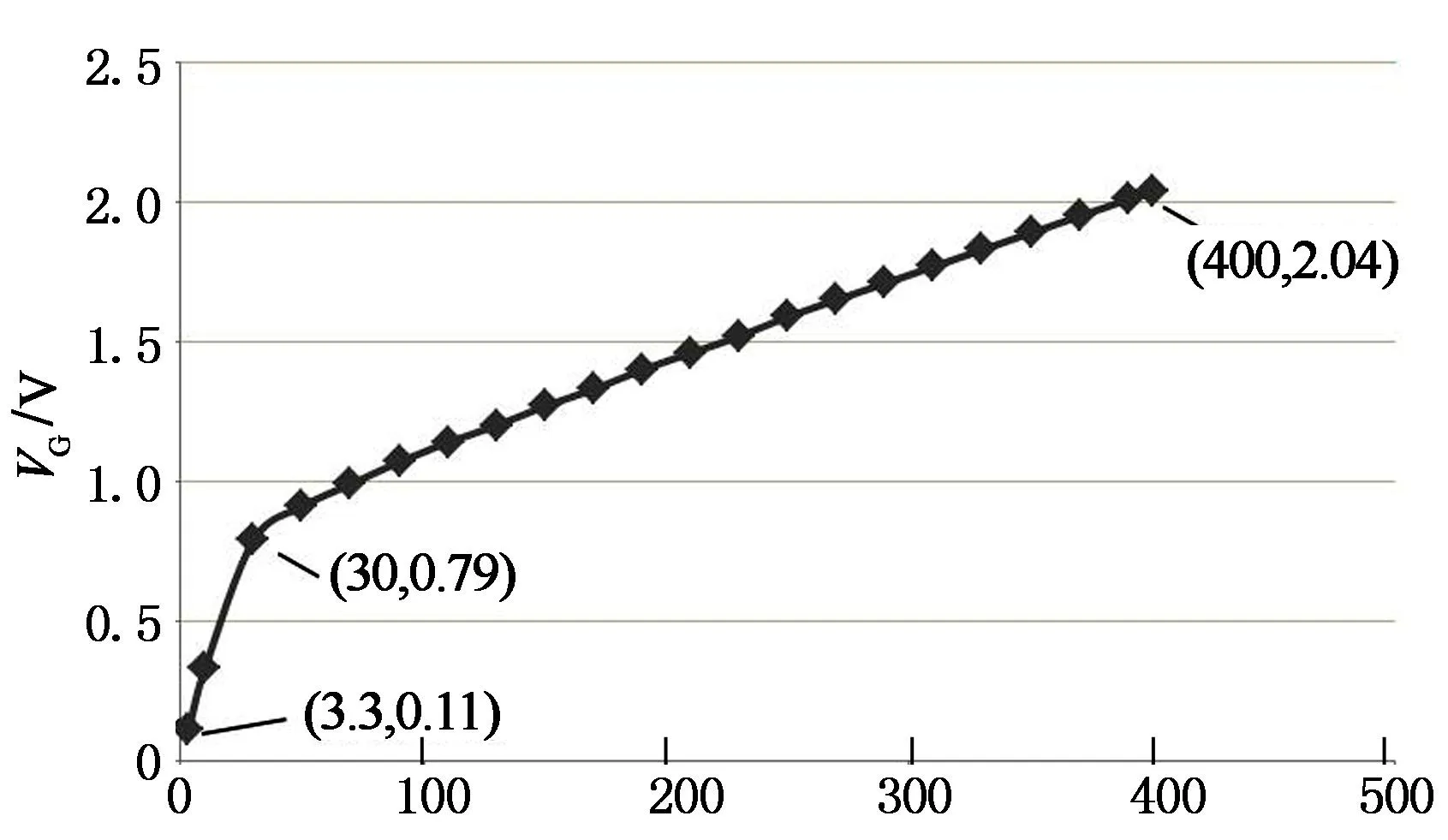

根据上一节的分析与最终确定的尺寸信息,在CSMC HJ018工艺下Spectre仿真得到触发栅电压与信号爬升速度的关系如图4所示.当输入为正常75 MHz 3.3 V信号时,电压变化率V′均为3.3 V/ns,栅压抬升仅0.11 V,在爬升率30 V/ns处出现明显的钳位拐点,可明显看到mn0管与衬底PN结对栅触发电压爬升的钳制作用.最终在400 V/ns(ESD军用标准下电压变化率)处栅压抬升2.04 V,防止栅电压过度抛高而降低主泄放管二次击穿点It,同时也使主泄放管栅压在较宽的范围内保持一个合理的值.

根据1.1和1.2的分析,在smic18 mmrf工艺下流片验证的ESD结构如图5所示.其中,区域Ⅰ为图3中所示MN0~MN3管,区域Ⅱ为耦合电容C0,区域Ⅲ为电阻R0,区域Ⅳ为钳位管mn0.图3中所示PAD端覆盖于结构上与区域Ⅰ中MOS管漏端相连.本文采用近年来较流行的传输线脉冲测试方法(TLP)来测试PAD端输入电压与电流之间的I-V特性曲线[9].

V′/(V·ns-1)

图5 芯片结构

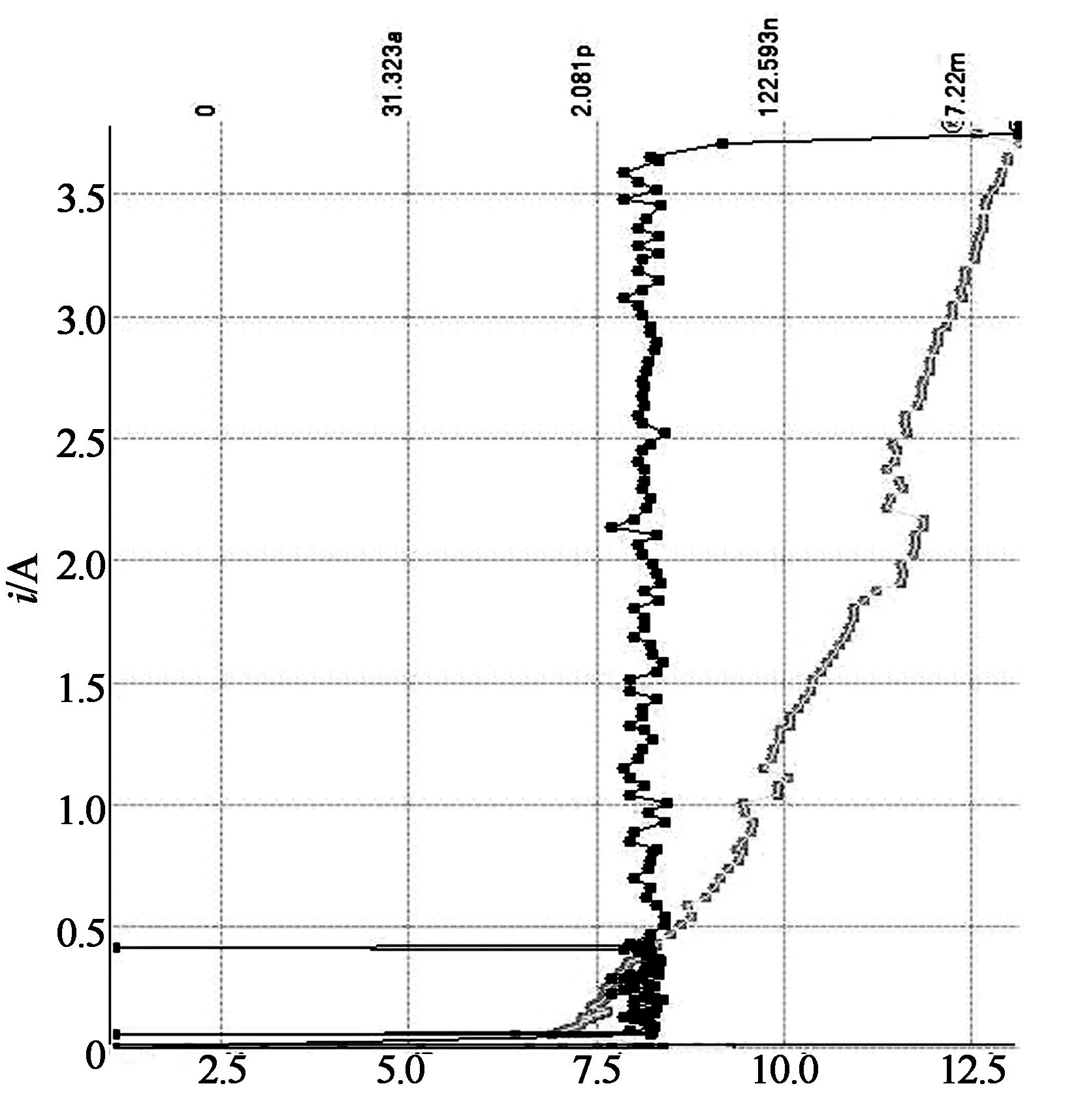

图6所示为该结构在TLP平台下的测试结果,在输入PAD端的阶跃电压达到8 V左右时ESD结构触发,电流开始增加.当电流增加到3.7 A左右时ESD结构发生二次击穿,结构被损坏,此时的电流即二次击穿电流It.人体模型(HBM)的等效输入电阻为1 500 Ω,因此,由TLP平台测试得到的二次击穿电流It与等效HBM耐压能力VHBM之间的换算关系为VHBM=It×1 500.

V/V

由于采用工艺的差异,本文所提出结构与文献[3]所提出结构的触发电压并无可比性.但CSMC HJ018工艺典型击穿值10 V以上,本文所提出结构的触发电压为8 V左右,降低了触发电压.文献[3]中提出结构的二次击穿电流It最大不超过2.3 A,等效HBM电压VHBM=It×1 500 <3 450 V.本文所提出结构的二次击穿电流It=3.7 A,等效HBM电压为VHBM=It×1 500=5 550 V,等效导通电阻为3 Ω,达到4 kV以上军用标准[1],较文献[3]所提出结构具有更高的泄放能力.

3结论

本文采用栅耦合技术,使所提出的ESD结构在CSMC HJ018工艺典型击穿值10 V之前即触发.同时,利用抬升衬底电位可提升二次击穿电流It这一特点,成功弥补了栅耦合MOS ESD泄放结构二次击穿点低的缺点,在降低ESD泄放结构触发电压的同时保持较高二次击穿电流,在CSMC HJ018工艺下完成了一款触发电压低于10 V,HBM防护等级达到4 kV军用级别的NMOS ESD防护结构,优化了栅耦合技术在MOS ESD泄放结构中的应用.

参考文献

[1]Department of Defense of USA. MIL-STD-883Gmethod 3015.7[S]. Washington, DC: Department of Defense of USA, 2006.

[2]OH K H, DUVVURY C, BANERJEE K,etal. Gate bias induced heating effect and implications for the design of deep submicron ESD protection[C]//Proceedings of IEDM '01. New York: IEEE, 14.2.1-14.2.4.

[3]KER Ming-dou, CHEN Tung-yang. Substrate-triggered technique for on-chip ESD protection design in a 0.18 μm salicided CMOS process[J]. IEEE Transactions on Electron Devices,2003, 50(4):1050-1057.

[4]KER Ming-dou, CHEN Tung-yang. Substrate-triggered ESD protection circuit without extra process modification[J]. IEEE Journal of Solid-state Circuits, 2003, 38(2):295-302.

[5]吴晓鹏. 基于深亚微米CMOS工艺的静电防护器件研究[D].西安:西安电子科技大学物理与光电工程学院,2013: 45-46.

WU Xiao-peng. A study of ESD protection device based on deep submicron CMOS technology[D]. Xi'an: School of Physics and Optoelectronic Engineering, Xidian University, 2013: 45-46.(In Chinese)

[6]宁慧英,臧晶. 基于深亚微米工艺的ESD保护器件优化设计[J].机械设计与制造,2012(5):134-136.

NING Hui-ying, ZANG Jing. Design optimization of ESD protection device based on submicron CMOS process [J]. Machinery Design & Manufacture, 2012(5):134-136.(In Chinese)

[7]李志国,余天宇,张颖,等. 基于RC触发NMOS 器件的ESD 电路设计[J]. 半导体集成电路,2014, 39(8):579-583.

LI Zhi-guo, YU Tian-yu, ZHANG Ying,etal. Design of the ESD circuit based on the RC triggered NMOS device[J]. Semiconductor Technology, 2014, 39(8):579-583. (In Chinese)

[8]BICLEANU D P, NICUTA A M, SALCEANU A. A novel ESD protection structure used to enhance the safety of the MOSFET integrated circuitry[C]// Proceedings of 2013 8thInternational Symposium on Advanced Topics in Electrical Engineering. New York: IEEE, 2013:1-6.

[9]陆坚,朱卫良. 一种新型IC保护单元ESD评价方式—TLP测试[J].电子与封装,2008, 8(12):13-16.

LU Jian, ZHU Wei-liang. The new method for IC ESD protect constructures—TLP [J]. Electronics and Packaging, 2008, 8(12): 13-16.(In Chinese)

An On-chip NMOS ESD Protection Circuit with Low Trigger Voltage and High ESD Robustness

CHEN Di-ping†, LIU Xing, HE Long, CHEN Si-yuan

(School of Physics and Microelectronics, Hunan Univ, Changsha, Hunan410082, China)

Abstract:This paper designed a NMOS ESD protection circuit with low trigger voltage (trigger voltage ≤10 V) and high ESD robustness (HBM ESD level≥4 kV). It raises the bias voltage of both the gate and the substrate of the main discharge element to an appropriate extent by designing a gate-coupled RC-network with voltage-clamping function. This not only provides a stronger discharge capacity and lower trigger voltage but also maintains a high secondary breakdown current. In this case, the ESD robustness of the MOS protection structure in CMOS deep submicron circuit is strengthened. The design is taped out in CSMC HJ018 process, and tested through TLP platform, which shows the trigger voltage is lower than 10 V and the secondary breakdown current is 3.5 A.

Key words:Electro-Static discharge(ESD); substratetrigger; gate coupling; TLP

中图分类号:TN47

文献标识码:A

作者简介:陈迪平(1963-),男,湖南醴陵人,湖南大学副教授†通讯联系人,E-mail:chdp@hnu.edu.cn

基金项目:湖南省科技计划项目(2014FJ1003)

*收稿日期:2015-01-09

文章编号:1674-2974(2016)02-0115-04