卫星固态存储器数据容错设计与机制*

2016-04-08邹业楠安军社

宋 琪,邹业楠,李 姗,安军社,朱 岩

(1.中国科学院 空间科学与应用研究中心, 北京 100190; 2.中国科学院大学, 北京 100190)

卫星固态存储器数据容错设计与机制*

宋琪1,2,邹业楠1,2,李姗1,2,安军社1,朱岩1

(1.中国科学院 空间科学与应用研究中心, 北京 100190; 2.中国科学院大学, 北京100190)

摘要:卫星数据传输系统的可靠性面临着空间粒子效应、信道干扰等多重威胁。 在介绍数据传输系统关键设备星载大容量固态存储器设计与实现的基础上,从管理信息、数据位流、星地链路、文件传输四个方面构建容错机制,综合应用汉明编译码、RS编译码、低密度奇偶校验码编码等数据检纠错技术,增强存储器管理信息、存储数据、信道传输的容错性能。在实际型号任务固态存储器的基础上,结合CCSDS文件传输协议提出基于自动重传机制的文件可靠传输设计,提高数据传输全流程的容错性能。固态存储器使用多级流水写入、总线并行扩展等技术,吞吐率理论上接近900Mbps,容量达到256Gb。

关键词:固态存储器; 容错机制; 检纠错码; 自动重传请求; CCSDS文件传输协议

随着国内航天事业发展水平不断提高,航天器的有效载荷数量、种类及任务形式越来越丰富,空间平台数据呈现出信源多、数据量大、数据类型多样的特点,对卫星数据传输系统的技术水平要求不断提高。存储器是航天器数传、数管系统的核心设备之一。基于半导体工艺固态存储器(Solid State Recorder, SSR)具有抗震、容量大、技术储备丰富[1]的优点,已经成为航天器存储设备主流。而基于NAND Flash的大容量固态存储器则具有存储密度高、功耗低、非易失的特点,竞争力强[2]。商用Flash存储器一般采用硬盘管理技术加Flash转换层(Flash Translation Layer, FTL)的结构,可以直接处理串行高级技术附件(Serial Advanced Technology Attachment, SATA)命令[3],但管理复杂、接口速率存在瓶颈,不适合航天任务。航天用SSR一般采用现场可编程门阵列(Field Programmable Gate Array, FPGA)直接控制存储介质,提高接口吞吐率,降低系统复杂度,使用多级流水、总线扩展技术,以便获得更高的性能和可靠性。

国内的卫星任务使用过多次基于同步动态随机存取记忆体(Synchronous Dynamic Random Access Memory, SDRAM)、DARM[4]的SSR,近年来以Flash为主[5]。NASA的Landsat7[6]和后续2012年的LDCM[7]项目都使用了基于SDRAM的SSR,形成了较为成熟的数传系统。当前,如果没有半导体技术革命性的进展,单个SSR很难保持容量快速提升,现阶段对SSR的研究以文件管理和数传系统综合研究为主。

SSR的设计使用较为复杂[8]。根据卫星数传系统实际工作模式和需求,介绍基于Flash的星载固态存储器设计,分析数据容错机制。为保证任务数据的可靠性,针对Flash存储介质可能产生的单粒子效应[9]和介质退化效应,采用汉明码保护存储器的管理信息,使用交织深度为4的RS编解码保护数据位流。数据下行时采用低密度奇偶校验码(Low Density Parity Check Code, LDPC)编码提高星地链路信噪比。同时在实际型号固态存储器平台和类文件化管理基础上,结合CCSDS文件传输协议[10](CCSDS File Delivery Protocol, CFDP),研究自动重传(Automatic Repeat-reQuest, ARQ)机制下的文件传输容错。错误检测与纠正(Error Detection And Correction, EDAC)技术与ARQ策略的综合使用,提高了存储器的管理信息、数据位流、星地链路、文件传输四个方面的数据容错性能。

1卫星SSR的设计及应用工作模式

1.1基于Flash的固态存储器基本设计

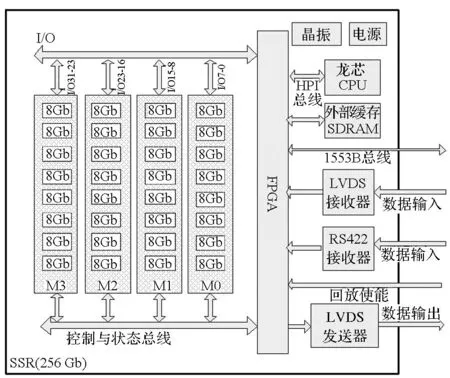

卫星固态存储器采用FPGA作为控制器,配有CPU地址管理软件,其架构如图1所示。FPGA中例化1553B远程终端IP核[11]进行通信。数据吞吐率理论上接近900 Mbps,容量128 Gb/256 Gb/512 Gb可选。

图1 卫星固态存储器单板架构Fig.1 SSR structure

Flash芯片工作频率最大为40 MHz,写入需要300 μs~700 μs编程时间,应用实测为400 μs~500 μs,四级流水写入可保证整体上无中断写入。四倍总线并行扩展将数据位宽从8位扩展为32位,将4页Flash空间视为一个整体“簇”统一操作。对于坏块管理,包括初始坏块、编程坏块、擦除失败坏块[12-13],初始坏块不纳入使用。编程坏块则马上将下一块作为替代块重新写入数据。擦除失败块将被标示为初始无效块等效处理。

1.2类文件化数据分区管理

传统存储器将数据顺序存储,按存储地址、时间进行索引。为了提高数据的访问效率,减轻下行信道压力,对数据进行分区类文件化管理。

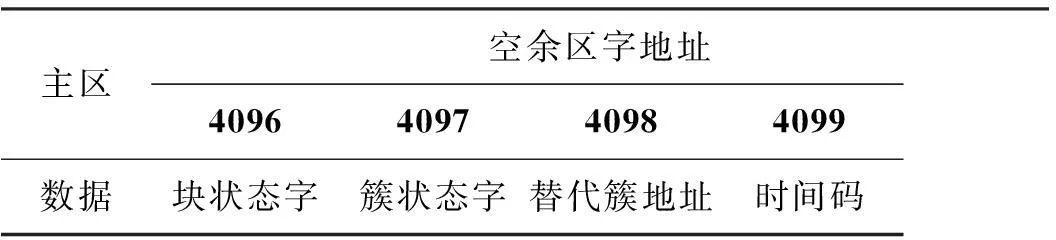

如表1所示,Flash使用时将簇使用信息写入空余区。FPGA根据簇信息组织块信息表送往CPU,CPU以此为基础进行数据分区管理,并根据系统运行实时更新。

表1 簇内地址内容分配表

数据写入流程如图2所示,数据的分区与物理地址的映射由CPU管理,数据流的处理由FPGA实现。数据进入存储器主控FPGA后,经合路RS编码,进入外置SDRAM分通道缓存。外部缓存的通道与分区一一对应。

图2 数据写入流程Fig.2 Process of data writing

1.3数传系统工作模式

数传系统是固态存储器的工作平台,其工作模式和流程,是数据可靠性研究的基本条件。

随着有效载荷数量和数据量的急速增大,分布式、集群式等新的高级存储架构必然需要存储节点容量均衡功能,其架构如图3所示。高级均衡模式可应用于节点容量均衡、异地备份等情景,存储器内的分区数据视作文件,在源节点与目的节点之间按照CFDP协议进行文件传输,将旧有数据部分搬移到另一存储单板或存储节点上。

图3 高级存储架构示意图Fig.3 Advanced SSR structure diagram

2容错机制的设计及分析

容错机制从数据传输系统的各个环节入手,综合采用EDAC技术,保护管理信息、数据位流、星地链路,同时结合数据的文件化管理,研究CFDP可靠传输技术,保护文件传输。

2.1基于汉明码的存储管理信息容错设计

存储器的管理信息存放于Flash的空余区,管理信息在轨可能受单粒子效应等影响产生错误,汉明码能够有效提高管理信息的可靠性。

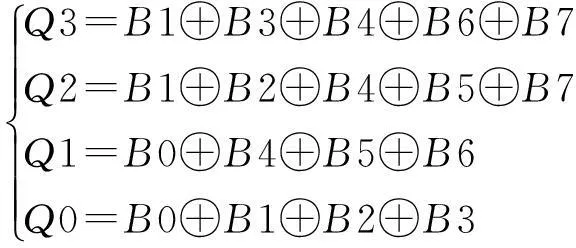

在数据存储的过程中,FPGA自动在空余区加载各簇的“簇标识字”。为避免长时间储存单粒子翻转,采用速度快易实现的(12,8)汉明码进行保护,能够通过解码纠正8位数据中的单个错误[14]。设原码信息位为B0~B7,增添的编码校验位为Q0~Q3,选用校验矩阵为

(1)

根据

HCT=0T

(2)

则校验位为:

(3)

当存储节点上电初始化或者复位时,FPGA遍历存储空间所有空余区,读取簇标识字及与其对应的校验位R0~R11,根据校验矩阵得伴随向量S为

(4)

则可知伴随向量对应的出错位置对应关系如表2所示。

表2 汉明码译码查表

若只估算单粒子翻转,逻辑器件低轨出现位错的概率量级为10-7位/d,中轨的量级为10-6位/d[15]。以此为前提进行测算结论如图4所示。

图4 误比特率Fig.4 Bit error rate

2.2基于RS编解码的存储数据位流容错设计

数据位流在卫星平台上可能受到单粒子效应、结构干扰出错,RS编解码具有较强的纠错能力,能够提高数据位流的可靠性。

2.2.1交织RS方案

在Flash空间中可能发生单粒子翻转造成存储数据位出错,而且介质外置缓存、Flash的I/O接口干扰也有可能带来突发错误。为了保护数据,在写入Flash之前进行RS编码,读出Flash时进行解码纠错,RS编码结构如图5所示。

设计采用的RS(256,252)技术是在标准RS(255,252)码的基础上增添一个校验码拓展而来,每个码字由 8 bit组成,将标准RS检二纠一性能[16]提升到检二纠二,但代价是当错误码字多于2个时,它不能严格标识错误。RS编码交织有利于将错误离散化,采用交织深度为4的编码方案。待存储的数据串并转换为32 位,相同字节位置的连续252 Byte作为码块的信息元,经编码后增加4个校验码元。

图5 RS编码结构示意图Fig.5 RS encoding process

2.2.2RS编译码算法简介

RS(256,252)码的生成多项式为

P(x)=x8+x4+x3+x2+1

(5)

设编码后的码字为

C=[c255c254c253…c2c1c0]

(6)

其中C3,C2,C1为按照RS(255,252)码生成的对应编码信息的一般校验位,C0是扩展奇偶校验位。设数据的错误向量为E,则最终读出得到的码字V为C与E的模和。

访问数据时,从Flash读取出来后,经译码送往输出缓存,经并串转换后从节点出口输出。译码时计算出E后,与V进行模和,完成纠错。

V+E=C+E+E=C

(7)

求解错误向量E首先需要计算伴随向量S。

设α是生成多项式P(x)=0的本原元,则所需校验矩阵为

(8)

所以S=(S0S1S2S3)=VgHT

(9)

(10)

同时可得辅助译码参数

(11)

译码策略如表3所示。

表3 RS译码策略

若只估算单粒子翻转,半导体介质低轨出现位错的概率量级为10-8位/d,中轨的量级为10-7位/d[16]。以此测算结论,如图6所示。

图6 RS码误组率Fig.6 RS frame error rate

2.3基于LDPC编码的星地链路容错设计

星地链路传输距离远、信号弱、噪声大,LDPC能够有效提高星地链路信道信噪比。

当卫星过境时,实时/延时数据将经过LDPC编码后下行至地面。LDPC具有稀疏矩阵,信道增益强,理论上接近香农限,基于可信传播的迭代译码与信道容量只有零点几个dB的差距。迭代译码较为复杂,需要大量的计算和缓存资源,在星上平台实现译码比较困难,一般由地面接收进行译码。CCSDS推荐近地通信使用基于LDPC(8176, 7156)改进的LDPC (8160, 7136)码,两者的性能相差无几,但后者的编码长度是32的整数倍,更有利于保证数据传输格式的完整,也便于计算机处理。实际设计中采用LDPC (8160, 7136)增强星地通信可靠性,具体流程如下:

1)接收存储器来的7136 bits数据,在之后补充18个‘0’,得到7154 bits序列。

2)LDPC校验矩阵由32个511×511的循环方阵Aij组成

(12)

CCSDS给出了标准的循环矩阵,可得包含有28个循环矩阵Bij的7154×8176生成矩阵G。

(13)

3) 7154 bits经生成矩阵得到8176 bits序列,去掉头部的18个‘0’,在尾部增添两个‘0’,得到8160 bits的序列,即为编码后的序列。

LDPC能够获得的信噪比增益与迭代译码的迭代次数有关。CCSDS给出了较为丰富的测试结果[17]。在同等信噪比下,50次迭代译码复杂度高,但误码率较10次迭代有明显降低。

2.4基于CFDP的文件传输容错ARQ策略

提高数据可靠性,不仅需要纠错、抗噪,对数据格式完整性的保护同样重要,使用CFDP可靠传输模式能够有效提高文件传输可靠性。

当前我国星上数据的存储、传输均采用位流的形式,对存储管理而言数据访问模式单一,仅能通过指定存储地址或指定之间进行访问,导致访问效率低,管理程度差。特别是航天任务数据越来越多越来越复杂,而星地链路却非常有限的情况下,急需提升数据综合管理技术。CCSDS推荐的CFDP协议是一种针对大误码率、大延时链路可靠数据文件传输的标准。传统的数据传输没有实现保证数据完整性的机制,所有数据按比特流顺序传输完成,即意味着传输完毕。CFDP支持数据丢失重传,针对不同数据对完整性的要求不同,按要求完成数据传输。

CFDP协议单元实体接收到传输文件的指令后,将待发送文件分为若干数据包封装成PDU。发送方首先发送元数据包MPDU,包括本次事务ID号、源文件名、目的文件名、文件大小等参数,通知接收方开始传输文件,然后发送文件数据PDU。发送完毕之后,发送一个文件结束数据包。不需握手,减少了传输时延和带宽资源的浪费。如果接收方接收到了标有新的ID的文件数据单元,代表一个新的事务开始。CFDP每一个PDU都含有一个特殊的字段,标明该PDU在待传文件中的起始偏移地址,接收方通过校验接收到的PDU的序列字段判断哪些PDU发送失败。

对于可靠文件传输,CFDP应用丢失检测重传机制来保证文件的完整性和正确性[18],事件流如图7所示。与传统ARQ相比,接收端仅对传输出错的PDU向发送方传送否定确认信息NAK而不是确认信息ACK,ACK确认信息只用于文件结尾和结束。文件传输过程一般分为文件传输检测过程和文件延时检测过程,在文件发送完毕后再进入文件延时检测阶段,从而降低协议信令。

图7 CFDP可靠传输事件流Fig.7 Events stream of CFDP reliable transmission mode

3结论

卫星数据传输系统有着独特的工作模式,其传输速度、数据可靠性等性能需要SSR整体配合。SSR数据传输处理采用多种EDAC组合提高数据可靠性。在实际型号任务SSR设计的基础上,对类文件管理和文件传输容错机制展开进一步研究,以期不断提高技术应用水平,满足快速提升的航天任务需求。

参考文献(References)

[1]陆游游,舒继武. 闪存存储系统综述[J]. 计算机研究与发展,2013,50(1):49-59.

LU Youyou, SHU Jiwu. Survey on flash-based storage systems[J]. Journal of Computer Research and Development, 2013,50(1):49-59.(in Chinese)

[2]Hsieh J W, Tsai Y L, Kuo T W, et al. Configurable flash-memory management: performance versus overheads[J].IEEE Transactions on Computers, 2008, 57(11): 1571-1583.

[3]张辉,晏益慧,罗宇. 大容量NAND Flash文件系统转换层优化设计[J]. 计算机工程与科学,2011,33(4):81-85.

ZHANG Hui, YAN Yihui, LUO Yu. Optimization design of the NAND flash transition layer based on the large-scale NAND flash[J]. Computer Engineering & Science,2011, 33(4): 81-85.(in Chinese)

[4]王芳,李恪. 空间太阳望远镜的星载固态存储器研制[J]. 电子学报,2004,32(3):472-475.

WANG Fang, LI Ke.Development of onboard solid state recorder for space solar telescope[J]. Acta Electronica Sinica, 2004,32(3):472-475. (in Chinese)

[5]陈斌, 沈卫华, 朱岩, 等.嫦娥二号卫星大容量存储器设计[J].航天器工程, 2011,20(5):99-104.

CHEN Bin, SHEN Weihua, ZHU Yan, et al. Design of solid state recorder for chang′e-2 orbiter[J]. Spacecraft Engineering, 2011,20(5):99-104. (in Chinese)

[6]Arvidson T, Goward S N, Gasch J, et al.Landsat-7 long term acquisition plan: development and validation[J]. Photogrammetric Engineering and Remote Sensing, 2006, 72(10): 1137-1146.

[7]姜高珍, 韩冰, 高应波,等. Landsat系列卫星对地观测40年回顾及LDCM前瞻[J]. 遥感学报, 2013,17(5): 1033-1048.

JIANG Gaozhen, HAN Bing, GAO Yingbo,et al. Review of 40-year earth observation with landsat series and prospects of LDCM[J]. Journal of Remote Sensing, 2013, 17(5): 1033-1048. (in Chinese)

[8]高怡祯. 基于闪存的星载大容量存储器的研究和实现[J]. 电子技术应用, 2003,29(8):75-78.

GAO Yizhen. Research and application of airborne solid state recorder based on flash[J]. Application of Electronic Technique, 2003,29(8):75-78. (in Chinese)

[9]Gaspard N J, Jagannathan S, Diggins Z J, et al. Technology scaling comparison of flip-flop heavy-ion single-event upset cross sections[J]. IEEE Transactions on Nuclear Science, 2013, 60(6):4368-4373.

[10]Pavale S, Unnikrishnan E, Laksminarasimhan P. Design, implementation and performance evaluation of CCSDS CFDP protocol[C]// Proceedings of 2010 IEEE International Conference on Computational Intelligence and Computing Research (ICCIC),IEEE,2010:1-4.

[11]周莉, 安军社, 谢彦, 等.基于ASIC技术的1553B IP核的设计[J],空间科学学报, 2014,34(1):127-136.

ZHOU Li, AN Junshe, XIE Yan, et al. Design of a 1553B IP core based on ASIC technology[J]. Chinese Journal of Space Science, 2014,34(1):127-136. (in Chinese)

[12]Fabiano M, Furano G. NAND flash storage technology for mission-critical space applications[J]. IEEE Aerospace & Electronic Systems Magazine, 2013, 28(9):30-36.

[13]郑文静,李明强,舒继武. Flash存储技术[J].计算机研究与发展,2010,47(4):706-726.

ZHENG Wenjing, LI Mingqiang, SHU Jiwu. Flash storage technology[J]. Journal of Computer Research and Development, 2010,47(4):706-726.(in Chinese)

[14]Rhee S, Kim C, Kim J, et al. Concatenated reed-solomon code with hamming code for DRAM controller[C]// Proceedings of the 2010 Second International Conference on Computer Engineering and Applications-Volume 01,IEEE Computer Society, 2010:291-295.

[15]Xiao Y, Luo C L, Yang C. The comparative analysis of LDPC and RS code[C]// Proceedings of 2011 International Conference on Consumer Electronics, Communications and Networks (CECNet),IEEE, 2011:4510-4513.

[16]贺朝辉. 空间轨道单粒子翻转率预估方法研究[J].空间科学学报, 2001,21(3):66-73.

HE Chaohui.Study of methods for predicting SEU rate in space orbits[J]. Chinese Journal of Space Science, 2001, 21(3): 66-73.(in Chinese)

[17]CCSDS 131. 1-O-2. Low density parity check codes for use in near-earth and deep space applications[S].Consultative Committee for Space Data Systems, Washington DC,USA,2007.

[18]Back W, Lee D C. Expected file delivery time of immediate NAK ARQ in CCSDS file delivery protocol[C]//Proceedings of Aerospace Conference,IEEE,2003,41:503-524.

Design and mechanism of the fault tolerance of solid state recorder

SONGQi1,2,ZOUYenan1,2,LIShan1,2,ANJunshe1,ZHUYan1

(1.Center for Space Science and Applied Research, Chinese Academy of Sciences, Beijing 100190, China;2.University of Chinese Academy of Sciences, Beijing 100190, China)

Abstract:The satellite data transmission system is faced with various threats such as single event upset in semiconductor devices, the transmission noise and so on. The key component of the design and implementation of high-capacity SSR (Solid State Recorder) of the transmission system was introduced, and based on the SSR, a fault tolerance mechanism was proposed to protect management information, data bit stream, satellite-to-ground link and file delivery. The mechanism improved the fault tolerance ability of the management information of SSR, the data in store and the transmission channel with the hamming code, the RS code and the LDPC (Low Density Parity Check Code) encoding. Advanced research of one automatic repeat request method with CFDP (CCSDS File Delivery Protocol) was also proposed based on the SSR of one actual space mission to improve the transmission reliability in file-level. The SSR used 4-pipeline writing and bus expansion techniques to achieve the throughput rate of almost 900Mbps theoretically and the capacity of 256Gb.

Key words:solid state recorder; fault tolerance mechanism; error detection and correction; automatic repeat request; CCSDS file delivery protocol

中图分类号:TP333

文献标志码:A

文章编号:1001-2486(2016)01-101-06

作者简介:宋琪(1989—),男,山东菏泽人,博士研究生, E-mail:songqi@nssc.ac.cn;朱岩(通信作者),男,研究员,博士,博士生导师,E-mail:zhuyan@nssc.ac.cn

基金项目:中国科学院空间科学战略性科技先导专项基金资助项目(XDA04060300)

*收稿日期:2015-03-09

doi:10.11887/j.cn.201601017

http://journal.nudt.edu.cn