厚膜HIC镀金引线柱直接采用锡基焊料研究

2016-03-30刘俊夫

刘俊夫,郑 静

厚膜HIC镀金引线柱直接采用锡基焊料研究

刘俊夫,郑 静

(中国电子科技集团公司第43研究所,安徽 合肥 230088)

电装行业中对镀金界面采用锡基焊料软钎焊之前进行搪锡去金的标准一直存在争议。采用SEM、体视显微镜等设备对厚膜混合集成电路(HIC)组装过程中镀金引线柱采用锡基焊料钎焊(不进行搪锡去金处理)工艺进行了研究。结果发现,典型金层厚度(1.3~2.5 μm)引线柱钎焊后能够通过环境试验应力考核和高温-长期储存试验;内引线柱局部镀薄金(0.5~1 μm)的样品在高温-长期储存试验过程中抑制Ni-Au-Sn化合物生长的效果更加明显,可以作为一种高可靠HIC镀金引线柱不去金焊接的优选封装结构。

厚膜混合集成电路;镀金引线柱;锡基焊料;金脆;搪锡;钎焊

锡基软钎焊工艺对焊接界面的可焊性比较敏感,为了避免焊接界面氧化,通常会采用电镀/化镀镍-金层来保护焊接表面并实现焊接过程中焊料的良好浸润[1-5]。但是20世纪80年代,中国空间技术研究院的某型产品镀金引线焊点的焊接界面发生了开裂的失效模式,在失效分析的过程中引出了镀金界面采用锡基软钎焊工艺产生“金脆”的问题。因此,该院在国内电装领域较早地提出了镀金引线在焊接前要进行搪锡去金处理的要求。

多年以来,关于镀金引线柱在焊接前进行搪锡去金处理的国内外标准要求并不统一,电装行业中对该要求的执行情况也不一致[6-14]。尤其是与印制电路板(PCB)电路工艺结构有本质不同的厚膜HIC行业,对于是否应执行这一要求一直有较大的争议,且未见到国内外有文献具体阐述搪锡去金要求在厚膜HIC行业的适用性问题。本文分析了厚膜HIC的行业标准要求以及工艺结构特点,验证了厚膜HIC在组装过程中镀金引线柱直接采用锡基焊料软钎焊(不进行搪锡去金)的可靠性和合理性。

1 “金脆”机理

当在镀金界面进行锡基焊料的软钎焊工艺过程中,由于Au与Sn的相容性非常好,Au、Sn之间的扩散作用产生了多种形式的Au-Sn二元金属间化合物。一般认为:当焊料中Au的质量分数>3%时,AuSn4化合物便会生成。这些中间相化合物的维氏硬度较高,呈脆性。当Au-Sn化合物集中在焊接界面分布成层时会降低焊接界面的强度,这就是所谓的“金脆”现象。

2 不同国家/地区的相关标准

表1统计了各国家/地区的行业标准关于镀金界面进行锡基焊料软钎焊之前进行“搪锡去金”的不同要求。国内很多军工院所从事焊接电装领域的专家们还有一种共识:当镀金层厚度小于1.27 μm时,使用锡基焊料的软钎焊工艺不会产生“金脆”问题,可以不用进行去金处理(当然前提是金层应该足够致密以保护覆盖的阻挡层不被氧化)[15]。也有持保守观点的专家认为所有电装行业都应该按照表1中ECSS-Q-ST-70-18A的要求使用吸锡线去除搪锡的焊料或采用双锡锅法,这样才算是“去金”。

表1 对搪锡去金工艺要求的不同标准

Tab.1 Different standards of pretinning and degolding process requirements

值得关注的是:作为电装领域一个分支行业,表1中所列的混合集成电路主要依据的行业规范并没有要求镀金界面采用锡基焊料软钎焊前进行搪锡去金(虽然GJB2440A——2006规定“引线和引出端的镀金层厚度应为1.3~5.7 μm”)。国内主流的高可靠HIC生产厂家多年来也基本没有未执行这一要求。对Interpoint公司、IR公司、VPT公司等国外主流HIC厂商生产的高质量等级HIC(/883 QML级以及SPACE级)样品进行分析,发现电路内部的镀金内引线柱金层厚度均超过了1.27 μm,均采用锡基焊料软钎焊工艺,但均未采用搪锡去金后再进行焊接的工艺。

图1是镀金层厚度为3.09 μm的引线柱采用Sn62Pb36Ag2焊料进行一次回流焊接的焊接界面剖面图,局部残留了没有完全融入焊料的金镀层,说明较厚的镀金层一次回流焊接不能完全去金。

图1 引线柱焊接后局部残留镀金层

3 仿真分析

厚膜HIC引线柱的典型焊接结构见图2。

图2 厚膜混合集成电路引线柱部位的焊接结构示意图

厚膜HIC采用印制-烧结工艺将导体、电阻、绝缘介质等厚膜浆料附在陶瓷板上作为电路基板。陶瓷板通常采用高强度且热膨胀系数(CTE)与IC裸芯片及10#钢等材质相匹配的Al2O3陶瓷、BeO陶瓷或AlN陶瓷,因此,厚膜HIC能够在钢制管壳中实现气密封装,并且工艺结构的热匹配性好,结构强度高,能够承载很高功率密度的电路。

电装行业一些专家认为厚膜HIC镀金引线柱的焊接工艺要求应与PCB电路一致。但实际上,PCB电路的基板材质和材料属性与厚膜HIC中的陶瓷基板有本质的不同。材料阻燃等级较高的FR4级PCB板通常采用环氧树脂、玻璃纤维和铜箔进行高温层压制成。这种材质在玻璃纤维层压的方向的CTE约为15×10-6/℃,因此,PCB电路在表贴大尺寸IC芯片(如BGA封装结构)时会发生明显的热失配现象。PCB板另一个更加显著的特点是:在垂直于板面的轴方向上,由于没有玻璃纤维的约束,其CTE能够高达(50~60)×10-6/℃,并且吸潮后容易沿轴膨胀;一旦PCB的温度超过g点,轴方向的CTE值还会非线性地成倍增长。这也是导致PCB电路行业中“爆板”现象的主要原因之一。

Al2O3陶瓷基板与FR4级PCB材料属性的差异如表2所示。

表2 Al2O3陶瓷基板与PCB材料属性

Tab.2 Material properties of Al2O3 substrate and PCB

将图2结构的基板分别采用Al2O3和PCB进行建模,然后在温度循环条件下对引线柱焊接面受力情况进行有限元仿真分析。温度条件为:

在整个温度循环过程中,采用Al2O3基板结构的引线柱焊接界面承受的最大主应力(绝对值)分布云图如图3的剖面图所示;采用PCB基板结构的引线柱焊接界面承受的最大主应力(绝对值)分布云图如图4的剖面图所示。

图3 Al2O3基板的引线柱焊接界面承受的应力分布

Fig.3 Stress distribution of pins' soldering structure in Al2O3substrate

分别在图3和图4中的焊接界面取A点和B点两个取样点,然后采集两个取样点随温度变化过程中的受力情况,如图5和图6所示。

通过图3~图6能够看出:在温度循环条件下使用PCB基板的引线柱焊接界面受力更大,焊接界面更容易失效,尤其是在高温条件下。而很多整机单位使用的PCB厚度大于1 mm,这种轴方向的失配现象更加显著。

因此,相比于电装行业通用的PCB电路以及分元立器件的行业标准考核要求,HIC行业标准要求的环境试验考核条件更加严酷并且具有本行业特殊的禁限用工艺要求。这些标准要求与其混合集成的特点以及稳定性更高的工艺结构设计是紧密相关的。HIC行业多年的发展历程也验证了行业标准的合理性。

图4 PCB基板的引线柱焊接界面承受的应力分布

图5 A点应力与温度对应关系

图6 B点应力与温度对应关系

4 可靠性验证

为验证高可靠厚膜混合集成电路组装过程中镀金引线柱采用锡基焊料软钎焊(不进行搪锡去金处理)工艺的可靠性,本文设计了以下系列的验证试验。

4.1 耐环境应力试验

随机抽取中国电科43所圣达公司为某空间项目配套金属管壳(封口面周长166 mm)中的镀金引线80根引线柱,用Fisher XBLM237型X射线测厚仪进行镀金层厚度测量。测量结果表明:镀金层的厚度区间为1.6~2.41 μm,平均值为1.8 μm。选择不同金层厚度的引线柱样品分别编号为a#(1.65 μm)、b#(2.41 μm)、c#(1.6 μm)、d#(2.15 μm)、e#(2.15 μm)。所有引线柱均不进行搪锡去金处理,随外壳一起按照图2的结构采用再流焊工艺一次完成焊接,基板材质为Al2O3(纯度96%)。将上述样品用平行缝焊方式完成密封后,进行表3所示的环境试验。其中温度循环试验的循环次数为215次,严于GJB2438A——2002中C1分组QML条件规定的100次循环。

4.1.1 镜检

环境试验结束后,在30~50倍体视显微镜下对引线柱样品焊接结构形貌进行观察:引线柱焊点表面光亮,焊接界面无开裂等受损迹象。

表3 环境试验条件

Tab.3 Environment test conditions

4.1.2 SEM和EDS分析

使用FEI Quanta 200型扫描电子显微镜对a#、b#引线柱样品的焊接结构剖面进行SEM和EDS分析,结果如图7和图8所示。

通过对图7和图8分析可以看出:引线柱焊接界面区域结合良好、致密,Au-Sn金属间化合物未发现有明显的积聚和突出生长,也未见其成层分布,样品的焊接界面无金属间化合物脆化导致开裂的情况。距Ni-P层约5~10 μm之间的反应产物层中C、D两点的成分数据表明引线柱镀金层已完全熔入钎料中。图8中的数据表明Ni-P层以外的反应产物层厚度约2 μm,主要含有Ni、Sn、Pd及少量Au的成分,成分主体应为(Ni,Au)3Sn4。a#、b#样品中金属间化合物的分布基本一致,金元素含量也基本一致。这表明:在混合集成电路内引线柱镀金层厚度在1.3~2.5 μm的情况下不进行搪锡去金处理,直接用Sn62Pb63Ag2焊料进行再流焊形成的焊接结构基本一致且能够通过GJB2438A——2002规定的QML条件下的环境试验考核。

图7 a#样品SEM 照片和EDS分析数据

图8 b#样品SEM 照片和EDS分析数据

4.1.3 极端试验

选择c#、d#、e#样品按照4.1节相同的方式组装样品并完成表4规定的试验项目,其中温度循环试验的循环次数增加至500次。经历极端试验条件后,在30~50倍体视显微镜下对引线柱焊接结构形貌进行观察,具体形貌如表4所示。引线柱焊点在极端环境试验应力作用下发生明显粗化,但焊接界面无开裂等受损迹象;对焊接界面进行剖面并用500倍金相显微镜观察焊接界面,引线柱-焊料-铜环各块体材料结构完整,界面无开裂等受损现象。

综合本节分析可以得出:高可靠厚膜HIC组装过程中,对镀金引线柱(金层厚度为1.6~2.41 μm)不进行搪锡去金而直接采用Sn62Pb36Ag2焊料进行软钎焊得到的焊接结构,能够通过GJB2438A——2002规定的环境试验分组考核,并且可靠性裕度较高。

4.2 长期使用可靠性评估试验

4.2.1 金镀层厚度为1.6~1.83 μm试验

选择某空间项目用厚膜混合集成电路样品,引线柱金镀层厚度为1.6~1.83 μm,焊接结构与4.1节相同。按电路详细规范筛选合格后进行125 ℃、满载2 000 h加电老炼试验合格,然后进行表3中的机械冲击试验,试验结束后电测试合格。将试验后的样品在30~50倍体视显微镜下对引线柱焊接结构形貌进行观察,引线柱区域的焊接形貌正常,焊点在长期高温作用下发生粗化,但焊接界面无开裂等受损迹象。

表4 环境试验后引线柱焊点外观和剖面形貌

Tab.4 Sectional views of soldered pins after environment tests

将镀金层厚度为1.6 μm的引线柱焊接样品编号为f#,镀金层厚度为1.83 μm的引线柱样品编号为g#。将f#和g#样品进行剖面-腐蚀,用金相显微镜观察的形貌如图9所示,样品焊接结构各块体材料结构完整,引线表面的Au层已完全熔入钎料中,焊接界面区域结合良好、致密,无界面开裂情况。

图9 样品剖面形貌照片

选择g#样品的焊接结构使用Hitachi S4300型扫描电子显微镜进行SEM & EDS分析,结果如图10所示。

图10 g#样品焊接界面的SEM照片和EDS分析

通过图10可以看出:引线柱镀金层已经完全熔解在钎料中,在Ni-P层与钎料的反应产物层含有Ni、Sn及Au的成分,Au元素在经历长期高温处理后发生了“洄游”现象,阻挡层中的Ni元素也不断参与金属间化合物继续扩散生长,导致(Ni,Au)3Sn4生成物层厚度生长至约10 μm。但Au-Sn金属间化合物未发现有明显的积聚和突出生长,也未见其成层状分布。样品的焊接界面强度能够承受14 700 m/s2的机械冲击,且未出现因金属间化合物的脆化导致开裂的情况。

4.2.2 金镀层厚度为1.8~1.97 μm试验

选择某长期可靠性验证工程的代表品种厚膜HIC,引线柱镀层厚度范围为1.8~1.97 μm,按照详细规范筛选合格后,进行125 ℃、21 900 h(2.5年)高温烘焙后进行电测试合格,然后进行表4所示的机械冲击试验,试验结束后电测试仍合格。将该样品在30~50倍体视显微镜下对引线柱焊接结构形貌进行观察,引线柱区域的焊接形貌正常,焊点在长期高温作用下发生明显粗化,但无开裂等受损迹象。

将镀金层厚度为1.8 μm的引线柱焊接样品编号为h#,镀金层厚度为1.97 μm的引线柱样品编号为i#。将h#和i#样品进行剖面-腐蚀,用金相显微镜观察的形貌如图11所示,样品焊接结构各块体材料结构完整,引线表面的Au层已完全熔入钎料中,焊接界面区域结合良好、致密,无界面开裂情况。

图11 样品剖面形貌

选择i#样品的焊接结构使用Hitachi S4300型扫描电子显微镜进行SEM和EDS分析,结果如图12所示。

从图12中可以看出,(Ni,Au)3Sn4生成物层厚度增长至20 μm左右,在Ni-P层表面还生成了一层较薄的Ni-Sn合金层。Au-Sn金属间化合物未发现有明显的积聚和突出生长,也未见其成层状分布。样品的焊接界面强度能够承受14 700 m/s2的机械冲击,未出现因金属间化合物的脆化导致开裂的情况。因此,这种焊接结构能够满足GJB2438A——002规定的稳态寿命试验的考核要求,且长期高温条件下工作的可靠性裕度很高。

图12 i#样品焊接界面的SEM照片和EDS分析

5 内引线局部镀薄金界面焊接的可靠性

为了答复国内电装行业诸多专家关于“当镀金层的厚度小于1.27 μm时,使用锡基焊料的软钎焊工艺不会产生“金脆”,可以不用进行去金处理”的关切,43所圣达公司开发了一套对金属管壳内引线局部镀薄金的工艺,金层厚度稳定控制在0.5~1 μm并且实现批产应用;外引线仍满足GJB2440A——2006规定的“(外)引线和引出端的镀金层厚度应为1.3~5.7 μm”的要求。

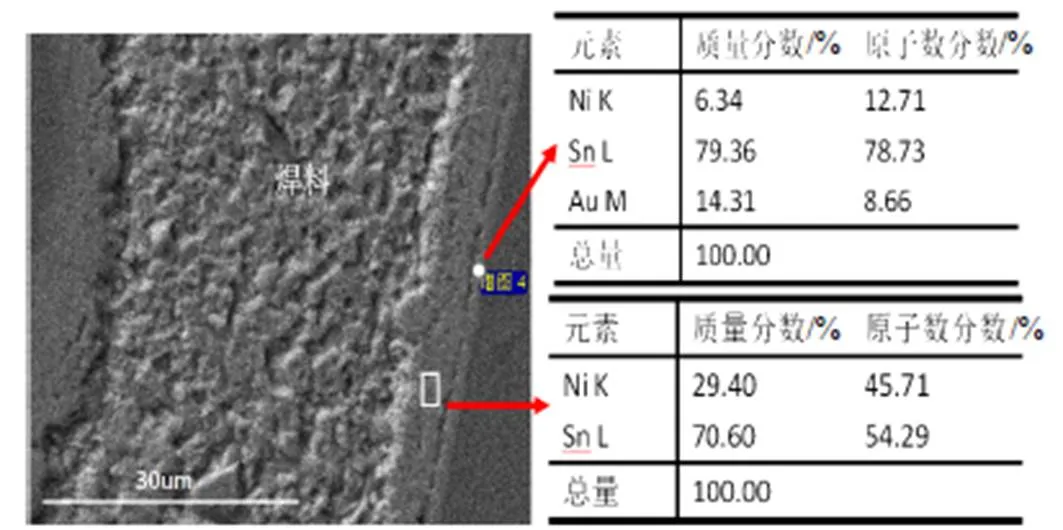

选择局部镀薄金工艺的管壳样品重复进行本文4.1节的试验,试验结果表明: 在温度循环试验次数增加至500次的情况下,局部镀薄金工艺样品的焊接结构表现与4.1节基本一致,焊接界面结合良好、致密,无界面开裂情况。将局部镀薄金工艺的样品进行125 ℃、2 000 h稳定性烘焙后对焊接界面进行进行SEM和EDS分析,结果如图13所示。

图13 局部镀薄金内引线柱样品125 ℃,2 000 h后焊接界面的SEM照片和EDS分析

薄金焊接界面的Ni-P层表面形成1 μm左右的Ni-Sn反应层以及5 μm左右的Ni-Sn-Au生成物层,未发现有明显的Au-Sn金属间化合物积聚和突出生长。(Ni,Au)3Sn4生成物层的厚度只有图10中生成物厚度的一半,这是由于焊接过程中参与反应的金含量大幅降低,所以对(Ni,Au)3Sn4的生长以及金元素的“洄游”现象起到了明显的抑制作用,虽然经历长期的高温处理,金元素在焊料中仍然以很低的含量均匀分布。因此,在薄金界面进行锡基焊料软钎焊工艺的可靠性更高。

局部镀薄金工艺既保证了厚膜HIC内引线不去金焊接的可靠性,又满足了整机和分机用户在使用HIC过程中对外引线柱部分反复插拔等工况对镀层强度的要求,可以作为一种高可靠HIC镀金引线柱不去金焊接的优选工艺。

6 结论

(1)混合集成电路行业标准没有对镀金界面的锡基焊料软钎焊工艺提出去金的要求,国内、外主流厚膜混合集成电路生厂商也没有执行这一要求。

(2)高可靠厚膜HIC的工艺结构与电装行业通用的高等级PCB板电路有很大区别,前者受温度循环应力的影响更小,失效风险更低。

(3)高可靠厚膜混合集成电路引线柱镀金层厚度在1.3~2.5 μm情况下,采用Sn62Pb36Ag2焊料直接进行焊接得到的结构,其焊接界面强度以及高温条件下的长期可靠性完全能够满足军标要求且可靠性较高。

(4)采用局部镀薄金工艺(内引线柱金层厚度为0.5~1 μm)的管壳能够对焊接界面(Ni,Au)3Sn4的生长以及金元素的“洄游”现象起到明显的抑制作用,可靠性更高。该艺可以作为一种高可靠HIC镀金引线柱不去金焊接的优选工艺。

[1] TAMMANN G, ROCHA H. The diffusion of two metals into one another with formation of intermetallic compounds [J]. Z Anorg Chem, 1931(1): 199-289.

[2] CIULIK J, NOTIS MR. The Au-Sn phase diagram [J]. J Alloy Compd, 1993, 191: 71-74.

[3] HUSTED B, BUENE L, FINSTAD T, et al. Interdiffusion and phase formation in Au/Sn thin film coupules with special emphasis on substrate temperature during condensation [J]. Thin Solid Films, 1982, 98: 81-86.

[4] NAKAHARA S, MCCOY R J. Interfacial void structure of Au/Sn/Al metallization on Ga2Al2As light-emitting diodes [J]. Thin Solid Films, 1980, 72: 457-461.

[5] MINOR A M, MORRIS J W. Inhibiting growth of the Au0.2Ni0.5Sn4intermetallic layer in Pn-Sn solder joints reflowed on Au/Ni metallization [J]. J Electron Mater, 2000, 29(10): 1170-1174.

[6] USA MIL. MIL-STD-2000A Standard requirements for soldered electrical and electronic assemblies [S]. USA: [s.n.], 1991.

[7] USA MIL. IPC/EIA J-STD-001B Requirements for soldered electrical and electronic assemblies [S]. USA: [s.n.], 1996.

[8] EU. ECSS-Q-ST-70-08A The manual soldering of high-reliability electrical connections [S]. Noorduijk, The Netherlands: ESA-ESTEC, 1999.

[9] EU. ECSS-Q-ST-70-18A Preparation, assembly and mounting of coaxial cables [S]. Noorduijk, The Netherlands: ESA-ESTEC, 2001.

[10] 国防科学技术工业委员会. QJ 3267-2006电子元器件搪锡工艺技术要求[S]. 北京: 中国标准出版社, 2006.

[11] 国防科学技术工业委员会. GJB2438A-2002混合集成电路通用规范[S]. 北京: 中国标准出版社, 2002.

[12] 国防科学技术工业委员会. GJB2440A-2006 混合集成电路外壳通用规范[S]. 北京: 中国标准出版社, 2006.

[13] 国防科学技术工业委员会. GJB548B-2005微电子器件试验方法和程序[S]. 北京: 中国标准出版社, 2006.

[14] 中国航天科技集团公司. Q/QJA 20085-2012宇航用混合集成电路通用规范[S]. 北京: 中国标准出版社, 2012.

[15] 李晓麟. 试论电子装联禁(限)用工艺的应用[C]//2009中国高端SMT学术会议论文集. 成都: 四川省电子学会, 2009: 112-115.

(编辑:陈渝生)

Study on gold plating pins directly soldering using Sn-base solder in thick film HIC

LIU Junfu, ZHENG Jin

(China Electronic Technology Group Cooperation No.43 Institute, Hefei 230088, China)

There is always existing dispute for the standards of pretinning and degolding before soldering on gold plated interface with Sn-base solder in electronic package industry. Using SEM and stereo microscope, etc. to study the gold plated pins’ soldering process (without pretinning and degolding) with Sn-base solder when assembling the high-reliable thick film hybrid integrated circuit (HIC). Results show that the pins soldering surfaces with typical gold plating thickness(1.3-2.5 μm) could pass a series of environment tests and high temperature-long term storage tests. Samples with thin gold plating thickness(0.5-1 μm) on inner pins could restrain the Ni-Au-Sn intermetallic compounds' synthesis more effectively, it should be given to this kind of packages for high reliable HIC.

hybrid integrated circuit; gold plated pin; Sn-base solder; gold embrittlement; pretinning; soldering

10.14106/j.cnki.1001-2028.2016.07.020

TN452

A

1001-2028(2016)07-0084-07

2016-06-12

刘俊夫

刘俊夫(1984-),男,河北承德人,工程师,研究方向为混合微电子技术,E-mail:liujunfu0110@163.com 。

2016-07-01 10:50:52

http://www.cnki.net/kcms/detail/51.1241.TN.20160701.1050.019.html