一种变温变掺杂流量的埋层外延生长方法

2016-03-22赵建君肖建农马林宝

赵建君,肖建农,马林宝

(南京国盛电子有限公司,南京 211111)

一种变温变掺杂流量的埋层外延生长方法

赵建君,肖建农,马林宝

(南京国盛电子有限公司,南京211111)

摘 要:在已经制作有埋层的衬底上生长外延层,为了控制图形畸变和漂移而选取了较高的工艺温度,导致了严重的自掺杂。通过对比实验探讨了常用的双层外延工艺和变温变掺杂流量工艺对于抑制自掺杂的效果。在一定的埋层掺杂浓度范围内,需要采用变温变掺杂流量工艺,才能使外延层纵向载流子浓度分布(SRP)满足器件要求。

关键词:埋层外延;变温变掺杂流量;纵向载流子浓度分布(SRP)

1 引言

在常见的双极型晶体管的生产工艺中,通常需要在已经制作有埋层的衬底上生长外延层。以NPN型双极晶体管为例,采用P型<111>中阻衬底,为了降低集电极串联电阻,需要在衬底上做N +埋层(通常扩Sb),同时还要做P 型埋层(下隔离,掺B),然后生长N型外延层,再在外延层上实施P型注入(上隔离),通过上下隔离相接来实现对通隔离。与光片外延相比,这种埋层外延存在着图形漂移与畸变及自掺杂严重的问题,需要有针对性地采用特殊工艺。

在衬底表面,制作埋层的区域构成一定的图形。这种图形会随着外延生长在外延后的表面形成整体的平移,称为图形漂移。图形本身也会放大或者缩小,称为图形的畸变。漂移和畸变的量需要控制在一定范围内以满足后道工序的要求,这是工艺上的一个难点。此外,由于外延之前衬底上已经制作有埋层,埋层中的杂质会在外延过程中挥发出来形成自掺杂,严重影响外延层的电阻率和纵向载流子浓度分布(SRP)曲线形貌,从而导致器件参数的恶化乃至失效。自掺杂的控制是另一个难点。由于Sb的自掺杂程度比B小,因此主要是解决B的自掺杂影响,而对Sb的自掺杂可以不予考虑[1]。

2 技术要求

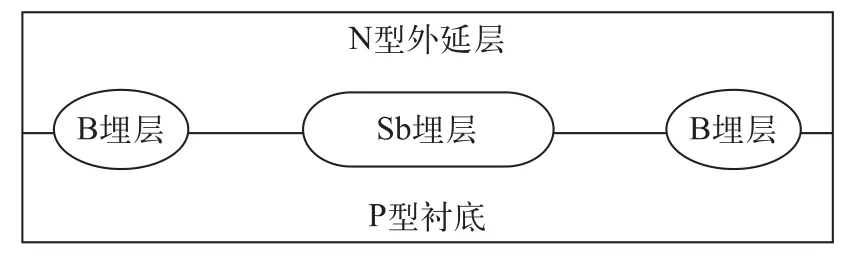

本文所描述的埋层外延片,采用衬底为P<111>(8~13 Ω·cm)中阻衬底扩Sb埋层和B埋层,B埋层区域方块电阻为90 Ω/□,外延层为N型,平区电阻率要求7 Ω·cm,厚度18.5 μm。其结构如图1所示。

图1 埋层外延片结构示意图

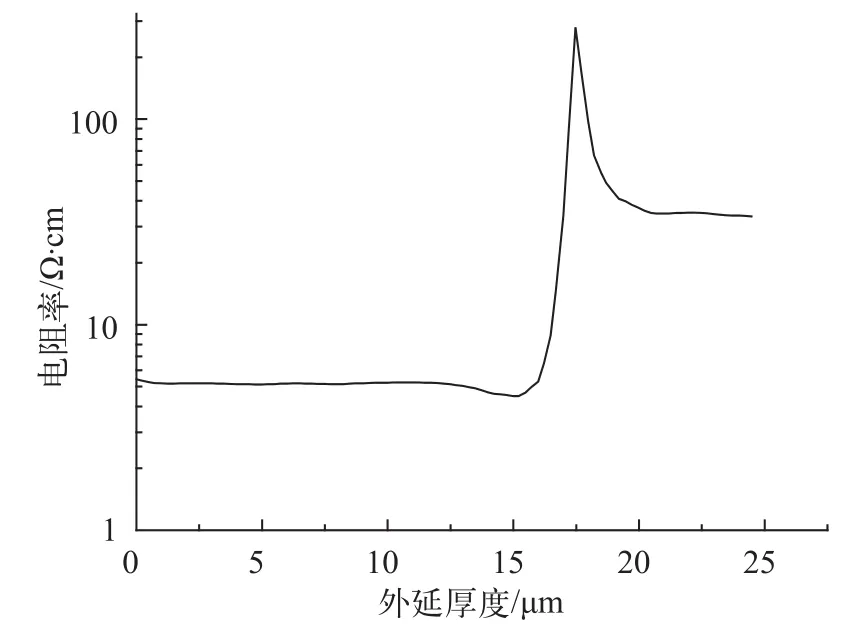

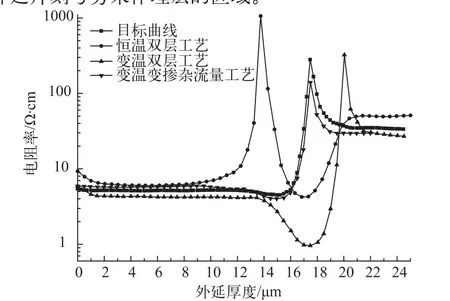

基于后道工序的要求,埋层区域的图形漂移率需要控制在0.9±0.1范围内。无埋层区域的纵向载流子浓度分布曲线要求如图2所示,要求在邻近衬底的外延区域直接形成PN结实现外延类型的反型,之后形成N型外延的平区直至外延层表面。图中右侧为P型衬底区域,中间是代表PN结的尖峰,左侧为N型外延区域。

图2 无埋层区域的纵向载流子浓度分布要求曲线

考虑到生产成本,选择单炉出片量较多的意大利LPE公司的LPE-2061S型桶式外延设备进行加工,生长方式为常压CVD法;硅源为三氯氢硅;埋层片装在桶式基座的侧面;测试采用Nanometrics公司的QS2200红外测厚仪在电路片正片上直接测厚度及均匀性,Semilab公司的SSM-495汞探针测试仪监控N型控片表面电阻率,CDE RESMAP168四探针测试仪在与正片同炉生长的P型中阻(8~13 Ω·cm)陪片上测试方块电阻及均匀性,SSM-2000扩展电阻测试系统对外延后埋层片指定区域进行SRP测试分析。

3 外延工艺分析

对于埋层外延,必须保证表面图形的漂移与畸变在一定范围内,否则将引起后道工序的困难。Si的生长和腐蚀速率的各向异性是发生图形漂移或畸变的根本原因。Si外延过程中衬底晶向、反应室压力、生长速率、生长温度、HC1对Si片表面腐蚀量等因素都会对图形漂移或畸变产生影响[2]。由于衬底晶向<111>已经确定,反应室压力固定为1个大气压,因此工艺上可以优化的参数主要为生长速率和生长温度,以及HCl的腐蚀参数。

由于漂移和畸变的量随温度的升高而减小,随淀积速率的增大而增大,因此埋层外延通常选取较高的工艺温度和较低的生长速率[3]。为了去除表面损伤及自然氧化层而得到一个较完整的生长表面,外延前还需要对衬底表面进行一定时间的HCl气相腐蚀。通过实验确定外延生长的工艺温度为1190 ℃,生长速率为0.5 μm/min,HCl气相腐蚀温度1100℃,流量2 slm,腐蚀时间2 min。

由于确定了较高的生长工艺温度,在B埋层掺杂浓度较高的情况下,严重的自掺杂将导致纵向载流子浓度分布曲线严重偏离要求,在靠近衬底表面首先形成高浓度的低阻P型区域,然后形成PN结,再形成N型外延平区。低阻P型区域在纵向载流子浓度分布曲线图中表现为在PN结尖峰右侧出现凹坑。这种低阻P型区域的存在会导致BVce_lpnp偏小以及饱和压降增大,必须采取措施予以消除。可以采取的措施主要是在开始外延的最初一小段时间内降低工艺温度和加大N型掺杂剂量。温度越低,自掺杂越小;而已经生长的外延层能够阻挡埋层中的杂质在外延过程中的挥发,随着外延厚度增加,自掺杂也会迅速减小,因此降低外延开始的最初一小段时间内的工艺温度,可以明显减小自掺杂的总量,而整个外延时间段的大部分保持高的工艺温度,又不会显著影响漂移率。同时在外延开始时加大N型掺杂的剂量,使外延层尽快实现反型,从而避免低阻P型区域的出现。

常用的工艺方法是恒温双层生长方法,即先生长低阻内层再生长高阻外层,工艺温度保持不变[4]。这种方法适用于埋层掺杂浓度较低的情形(方块电阻≥120 Ω/□)。当埋层掺杂浓度较高时(方块电阻<90 Ω/□),需要采用变温双层生长方法,即降温生长低阻内层、再高温生长高阻外层的方法。在两者之间的浓度区域,仅靠低阻内层已经不能满足要求,必须采用变温生长工艺,但是采用变温双层生长方法又容易在PN结反型之后出现低阻N型区域。为此采用了变温同时变掺杂流量的外延生长方法,在外延起始时设定较低的生长温度和较高的掺杂流量,然后逐步提高生长温度同时降低掺杂流量,直至达到主工艺温度和外延平区对应的掺杂流量,之后固定工艺温度和掺杂流量直至生长结束。通过调节合适的温度和掺杂流量的变化速率,实现要求的纵向载流子浓度分布。

4 结果与讨论

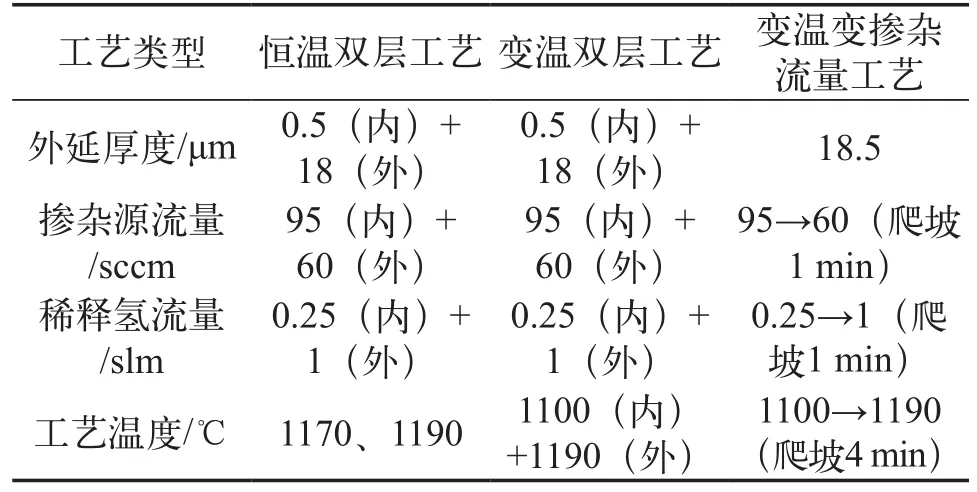

通过工艺对比试验研究了3种工艺的不同结果,工艺条件如表1所示。

表1 外延工艺条件对比列表

试验统一采用300×10-6浓度的磷烷作为掺杂源。通入反应腔的掺杂气体需要经过氢气稀释和排外过程,因此除了直接降低掺杂源钢瓶输出的掺杂源流量外,增加稀释氢气的流量可以进一步降低实际通入反应腔的掺杂流量。变温变掺杂流量工艺中掺杂流量和工艺温度开始时以恒定速率爬坡,爬坡过程结束后一直稳定在爬坡终止条件上直到生长结束。

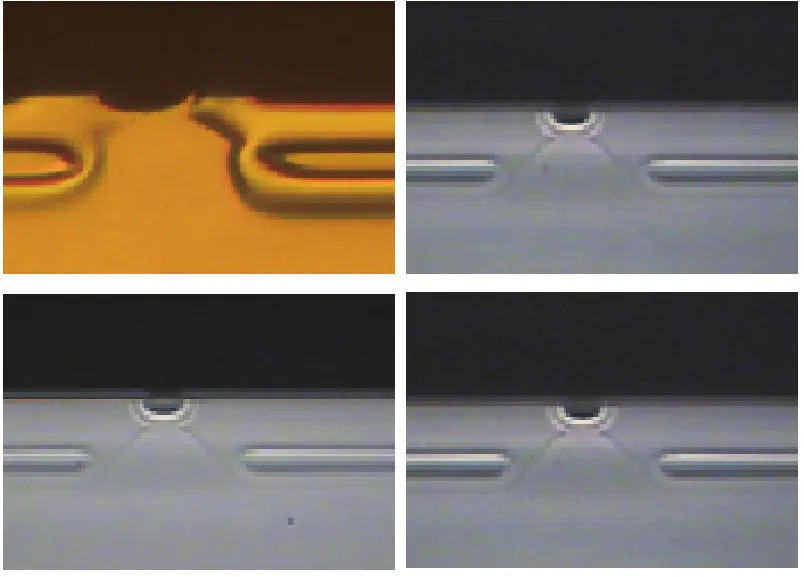

图3是1170℃恒温双层工艺和末温1190℃的3种工艺的图形漂移显微图片,显示的是显微镜拍摄的晶片垂直表面切开后的断面。

图3中左上、右上图分别是1170℃和1190℃恒温双层工艺生长的图形漂移显微图片,图中央深色半圆形区域就是后道工序制作的注入层,要求与外延层中图形边缘间隙区域正对。由图可知在1170℃下图形漂移与后道工序不匹配,注入层偏在左侧,而1190℃下的图形漂移基本满足要求。左下、右下图片分别是末温度1190℃下变温双层和变温变掺杂流量工艺的图形漂移图片,与1190℃恒温双层工艺的图形漂移基本一致,这表明较低的起始温度基本没有影响图形漂移。

图3 1170℃低温生长和1190℃3种工艺的图形漂移图

图4是末温度1190℃时3种工艺条件下生长的外延片的纵向载流子浓度分布图,测试位置位于埋层外延片刻号旁未作埋层的区域。

图4 末温度1190℃时3种工艺条件的纵向载流子浓度分布对比图

从图中可以看出,采用恒温双层工艺生长的外延层出现了低阻P型区域,表明仅仅内层加大掺杂流量难以有效抑制B的自掺杂,而变温双层工艺生长的外延层在形成PN结后出现低阻N型区域,在图4中表现为PN结尖峰左侧出现凹坑。减小变温双层工艺的内层厚度固然可以减小N型凹坑,但需要将内层厚度减小至明显小于0.5 μm的水平。此时受生长速率的波动影响较大,对B自掺杂的抑制能力存在明显波动,难以实现稳定的参数控制。采用变温变掺杂流量工艺生长的外延层则较好地满足了要求,与目标曲线符合得很好。

综上分析,1170℃低温生长时图形漂移与后道工序不匹配,而1190℃恒温双层工艺和变温双层工艺虽然图形漂移符合要求,但是SRP曲线不符合要求。只有1190℃下变温变掺杂流量工艺同时符合两个要求,是适合制备这种器件的唯一工艺。

5 结论

在制作有埋层的硅片上生长外延层,需要抑制埋层杂质挥发形成的自掺杂。在一定的埋层掺杂浓度范围内(方块电阻约90~120 Ω/□),常用的双层外延工艺难以满足要求,需要采用变温同时改变掺杂流量的工艺。通过实验证明选取合适的参数,变温变掺杂流量工艺能够有效抑制自掺杂,使外延层的纵向载流子浓度分布满足器件要求,同时也兼顾了图形漂移的要求。

参考文献:

[1] 席奎德.对通隔离中硼自掺杂的影响[J].半导体技术,1986,3: 9-10.

[2] 赵丽霞,张鹤鸣. 硅外延过程中图形漂移的研究[J]. 微纳电子技术,2009,11: 691-694.

[3] 衣贵诚. 硅外延淀积过程中埋层图形漂移的测量[J]. 微电子学与计算机,1989,5: 35-36.

[4] Wang Yinhai, Zhao Jianjun,Luo Hong, Ma Linbao. Process Control of Buried Layer Epitaxy by Barrel Type Furnace[J]. Materials Science Forum(0255-5476),2015, 815: 3-7.

赵建君(1983—),男,江苏江阴人,四川大学物理科学与技术学院硕士研究生,南京国盛电子有限公司工程师,主要研究方向是硅外延工艺。

A Buried-layer Epitaxy Technology by Varying Temperature and Doping Flow

ZHAO Jianjun, XIAO Jiannong, MA Linbao

(Nanjing Guo Sheng Electronic CO.,LTD, Nanjing 211111,China)

Abstract:High deposition temperature was applied to suppress pattern shift and distortion in the epitaxy process on buried Si substrate. However, auto doping was introduced because of the high deposition temperature. The comparison experimental results on suppressing auto doping were discussed between two epitaxy processes: two-step epitaxy and process by varying temperature and doping flow. Epitaxy Process by varying temperature and doping flow should be applied when the concentration of buried layer was in a certain range. The vertical carrier concentration profile (SRP) of corresponding epitaxy layer could satisfy the device demands.

Keywords:buried-layer epitaxy; varying temperature varying doping flow; spreading resistance profiles (SRP)

作者简介:

收稿日期:2015-8-12

中图分类号:TN 305.5

文献标识码:A

文章编号:1681-1070(2016)01-0034-04