基于FPGA的多速率信号发送器的设计

2016-03-17韩朝辉孟令军

韩朝辉,孟令军,邹 坤

(中北大学 仪器科学与动态测试教育部重点实验室 电子测试技术国家重点实验室,太原 030051)

基于FPGA的多速率信号发送器的设计

韩朝辉,孟令军,邹坤

(中北大学 仪器科学与动态测试教育部重点实验室 电子测试技术国家重点实验室,太原030051)

摘要:针对传统多速率信号发送器信号的非线性失真大、可调性差等问题,文中提出了一种基于FPGA与DAC5682的新型的设计方案;方案中着重介绍了DAC5682数模转换模块的实现方式以及多速率信号处理算法的实现;DAC模块可以同时实现4通道的数模转换,采样率可以达到1 Gsps;同时,为了验证FPGA算法设计的可靠性,文中首先通过MATLAB平台对算法进行了仿真建模分析;然后通过硬件描述语言将算法移植到FPGA电路上,在modelsim中实现了综合后仿真;最后给出了仿真波形;通过仿真验证,发送器具有良好的滤波效果,并可根据实际需求灵活的对基带频率以及变换后的混频模块进行相应的变换和升级;通过FPGA+DAC的设计,简化了系统结构,还能较为高效的实现系统中的各项技术指标;该系统可以广泛应用与移动通信系统中。

关键词:FPGA;DAC5682;多速率; 信号处理

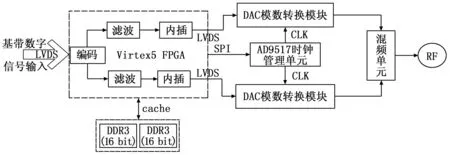

图1 系统组成结构

0引言

随着信息化时代的高速发展,通信已经变成人们日常生活中不可缺少的一部分。而通信领域中,多速率信号发送器是其较为重要的一部分。在实际信号采样设计中,设计者希望用尽可能高的采样率来降低系统的信噪比。同时,在信号处理和编码时,又希望只处理有效的信号频段,使信号速率尽可能地低,最后在D/A转换时又需要较高的采样率来还原信号,抑制信噪比。这三者看似矛盾的需求,而在多信号处理的技术下能够很好地融合为一个整体,通过插值和抽取来满足任意信号速率的转换需求。目前,多速率信号发送器已广泛用于移动通信系统中,而且随着通信技术的与日俱进,将来还会有更为广阔的应用前景。

1多速率发送器组成及基本原理

传统的设计方案是将基带信号通过DAC转换成模拟信号,然后在模拟电路的基础上经过滤波、放大、混频调制,将信号通过功率放大后发射出去。这种方案由于过多地使用了模拟电路,可能会使电路产生较大的非线性失真。同时模拟电路还不可调整,会对系统的升级和调整有一定的影响。

通过对传统设计方案的改进,文中设计了一种基于FPGA的多速率信号发送器。系统硬件组成结构如图1所示。系统主要由基带信号的处理(FPGA实现)、DAC数模转换模块、RF信号发送模块组成。

图2 DAC电路设计原理图

系统基本工作原理:基带信号通过LVDS接口方式传送到FPGA上[1],FPGA通过自身丰富的IP核和DSP48资源对数字信号进行信道编码和滤波处理,然后将处理后的数字信号经过DAC模数转换。方案中使用的DAC芯片为TI公司的DAC5682Z,由于系统对时钟有较严格的要求,所以这里加入了一个时钟管理芯片AD9517。FPGA通过SPI方式配置AD9517使其输出合适的时钟到DAC模块,利用DAC5682Z内部的插值滤波器以及混频模块将数字信号变换成所需要的频带信号然后再进行数模转换[2]。转换后的模拟信号经过混频变成射频信号,最终通过RF射频[3]模块将信号发送出去。(由于传输过程中数据量较大,这里设置了一簇DDR3高速缓存单元。该单元由两片镁光公司推出的16 bit的MT41J128M16组成,系统传输总线可达到32位,数据传输速率可以达到500 mbps。)

2DAC数模转换模块的设计

2.1硬件平台的设计

方案中使用了两片TI公司的16位1GSPS的双通道DA转换芯片DAC5682。可以同时现实4通道的数模转换。DAC5682Z是一款高速的双通道16位的D/A转换芯片,其采样速率可达到1Gsps。其内部包括4个处理部分:输入FIFO、2X/4X插值滤波器、Fs/4混频器和双路16bit的数模转换器。方案中使用FPGA对其进行参数配置,配置使用标准的SPI接口。图2为其中一片DAC模块的电路设计原理图。

电路设计中的关键问题:

1)由于数模转换模块的输入端口的数据电平标准为LVDS(low-voltage differential signaling)。因此在实际PCB的布线设计时,要等长,并且走线尽可能的离目标器件近。

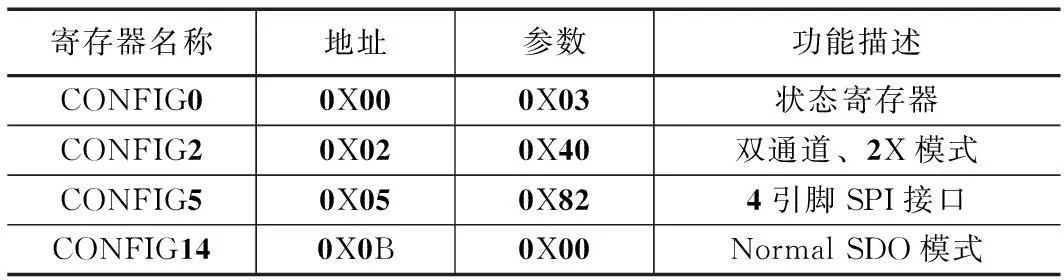

2) DAC芯片的内部寄存器的配置使用的是标准的4总线的SPI接口模式,电平标准为LVTTL33。设计时可以将其直接连接到FPGA相应的GPIO管脚上。程序设计中SCLK通过FPGA内部的DCM分频到10 MHz,通过SDIO、SDO信号线实现对DAC芯片的初始化配置。表2.1为DAC芯片几个重要寄存器的配置信息。

表1 DAC5682芯片寄存器定义

3)在DAC转换完成后的模拟信号通过变压器进一步的隔离,可以更好地防止噪声信号的干扰。同时,在模拟电路部分的PCB设计中,严格按照对称等长的原则进行布线。

2.2DAC模块与FPGA接口逻辑的设计

DAC5682芯片数据输入端为16位的高速LVDS信号接口(DP/N[15:0]),内部连接一个数据FIFO缓冲单元。数据输入分为单通道和双通道模式。在双通道模式下,数据进入FIFO后,由时钟的上升沿和下降沿分别采集数字量信号。采集到的I路数据和Q路数据分别进入A/B通道实现双路数模装换。图3为DAC工作时序图。

图3 DAC5682模数转换时序图

Xilinx公司的Virtex5系列FPGA有丰富的LVDS接口可以满足设计需求,同时,FPGA内部的ODDR模块可以完美的实现双边沿采样数据。图4为FPGA内部ODDR模块的结构图。

其中C为时钟输入口,数据D1和D2分别在时钟C的上升沿和下降沿输入,CE为时钟使能信号,R为复位信号,S为置位信号。

DAC5682芯片的时钟通过专用的时钟管理模块ADC9517提供。该模块可以同时稳定输出4路LVDS时钟信号,频率最高可以达到1.6 GHz。满足设计需求。

图4ODDR模块示意图

3FPGA算法设计与实现

3.1多速率信号发射器的算法设计

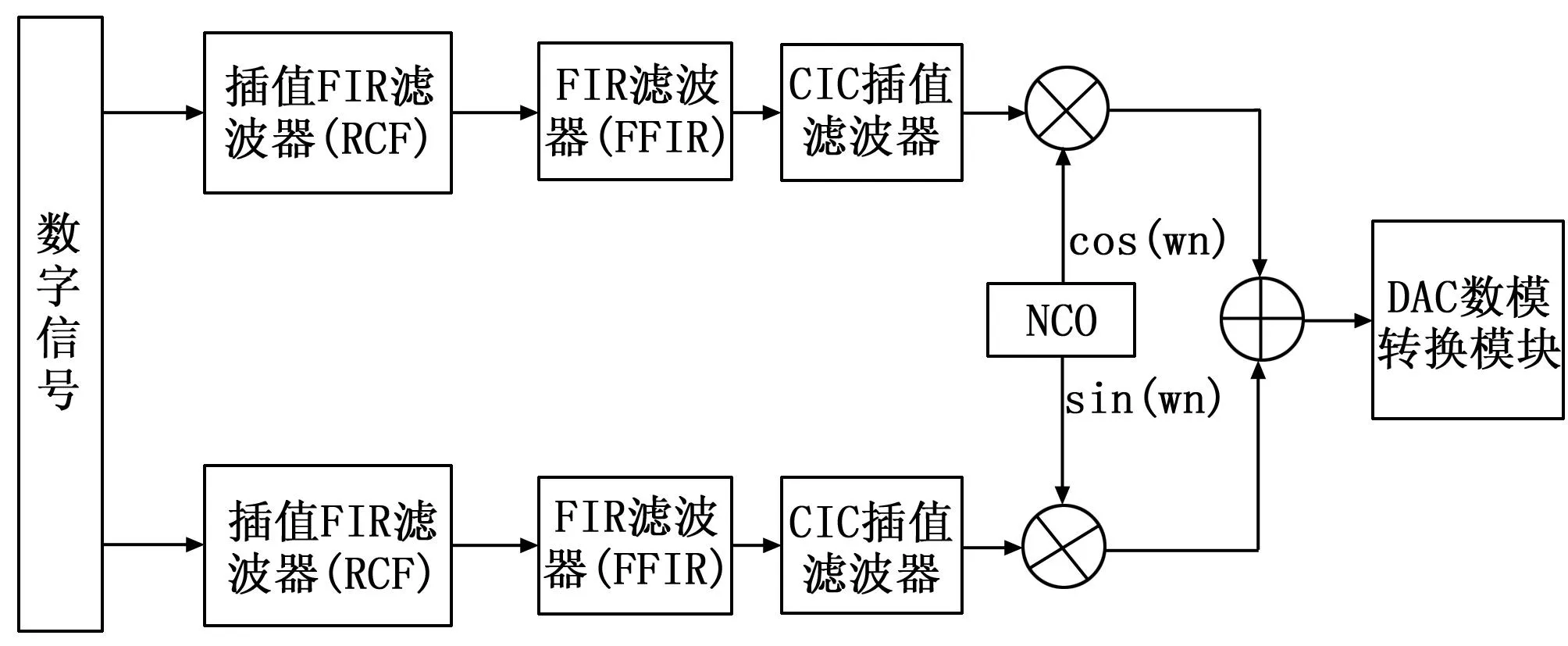

多速率信号发送器的系统结构如图5所示。其中在DAC工作之前,主要由4部分级联组成[4]:可编程的插值FIR滤波器(RCF)、两个固定系数的FIR滤波器(FFIR)、高速的CIC插值滤波器及数控频率振荡器(NCO)。

图5 FPGA实现算法结构图

实际使用中,由RCF完成对输入信号的采样,采样倍数为[1,16],由于工作在高速时钟下,所以其阶数一般不会太高。

FFIR对输入信号进行2倍的采样,如果固定系数滤波器的带宽达到输入采样率的一半,则能较好的抑制带外信号和噪声。

CIC滤波器则一般采用2阶或5阶,完成对输入信号的[1,32]倍的采样。

NCO模块有两部分产生:载波频率和复数乘法器。通过乘法器把基带数据搬到希望的中频上。

3.2多速率信号发送器算法的仿真和分析

3.2.1Matlab的建模与仿真

在FPGA设计实现之前,先通过Matlab工具进行仿真验证。Matlab具有丰富数学应用仿真库[5],通过对库函数的条用,方案中使用了两个滤波器,输入的原始序列为正弦波序列,通过两级滤波器的设计,实现了对原始系列的8倍过采样。图6为Matlab的仿真结果。

图6 Matlab建模仿真图

分析:为了实现原始序列的8倍过采样,需要对序列采样频率进行L=8倍的内插。如果使用单级滤波器实现,则需要的去镜像滤波器的阶数会很大,所以设计中采用了2级的滤波和内插,逐阶的提高采样速度。由于L=8=2×4,所以设计中使用了半带滤波器和CIC滤波器组成。

半带滤波器由于其一般系数为零,大大减少了计算量,提高了计算效率,非常适合在2M倍的插值,为了去掉镜像频率的干扰,这里设计了一个FIR的滤波器,从而实现了原始序列的2倍插值;CIC滤波器滤波系数为1,结构简单,基本组成包括积分部分和梳状部分。同时,作为一种基于零点相消的FIR滤波器,更适合工作在较高的采样率,广泛应用于高速插值系统中,设计中使用的是一个4倍插值的CIC滤波器[6];由于CIC滤波器和半带滤波器的子函数都会带入信号的一些延迟[7],所以从仿真结果可以看出:信号的输出会滞后信号的输入一段时间,但这对于系统的性能影响不大。

3.2.2 多速率信号发送器的FPGA的实现

如图7所示,FPGA实现逻辑主要由以下几个部分组成。基于以上算法结构的设计,通过Verilog硬件描述语言实现信号编码、滤波以及载波输出等逻辑功能[9-10]。

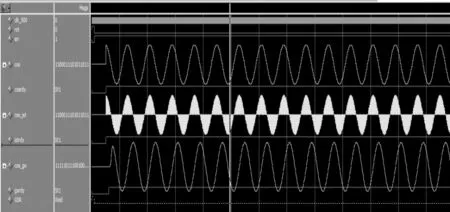

图7 Verilog实现结构图

在Verilog中实现的基本原理:使用的基带信号是250kbps的一个余弦码流,半带滤波器模块实现了一个串行结构的16阶、2倍插值(也就是每一个周期内插入一个零值)、16位位宽的插值滤波器,然后通过CIC滤波器实现内插为4的插值滤波器,滤波器的系数通过MATLAB获得。将CIC滤波器的输出值与载波相乘后输出,从而将基带数据加载到中频上。图8为仿真结果图。

图8 Verilog程序在modelsim中的仿真结果

如图8所示,信号cos是基带码元,信号cos_ist是内插零值后的码元信号,最后经过两级插值滤波器后的输出信号为cos_gx。从图中可以看出,输出的码流信号较为平滑,对于镜像频率的滤波效果明显。因此,该发送器具有较好滤波性能。

4总结

本文主要讨论了无线通信中的多速率信号发送器的设计,通过对理论基础的研究,设计出了一种实现多速率信号发送器的实现方案。

文中的创新点在于:针对传统的设计方法的一些弊端,有针对性的进行了改进。通过使用FPGA+DAC的方式,能够灵活的对基带频率以及变换后的混频模块根据需求进行相应的变换和升级。文中详细描述了DAC模块的电路设计原理以及逻辑编程思路,对于FPGA算法的实现,进行了环路测试[11]。

参考文献:

[1] 田耘,徐文波,张延伟,等.无线通信FPGA设计[M].北京:电子工业出版社,2008.

[2] 蔡光君,任菊.多速率信号处理技术的实现研究[J].太原科技,2009(4):65-66.

[3] 粟欣,许希斌.软件无线电原理与技术[M].北京:人民邮电出版社,2010.

[4] 王映民,等. TD-LTE技术原理与系统设计 [M]. 北京:人民邮电出版社,2010.

[5] 西瑞克斯(北京)通信设备有限公司 无线通信的 MATLAB和FPGA实现[M]. 北京:人民邮电出版社,2011.

[6] 范艳根.CIC 滤波器的 FPGA 实现.黑龙江科技学院学报, 2008,18(3):206-208.

[7] 史学书.软件无线电系统中NCO的设计与实现[J]. 现代电子技术,2005(15):6-8.

[8] 周文安等. 无线通信原理与应用[M]. 北京:电子工业出版社,2012.

[9] 陈议. 基于FPGA的多速率调制解调器的实现[D].西安:西安电子科技大学,2009.

[10] 刘翠海,等. 无线电通信系统仿真及军事应用[M]. 北京:国防工业出版社,2013.

[11] 杜勇,等. 数字通信同步技术的MATLAB与FPGA实现[M].北京:电子工业出版社,2013.

Design of Multi Rate Signal Transmitter Based on FPGA

Han Zhaohui, Meng Lingjun, Zou Kun

(Ministerial Key Laboratory of Instrumentation Science & Dynamic Measurement,State Key

Laboratory for Electronic Measurement Technology, North University of China,Taiyuan030051, China)

Abstract:Aiming at the problem that the traditional multi rate signal is nonlinear distortion, and the adjustable difference, a new design scheme based on FPGA and DAC5682 is proposed. Program focuses on the implementation DAC5682 digital-analog converter module and multi-rate signal processing algorithms. DAC module can achieve 4-channel digital-analog conversion, the sampling rate can reach 1Gsps. Meanwhile, in order to verify the reliability of FPGA algorithm design, paper first platform through MATLAB algorithm for the simulation modeling and analysis; Then the algorithm is transplanted to the FPGA circuit through the hardware description language, and the simulation is realized in Modelsim; Finally, the simulation waveforms are given. Through simulation, the transmitter has a good filtering effect, and the flexibility of the baseband frequency and transformed mixing modules to transform and upgrade based on actual demand. Through the design of FPGA+DAC, the structure of the system is simplified, it can also be more efficient implementation of the technical indicators in the system. The system can be widely used in mobile communication systems.

Keywords:FPGA; DAC5682; multi-rate; signal processing

文章编号:1671-4598(2016)02-0317-04

DOI:10.16526/j.cnki.11-4762/tp.2016.02.088

中图分类号:TN914

文献标识码:A

作者简介:韩朝辉(1989-),男,硕士研究生,主要从事电路与系统方向的研究。孟令军(1969-),男,硕士生导师,副教授,主要从事集成测量系统及仪器、微纳仪器及测试技术方向的研究。

收稿日期:2015-02-27;修回日期:2015-04-27。

邹坤(1990-),男,硕士研究生,主要从事电路与系统方向的研究。