基于ARM+FPGA的PLC计数器的设计

2016-03-17徐晓宇李克俭蔡启仲潘绍明

徐晓宇,李克俭,蔡启仲,潘绍明,余 玲

(1.广西科技大学 电气与信息工程学院, 广西 柳州 545006;2.广西科技大学 鹿山学院电气与计算机工程系, 广西 柳州 545616)

基于ARM+FPGA的PLC计数器的设计

徐晓宇1,李克俭1,蔡启仲1,潘绍明1,余玲2

(1.广西科技大学 电气与信息工程学院, 广西 柳州545006;2.广西科技大学 鹿山学院电气与计算机工程系, 广西 柳州545616)

摘要:计数器是PLC内部重要的软元件之一,在以PLC为核心部件的自动控制系统中,这种软元件通过相应的程序实现系统的实时准确的计数;ARM通过双口RAM发送指令命令给FPGA,FPGA控制计数器进行相关操作,FPGA的晶振工作频率50 MHz作为计数器控制模块的时序约束,设计的计数器具有加减计数功能、断电保持功能、数据回传功能等,以满足PLC控制器的计数需求,并通过使用地址映射存储器使得计数器控制器的指令执行更加高效;设计了计数器与FPGA指令执行控制器的通信协议;通过对设计完成后的仿真与测试,单个计数器的计数频率达到2 MHz,基本实现了PLC计数器的功能,并且达到了稳定计数的设计要求。

关键词:计数器; PLC; 双口RAM; 地址映射存储器; FPGA通信协议

0引言

PLC是一种专用于工业控制的计算机,其基本组成与微型计算机是相同的,都是以微处理器为核心的电子系统,各种功能的实现都是由硬件和软件共同来完成的。但是PLC在硬件、软件结构上,特别是在I/O通道、系统软件、系统RAM和模块化划分等方面又具有自身的特点,与微型计算机有着明显的差异[1]。PLC内部各组成单元之间通过控制总线、地址总线和数据总线等连接,外部则根据实际控制对象配置相应设备与控制装置构成PLC控制系统[2]。

采用ARM-FPGA架构的PLC系统可以很好地融合ARM高速低功耗和FPGA并行工作的优点[3-4]。

在继电控制线路中,计数器是作为一种仪表在电路中使用的,其基本功能是对输入开关量信号进行计数。通过对PLC计数器的运行特点的研究,本设计实现的动态并行执行的计数器控制器,基本满足PLC对计数器种类功能的不同需求,并且可以根据具体工程应用来重构其内部的计数器的总数,实现对FPGA资源的灵活配置。

1功能需求分析和接口电路设计

1.1功能需求分析

PLC内部的计数器一般分为内部信号计数器和高速计数器两种,通常将内部信号计数器简称为计数器。计数器按断电数据保持的情况分为通用型计数器和断电保持型计数器,按加减计数方式分为单增型计数器和加减计数器。同时我们注意到,如果在对计数器执行一些指令时对所有计数器进行操作,降低计数器指令操作的效率。因此设计的计数器控制模块具有以下主要功能:根据PLC的计数器的特点,计数器控制模块设计通用型计数器和断电保持型计数器,同时通用型计数器和断电保持型计数器都拥有单增型和加减型这两种工作方式的计数器;能根据指令执行控制器发送的指令,完成对计数器的初始化配置,完成对计数器状态的更新或修改,完成对计数器的启停、复位等操作,并能读取计数器的当前值;针对计数器控制模块的运行特点,设计相关的结构和功能模块,使其能在执行一些指令时增加其执行效率。

由以上的功能需求分析,确定了计数器的基本功能和实现目标,从而可以确定计数器的体系结构和各个功能模块的配置。

1.2ARM与FPGA接口电路设计

FPGA与ARM之间的数据交换需要存放PLC运行中的各类信息,由于两个端口需要同时对存储器进行访问,选用控制双口RAM来实现。设计的双口RAM是一个具有两个读写端口的存储器,两个端口具有完全独立的数据总线、地址总线和控制总线,并允许两个端口同时对存储器进行访问,其最大的特点是对数据的存储共享。双口RAM的使用可以提高RAM的吞吐率,适用于实时的数据缓存。

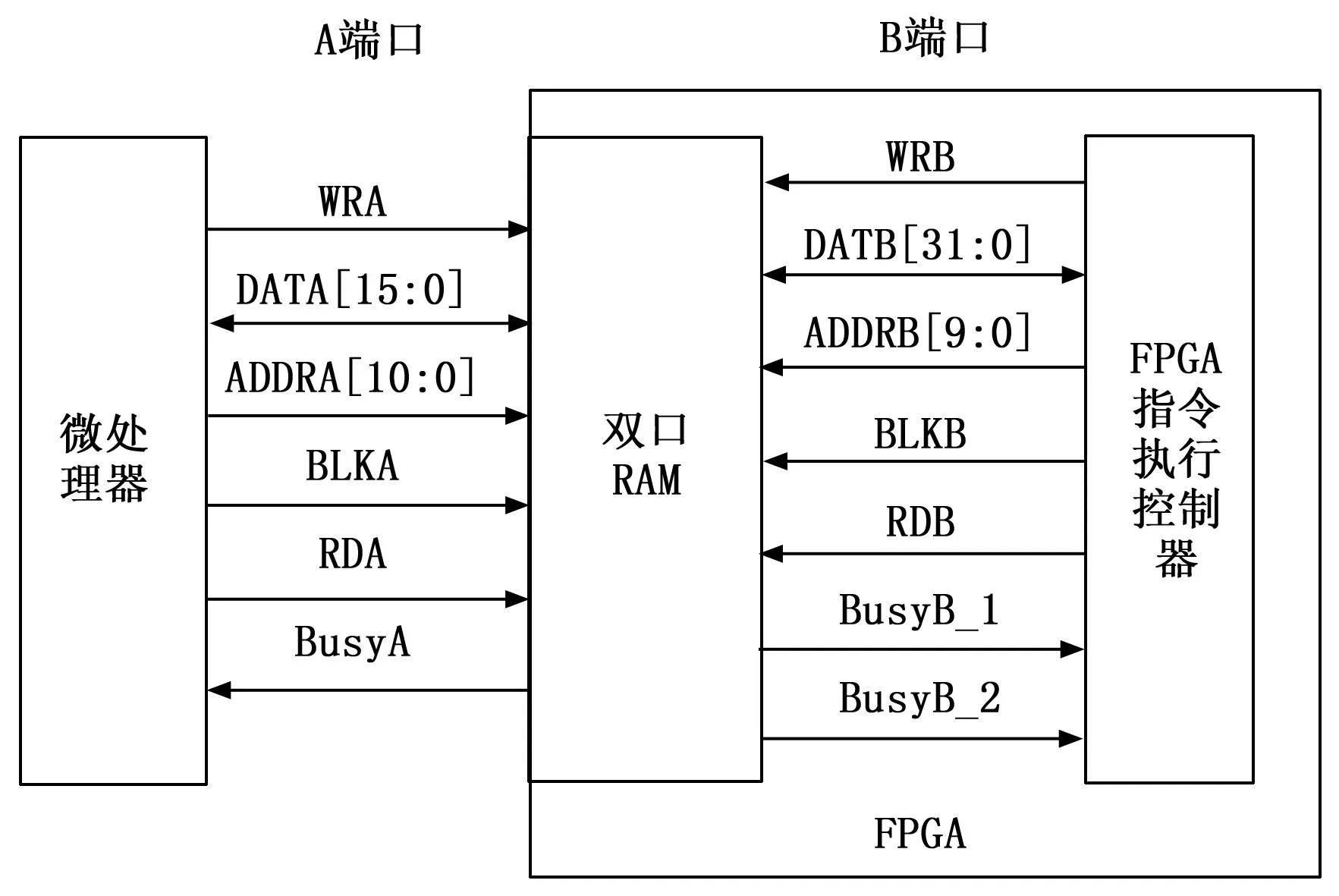

接口控制电路设计为具有仲裁功能的双端口RAM,该双端口RAM与微处理器和FPGA指令执行控制器连接如图1所示。双口RAM的一个端口称为A端口,另一个端口称为B端口。A端口的数据为16位可以与16位微处理器的数据总线直接连接,B端口的数据为32位与FPGA内部的存储读写控制模块的数据总线连接。对于A端口,双口RAM的存储容量为2 K×16,地址总线为ADDRA0~ADDRA10;对于B端口,存储容量为1 K×32,地址总线为ADDRB0~ADDRB9。微处理器通过A端口对1个32位数据的读写操作需要分两次进行。在此设计的双口RAM的地址总线ADDRA、ADDRB,数据总线DATA、DATB,片选线BLKA、BLKBB,读信号线RDA、RDB,写信号线WRA、WRB,忙信号线BusyA和普通双口RAM引脚的功能是一致的。图1中的BusyB_1和BusyB_2分别表示A端口和B端口同时对某一个32位存储单元进行读或写操作时,A端口正在进行低16位或高16位的读或写操作。

图1 双口RAM连接图

2计数器控制器设计

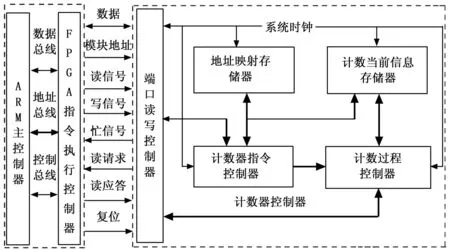

由ARM与FPGA协同构建的PLC控制系统,ARM作为PLC主控制器通过数据总线、地址总线、控制总线向FPGA发送指令命令,FPGA接收到ARM的指令命令之后,通过FPGA指令执行控制器与计数器进行通信,计数器总体结构设计如图2所示,其中包含以下模块:端口读写控制器、地址映射存储器、计数当前信息存储器、计数器指令控制器及计数过程控制器。

图2 计数器总体结构图

2.1地址映射存储器

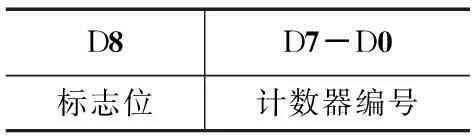

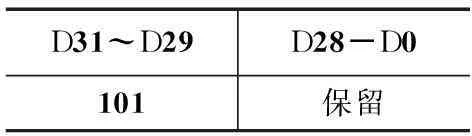

计数器当前信息在相应存储器中的存储位置对应着计数器的编号,即计数器的编号为其相关数据在计数当前值和计数设置值存储器中的地址。为了能够动态执行本设计,使用地址映射存储器按初始化先后存储被使用的计数器的编号,当计数器控制器进行复位或者断电保持型计数器断电后数据上传操作时,从地址映射存储器中的第一个地址开始先后读取被使用的计数器的编号,以此编号为地址,便可以迅速地在计数存储器中找到需要进行操作的计数器的相关数据进行操作。这样就跳过了不需要操作的计数器,从而达到了提高系统执行效率的目的。地址映射存储器的数据格式如表1所示。

表1 地址映射存储器存储数据格式表

2.2计数当前信息存储器

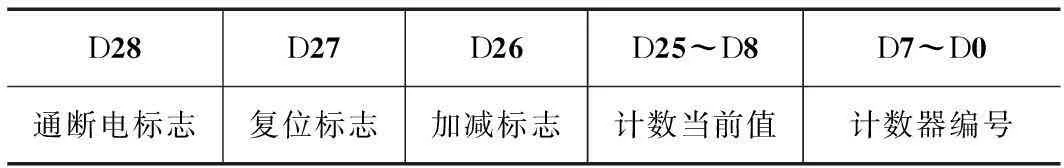

计数当前信息存储器存储数据格式如表2所示,包含计数器编号、计数当前值、加减标志位、复位标志位、通断电标志位等重要信息。

表2 计数当前信息存储器存储数据格式表

计数当前信息存储器使用Libero软件提供的双端口存储器IP核生成,用以实现计数器状态信息、计数相关数据的存储。数器当前值存储器设计为29位,用以存储计数器的当前状态信息、计数当前值和编号信息,计数器的编号即为其相关信息在计数当前值值存储器中的地址。

2.3计数器指令执行器

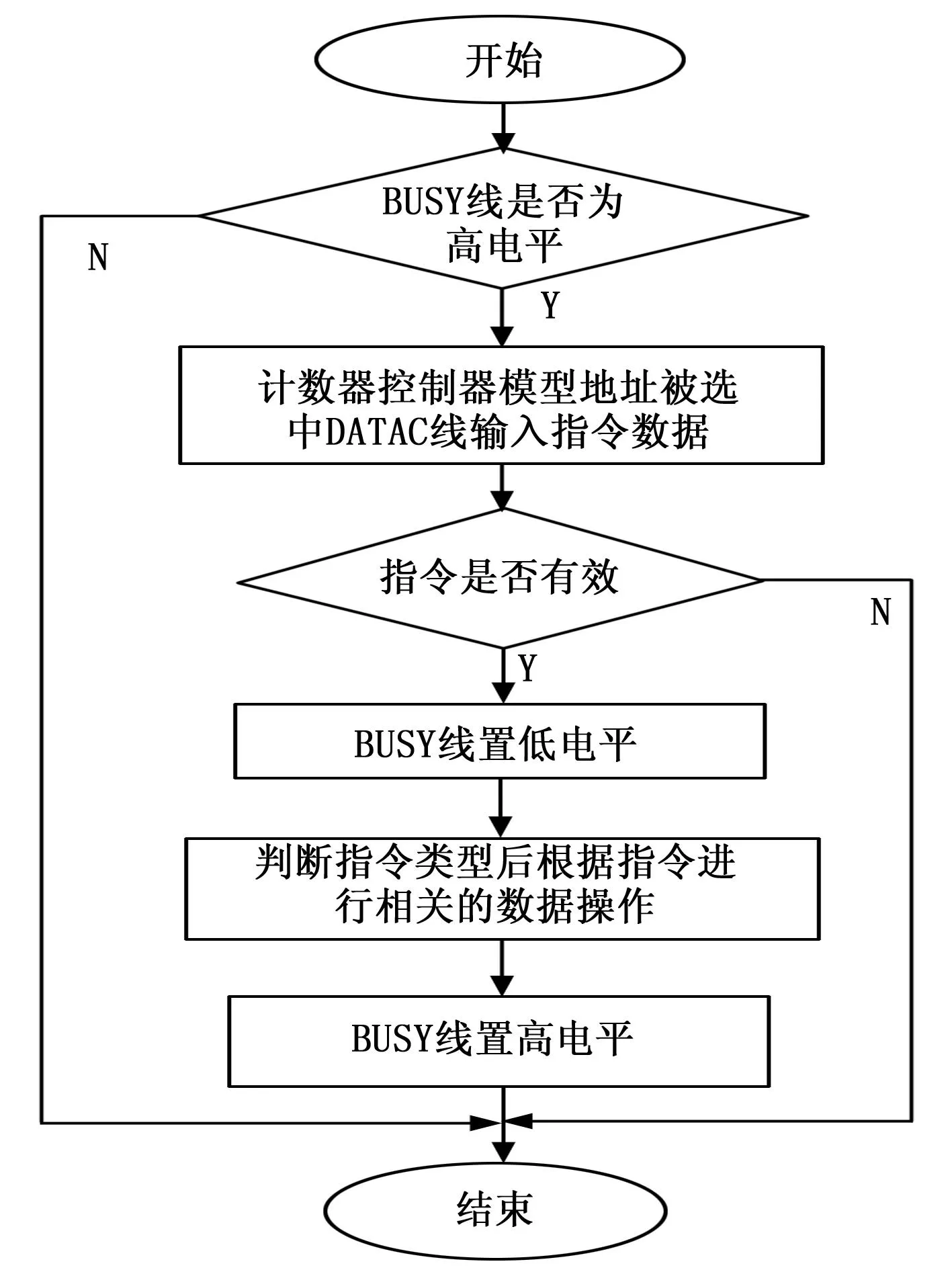

当指令执行控制器对计数器控制器发送指令之后,指令将被送至计数器指令执行器。通过对D31~D29这三位数据的检测,判断指令的类型执行相关的数据操作,其流程如图3所示。

图3指令执行器流程图

指令类型通过端口读写控制器的输出线code_in线输入指令执行器,指令数据通过端口读写控制器的输出 data_in线输入指令执行器,同时端口读写控制器置低CE线,启动计数器指令执行器。

2.4计数过程控制器

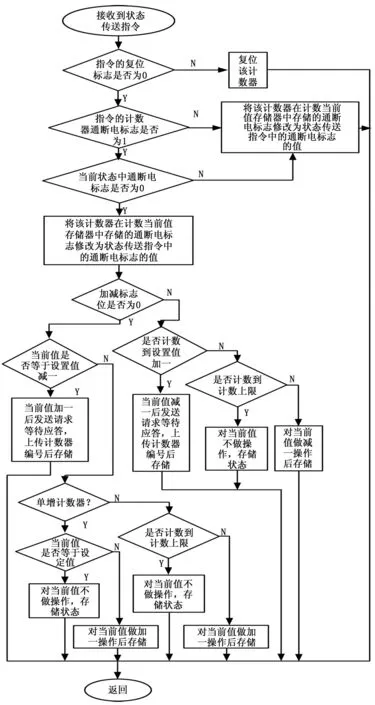

计数控制器功能是对计数器进行计数操作,并将计数结果上传至指令执行控制器的接收端口。当计数器控制器从指令执行控制器接收到计数器信息刷新指令后,将此指令传送到计数控制器,计数控制器根据指令内容中的计数器编号确定计数器在计数当前值存储器中的地址,然后对计数当前信息存储器中的数据进行读写操作,从而实现计数功能。首先对计数器信息刷新指令的通断电状态标志位和加减标志位进行判断,接下来对计数当前信息存储器里的存储的计数当前值进行操作并与该指令里包含的计数设定值进行比较和判断,完成相应的数据操作。该程序流程如图4所示。

图4 计数过程控制器流程图

3指令执行控制器与计数器通信数据格式

计数器控制器主要实现的功能就是接收FPGA指令执行控制器发来的经过ARM编译后的PLC指令,根据指令自主完成对计数器的相关复位、计数操作、计数当前值上传等操作[5-6]。

为了实现PLC的计数功能,对指令执行控制器与计数器控制器通信的指令进行了命令字数据格式的设计。

3.1复位指令

该指令由指令执行控制器发送,当复位标志为001时将对所有计数器进行复位,对计数器控制所有存储的数据清零,效果与上电复位效果一致。当复位标志为010时对部分计数器进行复位,该复位命令对断电保持型的单增或加减计数器和地址映射存储器无效。数据格式如表3所示。

表3 复位指令数据格式表

3.2计数器初始化指令

该指令由指令执行控制器发送,是PLC用户应用程序第一次编译或执行全局复位后发送给计数器控制器的指令,用以初始化计数器。数据指令入表4所示。

表4 计数器初始化指令数据格式表

其中:D28表示是否数据寄存器D传送,数值为0为非D传送;数值为1为D传送。

3.3断电保存指令

该指令由指令执行控制器发送,用于当PLC断电时指令执行控制器告知计数器控制器进入断电保存阶段,接收到该指令后计数器控制器将发送正在使用的断电保持型计数器的编号以及该计数器的当前值,用于保存至PLC再次通电时回传。数据格式如表5所示。

表5 断电保存指令数据格式表

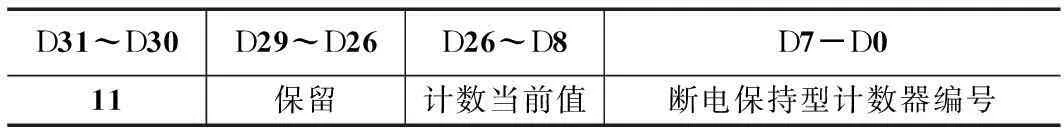

3.4断电保持型计数器断电保存信息

该信息由计数器控制器发送,在接收到指令执行控制器断电保存指令后发送此信息给指令执行控制器,用以保存正在使用的断电保持型计数器的当前值及其对应的计数器编号。数据格式如表6所示。

图5 测试仿真图

D31~D30D29~D26D26~D8D7-D011保留计数当前值断电保持型计数器编号

4仿真测试

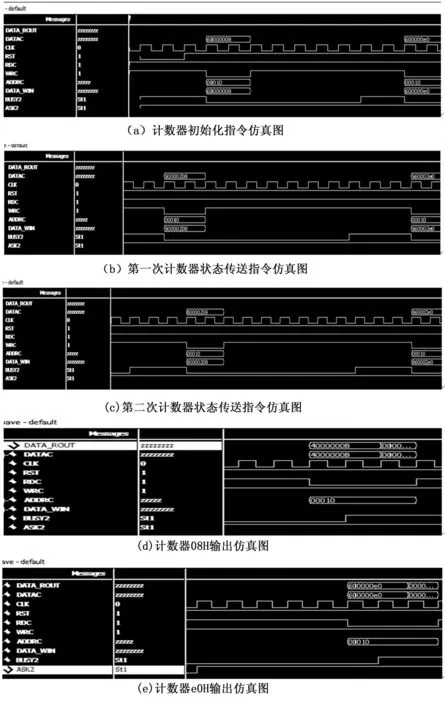

在使用Verilog HDL语言完成硬件描述方面的设计后,使用ModeSim软件配合编写的testbench.v测试程序,模拟指令执行控制器对计数器控制器的输入,然后观察计数器控制器的输出情况[7-9]。测试方法:先使用synplify软件综合后,再进行综合后仿真,对计数控制器进行测试,测试计数控制器是否能完成计数功能。

设计的指令执行控制器访问计数器控制器的模块地址为00010,先模拟指令执行控制器发送指令初始化编号8和224号计数器,两种计数器分别为通用型单增和断电保持型加减计数器,测试仿真如图5所示。

经过测试,计数控制器在计数到时都准确地上传了计数器的编号至指令执行控制器,初步实现了设计目标。

5结语

本设计是在FPGA为平台下设计的一种面向PLC的计数器控制器,设计了计数器控制器与指令执行控制器的通信时序和通信协议。基本实现了PLC的计数功能,并且本设计使用了地址映射存储器来存储特定编号计数器的相关数据在计数存储器中的地址,使得计数控制器的复位指令和断电保持计数器的信息上传操作更加快速高效,在大规模计数器的设计中有一定的参考价值。

参考文献:

[1] 方承远,张振国. 工厂电气控制技术(第3版) [M]. 北京:机械工业出版社,2008.

[2] 王荣华,张燕斌.PLC技术在矿山机电控制中应用研究[J].现代商贸工业,2011(6):246-247.

[3] 侯鸿佳,蔡启仲,陈文辉,等.ARM+FPGA组成的PLC结构的通信系统[J].广西工学院学报.2012,23(1):60-64.

[4] 蒋玉新,蔡启仲,李克俭,等. 基于ARM-FPGA的PLC源程序编译系统的设计[J]. 计算机应用与软件,2013,09:179-182.

[5] Yu L,Li K J,Cai Q Z,et al. Design of Parallel Operated Counter based on ARM + FPGA[A].2012 International Conference on Measurement, Instrumentation and Automation (ICMIA 2012)[C].Guangzhou,2012:234-239.

[6] 张炜,李克俭,蔡启仲,等.基于FPGA的PLC并行计数器的设计[J].计算机工程与设计,2013,34(4):1244-1249.

[7] 夏宇闻.Verilog数字系统设计教程[M](第2版).北京:北京航空航天大学出版社,2008.

[8] 王金明.数字系统设计与Verilog HDL(第3版).北京:电子工业出版社,2009.

[9] 华清远见嵌入式培训中心.FPGA应用开发入门与典型实例[M].北京:人民邮电出版社,2008.

Design of Counter in PLC Based on ARM+FPGA

Xu Xiaoyu1, Li Kejian1, Cai Qizhong1, Pan Shaoming1, Yu Ling2

(1.College of Electronic and Information Engineering,Guangxi University of Technology,Liuzhou545006,China;2.Department of Electrical and Computer Engineering,Lushan College, Guangxi University of Science and Technology,Liuzhou545616,China)

Abstract:Counter is one of the important parts of the PLC. In the automatic control system with PLC as the core component, the software can realize the real-time and accurate count of the system. Through the dual port RAM, ARM command can be transmitted to the FPGA. The FPGA control counter related operations, the FPGA oscillator frequency 50 MHz as counter control module timing constraints, counter design with addition and subtraction counting function, power holding function, data transmission function, so as to meet the needs of the PLC controller of the count, and through the use of memory address mapping the counter controller instruction execution more efficient. The communication time sequence and communication protocol of the FPGA internal control and FPGA instruction execution controller are designed. After the simulation and testing of the design, the count frequency of a single counter reaches 2 MHz, the function of the PLC counter is basically realized, and the design requirements of the stable count are achieved.

Keywords:counter; PLC; dual port RAM; address mapping memory; FPGA communication protocol

文章编号:1671-4598(2016)02-0271-04

DOI:10.16526/j.cnki.11-4762/tp.2016.02.075

中图分类号:TP3

文献标识码:A

作者简介:徐晓宇(1988-),男,河北唐山人,硕士研究生,主要从事嵌入式系统与自动化装置方向的研究。

基金项目:广西科学基金项目(桂科自2014GXNSFA118392);广西教育厅科研项目(2013LX092)。

收稿日期:2015-09-04;修回日期:2015-09-28。