基于ARM Cortex-M3微控制器与QDUC的嵌入式激励器设计

2016-03-17徐林峰

徐林峰,李 星

(中国电波传播研究所青岛分所,山东 青岛 266107)

基于ARM Cortex-M3微控制器与QDUC的嵌入式激励器设计

徐林峰,李星

(中国电波传播研究所青岛分所,山东 青岛266107)

摘要:为解决传统激励器设备体积大、成本高等问题,采用ARM Cortex-M3微控制器与QDUC方案设计了一种嵌入式激励器;系统基于ARM Cortex-M3微控制器、以太网PHY与uIP TCP/IP协议栈构建有线以太网实现与外部上位机之间的数据的收发,使用专用QDUC集成电路芯片对以太网传送来的基带数据进行正交数字上变频,产生任意波形射频激励信号;该方案具有环境适应性强、尺寸小、结构简明、开发难度低、工作稳定可靠、可扩展性强等特点;试验实测系统工作于UDP模式时最大可用基带数据更新速率可达21.5 Mbps,输出射频信号载波频率覆盖DC~400 MHz,满足实际工程需求。

关键词:微控制器;正交上变频器;激励器;以太网

0引言

激励器主要用于向雷达发射机、电子对抗等设备等提供各种激励信号。传统的激励器设计方案是采用PCI、CPCI、VPX等标准总线计算机板卡的形式,依托通用计算机平台实现信号的产生[1]。这种方案可靠性较高,但成本亦较高,且无法实现设备的小型化、便携化。本文依据工程实际需求,采用将ARM Cortex-M3微控制器与QDUC(正交数字上变频器)结合的技术方案,实现了一种低成本、小尺寸、可组网使用的嵌入式激励器。

1系统功能与结构

嵌入式激励器以基于ARM Cortex-M3内核的GD32F107VCT6(以下简称GD32F107)微控制器及QDUC为核心,配合以太网接口电路实现对以太网传输来的任意基带数据的正交数字上变频。

嵌入式激励器系统组成如图1所示。GD32F107与以太网PHY(物理层收发器)之间采用RMII模式连接,快速以太网发来的数据帧由以太网PHY处理后发送给GD32F107,由GD32F107解析后得到控制指令及实时的I路与Q路基带数据,控制指令通过SPI串行口发送给QDUC,基带数据通过并行数据接口逐帧发送给QDUC,由QDUC根据预先设置的参数将基带数据上变频生成期望的射频模拟信号并送出。SD存储卡用于用户存储以太网传输来的基带数据,以备设备独立工作时调取使用。

图1 系统组成框图

2硬件设计

2.1微控制器

GD32F107是一款基于ARM Cortex-M3 r2p1内核的互联型国产通用微控制器,其最高工作主频108 MHz,具有单周期乘法器与硬件除法器,片上具有256kB FLASH、96kB SRAM、1个10/100 M以太网MAC(媒体访问控制器)控制器、3个SPI串行口、80个GPIO等丰富的外设资源,并具有片上FLASH访问零等待的特点[2]。GD32F107工作电源电压为2.6~3.6 V,典型工作电压为3.3 V。

2.2QDUC

QDUC主要功能是将输入基带数据进行频率变换、频谱搬移, 即在数字域实现混频功能。本文设计中QDUC选用ADI公司生产的AD9957集成芯片。

AD9957将1个直接数字频率合成器(DDS)、1个1GSPS 14位数模转换器、时钟乘法器电路、数字滤波器和其它DSP功能集成在单个独立芯片上,具有32位频率分辨率、14位相位分辨率,最高内部系统时钟为1 GSPS,可直接输出高达400 MHz模拟射频信号,可以在有线或无线通信系统中为数据传输提供基带上变频功能[3]。

AD9957工作电源分别为1.8 V与3.3 V,采用SPI串行口进行配置编程,采用18位并行数据接口输入I路与Q路基带数据。其具有3种工作模式,分别为正交调制(QDUC)模式、DAC 插值模式、单音模式,该工作模式通过控制功能寄存器1 (CFR1)中的工作模式位进行选择。本文设计中,AD9957可以按照遥控指令工作于上述模式中的任意一种,当工作于正交调制(QDUC)模式与DAC插值模式时,需要外部(以太网或SD存储卡)提供基带数据。

本文设计中AD9957采用外部10 MHz OCXO提供的单端10 MHz信号作为参考时钟。AD9957内部锁相环将该参考时钟倍频作为系统时钟(fSYSCLK)使用。

2.3以太网接口

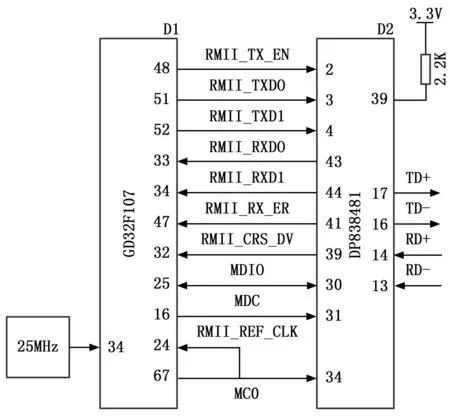

GD32F107微控制器片上MAC兼容MII(媒体独立接口)与RMII(精简媒体独立接口)两种接口模式,这为以太网接口电路的设计提供了极大的便利。本文设计中以太网PHY选用TI公司DP83848I。DP83848I是一款单口10/100 Mb/s以太网PHY,支持MII/RMII接口模式,可与GD32F107微控制器无缝连接[2,4]。DP83848I与GD32F107之间采用RMII接口模式连接。电路原理如图2所示。

图2 以太网接口电路原理图

需要注意的是,DP83848I需要通过预置上拉或下拉电阻的方式进行模式、地址功能的设置。为使DP83848I工作于RMII接口模式,39脚MII_MODE应通过电阻上拉至3.3 V电源,同时6脚SNI_MODE保持悬空(芯片内默认下拉)。此外DP83848I在上电复位时依照42脚PHYAD0(芯片内默认上拉)、43脚PHYAD1(芯片内默认下拉)、44脚PHYAD2(芯片内默认下拉)、45脚PHYAD3(芯片内默认下拉)、46脚PHYAD4(芯片内默认下拉)电平状态决定其物理地址并写入PHYCR寄存器中。在本文设计中,DP83848I的42脚、43脚、44脚、45脚、46脚未在片外配置上拉或下拉电阻(如图2),故其物理地址为0x01。

2.4VFD显示屏

VFD显示屏用于显示设备工作状态信息,其具有自发光、亮度高、可靠性高、环境适应性好等特点。本文设计选用VFD显示屏为双叶M202SD16FA。M202SD16FA为点阵式真空荧光显示屏,内部集成控制驱动电路,可显示2x20个字符,每个字符为5x8点阵。M202SD16FA具有i80接口模式、M68接口模式及串行接口模式3种数据接口,本文设计中采用i80接口模式。M202SD16FA工作电源为5 V,其工作温度与存储温度范围均为-40~+85 ℃。

2.5其他电路

本文方案中设计有SD存储卡电路,用于存储基带数据。SD存储卡采用SPI模式挂载于GD32F107微控制器的SPI3口上。

本文设计中电源转换电路用于将外部DC12V电源转换为+5 V、+3.3 V(数字)、+3.3 V(模拟)、+1.8 V(数字)、+1.8 V(模拟)共5路电源,供各电路单元使用。其中+3.3 V(模拟)与+1.8 V(模拟)专门用于AD9957集成芯片模拟电源供电。为保证AD9957所产生的射频信号质量,其模拟电源供电使用单独的低压差线性降压稳压器转换提供。

3软件设计

3.1硬件初始化

硬件初始化主要工作是对GD32F107时钟配置进行初始化,对DP83848I进行初始配置,对AD9957进行初始配置。其关键流程描述如下:

1)修改配置文件中定义的HSE(外部高速时钟)与当前使用的时钟频率一致,本设计中GD32F107采用外部25 MHz有源晶振:

define HSE_VALUE ((uint32_t) 25000000)

2)在主程序中使能HSE,设置GD32F107片上外设时钟,配置中断,系统时钟配置如下:

选择锁相环(PLL)时钟源为HSE的一分频,倍频数为4,即锁相环输出频率为100 MHz;

选择GD32F107系统主时钟SYSCLK的时钟源为锁相环时钟输出。

3)DP83848I各寄存器初始配置如下,工作模式为100 Mb/s全双工,使能自动协商:

PHY_BMCR = 0x3100

PHY_ANAR = 0x01e1

PHY_ANNPTR = 0x2801

PHY_PHYCTRL = 0x8021

4)AD9957各寄存器初始基本配置如下,工作于QDUC模式,主时钟400 MHz,使能反Sinc 滤波器,输出信号频率55.8 MHz:

CFR1(地址0x00)为0x00400002

CFR2(地址0x01)为0x01400000

CFR3(地址0x02)为0x1000c150

Profile 0(地址0x0e)高32位为0x1c91d14e

Profile 0(地址0x0e)低32位为0x23b645a2

需要说明的是,CFR3寄存器用于配置AD9957的主时钟频率等关键参数。选用低的时钟频率可以提高输出射频模拟信号的频率分辨率及杂散抑制指标,选用高的时钟频率则可以提高输出射频模拟信号的频率上限。

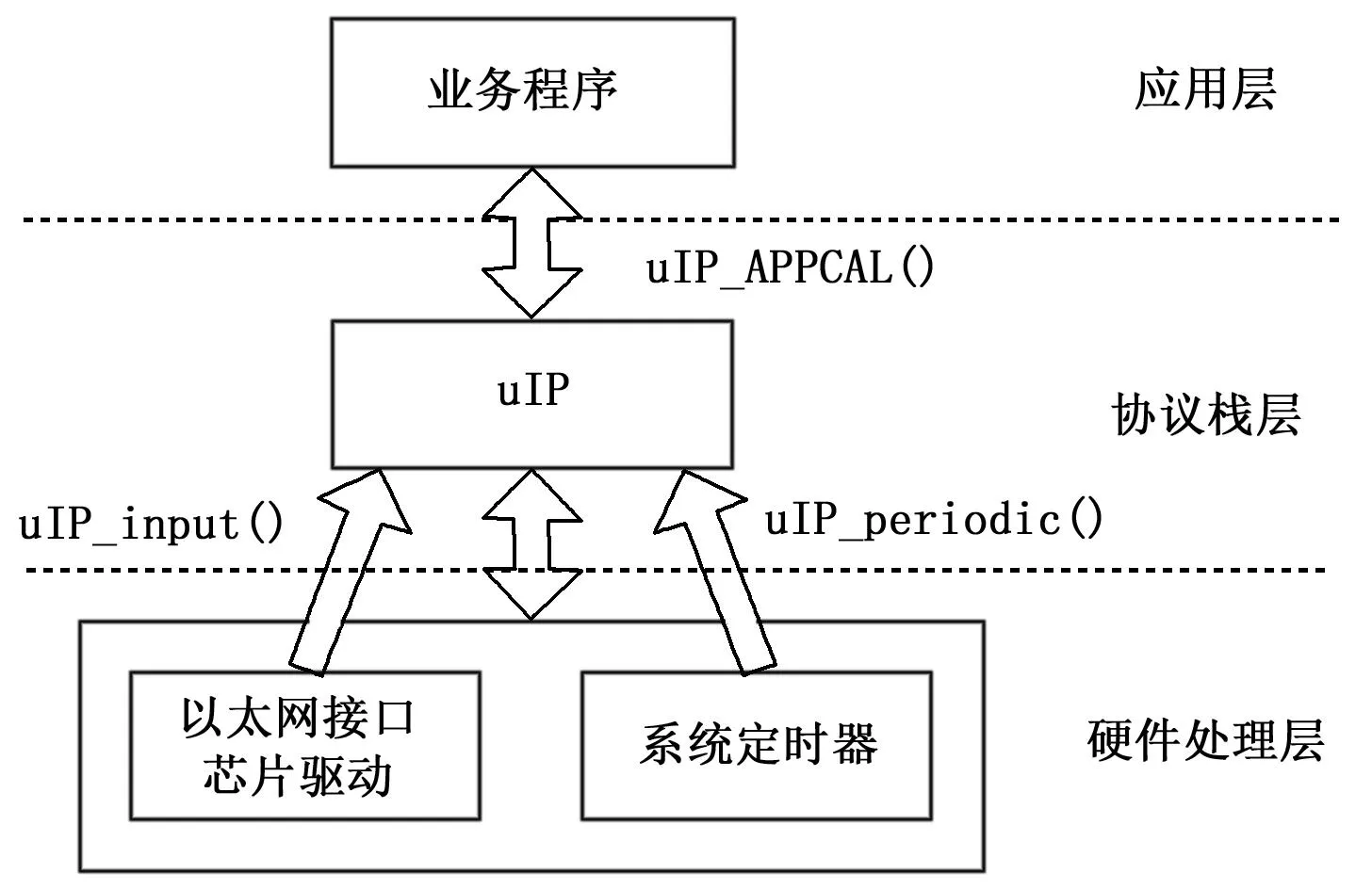

3.2以太网协议栈设计

本文设计方案中以太网协议栈采用uIP协议栈。uIP是一种适用于小型嵌入式设备通信的TCP/IP协议栈,其采用C语言设计,并开放全部代码。uIP 协议栈精简了标准TCP/IP协议栈中不常用的功能,简化了工作流程,其设计重点着眼于IP、TCP和ARP等协议的实现。其硬件处理层、协议栈层和应用层共用一个全局缓存区,不存在数据的频繁拷贝,且发送和接收都是依靠该缓存区实现,实际使用中可极大地节省存储空间和处理时间。uIP协议栈支持多个主动连接和被动连接并发,对数据的处理采用轮循机制,不需要操作系统的支持[5]。

图3 uIP体系结构

uIP协议栈通过接口函数与硬件处理层及应用层业务程序通信,其体系结构如图3所示。 uIP提供3个接口函数给底层硬件处理层,分别是uip_input()、uip_periodic()、uip_init(),其中uip_input()用于处理输入包,uip_periodic()处理周期计时事件,uip_init()用于初始化协议栈侦听端口及关闭所有连接。

主程序需要进行如下初始化操作:

1)DP83848I 驱动接口初始化和uIP初始化;

2)设置本机IP地址、网关IP地址、子网掩码。

当DP83848I从以太网接收到数据后产生中断,主程序需从DP83848I读取一个IP数据包,并得到数据长度:

uip_len = tapdev_read();

然后对前述数据包进行校验并处理:

if(BUF->type == htons(UIP_ETHTYPE_IP))

{

/*去除以太网帧头结构,更新ARP表*/

uip_arp_ipin();

/* IP包处理*/

uip_input();

3) 将液压油管路上的90°直角弯头全部换成平滑过渡的大弯头,从流体力学的角度看,平滑的大弯头产生的压损小于直角弯头所产生的压损。

}

3.3通信协议

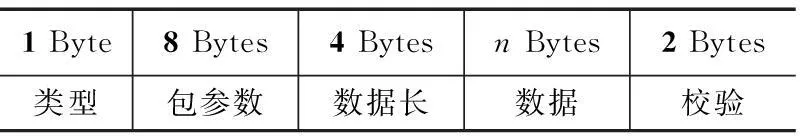

嵌入式激励器需要上位机通过以太网输入控制指令包及基带数据包,两种数据包的帧结构定义如表1所示。

表1 指令包帧结构

类型项:长度1字节,用于指明该数据帧为控制指令。

指令内容项:长度16字节,用于存储指令内容,如用于设置工作频率、实现工作模式切换、控制信号产生与停止等功能实现。

校验项:长度2字节,用于数据校验。基带数据包帧结构如表2所示。

表2 基带数据包帧结构

类型项:长度1字节,用于指明该数据帧为基带数据。

包参数项:长度8字节,前4个字节为数据包总数,后4个字节为当前数据包序号。

数据项:长度为n字节,n即数据长项值,用于存放基带数据。

校验项:长度2字节,用于数据校验。

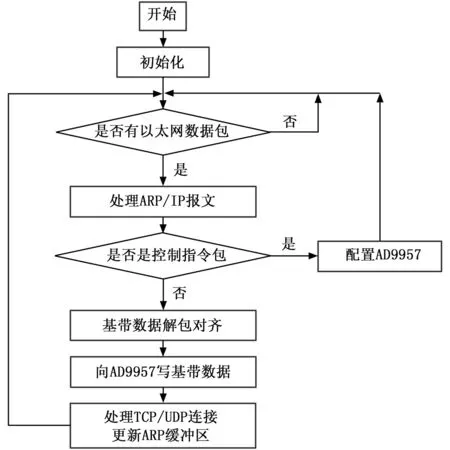

3.4程序流程

系统主程序流程如图4所示。系统上电开机后,先进行初始化操作,随后在主循环中判断是否有以太网数据包,如有则判断是控制指令包还是基带数据包并进行进一步处理。如果是控制指令包则解析后根据指令配置相关控制参数,如果是基带数据包则解包后按包序号顺序对齐后再通过并行数据接口定时写入AD9957。当前数据包处理完毕后,程序检查处理TCP/UDP连接并更新ARP缓冲区,并等待下一个以太网数据包。

图4 系统主程序流程图

4系统测试

嵌入式激励器网络传输性能决定了数字上变频基带数据的更新速率,直接影响AD9957性能的发挥。使用QT编写上位机测试软件,在专用100 M Base-Tx快速以太网环境下,采用TCP与UDP两种方式对嵌入式激励器网络传输性能进行了长时间的稳定性测试,测试数据如表所示。

表3 传输速率统计表

表3中,最大稳定传输速率指上位机与嵌入式激励器之间所能稳定实现的丢包率小于0.1%时的传输速率。测试数据表明,在TCP方式下基带数据最高更新速率可达到8.2 Mbps,在UDP方式下基带数据最高更新速率可达到21.5 Mbps。实际应用时为保证基带数据的更新速率,采用了UDP方式向嵌入式激励器传输基带数据。

本文设计中,为避免因基带数据包丢失影响最终产生的射频信号质量,在上位机与嵌入式激励器通信协议中引入了完善的应答机制。对于上位机向嵌入式激励器发送的以太网数据包,嵌入式激励器在收到后都要予以回应,如果上位机在发送完一个数据包后超过一定时间内未收到嵌入式激励器发回的应答包,则进行重发操作,如果重发3次仍未收到应答包则自动中断当前任务。嵌入式激励器在工作于QDUC模式下时,如果在一定时间内未收到下一帧基带数据包,则中止当前工作任务,自动中断射频信号的产生,避免损坏后级功放或发射机等设备,并在VFD显示屏显示出错信息。

实测嵌入式激励器可产生DC~400 MHz射频模拟信号。需要注意的是其所能产生的射频模拟信号频率上限与AD9957主时钟配置有关,当需要产生较高频率射频模拟信号时,AD9957的CFR3寄存器配置值必须根据其数据手册确定。

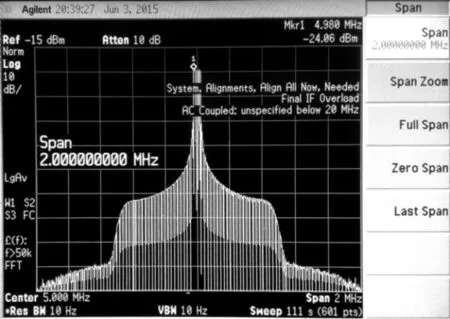

采用上位机控制嵌入式激励器工作于QDUC模式,工作频率5.0 MHz,通过以太网提供一组脉冲线形调频基带数据,产生的射频信号频域波形如图5所示。

图5 脉冲线性调频信号实测频谱图

5结语

本文以GD32F107微控制器与数字上变频器AD9957为核心,采用成熟的快速以太网技术实现了嵌入式激励器的设计,该激励器具有成本低、结构简单、开发难度低等特点,便于实现设备的小型化、便携化设计。测试数据表明,该设备可根据上位机提供的基带数据产生任意波形射频信号,性能较高、频率范围宽、灵活度高,可组网使用,满足工程需求。

参考文献:

[1] 宋思盛.基于PCI总线的通用雷达信号源设计[J].雷达与对抗,2004, 1:33-38.

[2] GD32F107xx ARM Cortex-M3 32-bit MCU Datasheet[Z]. GigaDevice Semiconductor Inc.2013.

[3] 基于AD9957的伪卫星脉冲调制技术研究[J]. 无线电通信技术,2008,34(6):21-24.

[4] SNLS266E - DP83848C/I/VYB/YB PHYTER QFP Signle Port 10/100 Mb/s Ethernet Physical Layer Transceiver Datasheet [Z]. Texas Instruments Incorporated.2015.

[5] 孟松.基于嵌入式系统的TCP/IP协议栈的实现[J].无线电通信技术,2007,33(4):8-10.

A Design of Embedded Exciter Based on ARM Cortex-M3 Microcontroller and QDUC

Xu Linfeng, Li Xing

(China Research Institute of Radiowave Propagation, Qingdao266107, China)

Abstract:This paper reports a design of embedded exciter based on ARM Cortex-M3 Microcontroller and QDUC, in order to deal with the problem of traditional exciter system, for example it has large volume, higher cost, and so on. The design using the ARM Cortex-M3 microcontroller, Ethernet PHY and uIP TCP/IP protocol stack to build a wired network achieving data communication with the extern host control node. The system can generate arbitrary waveform RF excitation signal, by means of quadrature digital upward frequency conversion employing the baseband data received from the Ethernet using the QDUC ASIC. The design has the features of excellent adaptability to environment, small size, simple structure, easy to design, credible performance, strong scalability. Experiments show that the maximum available baseband data updating rate can be reached in UDP working mode is 21.5Mbps, and the RF signal carrier frequency covers the range of DC to 400MHz, which can meet the requirements of the project.

Keywords:microcontroller; QDUC; exciter; Ethernet

文章编号:1671-4598(2016)02-0182-04

DOI:10.16526/j.cnki.11-4762/tp.2016.02.050

中图分类号:TP273

文献标识码:A

作者简介:徐林峰(1982-),男,山东临沂人,工程师,硕士研究生,主要从事嵌入式系统设计方向的研究。

收稿日期:2015-08-07;修回日期:2015-09-10。