基于VxWorks的有线通信模块设计

2016-03-07曹文继王小龙杨向白奉强

曹文继, 王小龙, 杨向, 白奉强

(1.成都大学 机械工程学院, 四川 成都 610106; 2.成都大学 信息科学与工程学院, 四川 成都 610106)

基于VxWorks的有线通信模块设计

(1.成都大学 机械工程学院, 四川 成都 610106; 2.成都大学 信息科学与工程学院, 四川 成都 610106)

单对线高速数字用户线技术是一种用于点对点的高速数据传输技术,可用于远距离局域网的连接,以满足用户远程的较小传输容量的企业网专线互联和对称带宽的Internet接入.基于VxWorks的有线通信模块以ARM9控制芯片作为主控芯片,完成对通信芯片SDFE-24624的参数配置和控制,也提供状态信息上报、主机控制及断线自动重连功能.模块可以不在人为干预的情况下自动运行连接,让整个模块的使用更加方便.

被复线;VxWorks;ARM9;SHDSL;SDFE-24624

0 引 言

单对线高速数字用户线(Single-pair High-speed Digital Subscriber Line,SHDSL)技术是一种用于点对点的高速数据传输技术[1-13],可用于远距离局域网的连接,以满足用户远程的较小传输容量的企业网专线互联和对称带宽的Internet接入等.为了方便实现有线通信,本研究采用英飞凌公司生产的通信芯片SDFE-24624,并采用基于ARM9的VxWorks控制系统实现,从而对通信芯片SDFE-24624进行配置和管理[1-4],体现了被复线通信模块智能便捷的使用特点.

1 系统硬件设计

1.1 系统的总结构设计

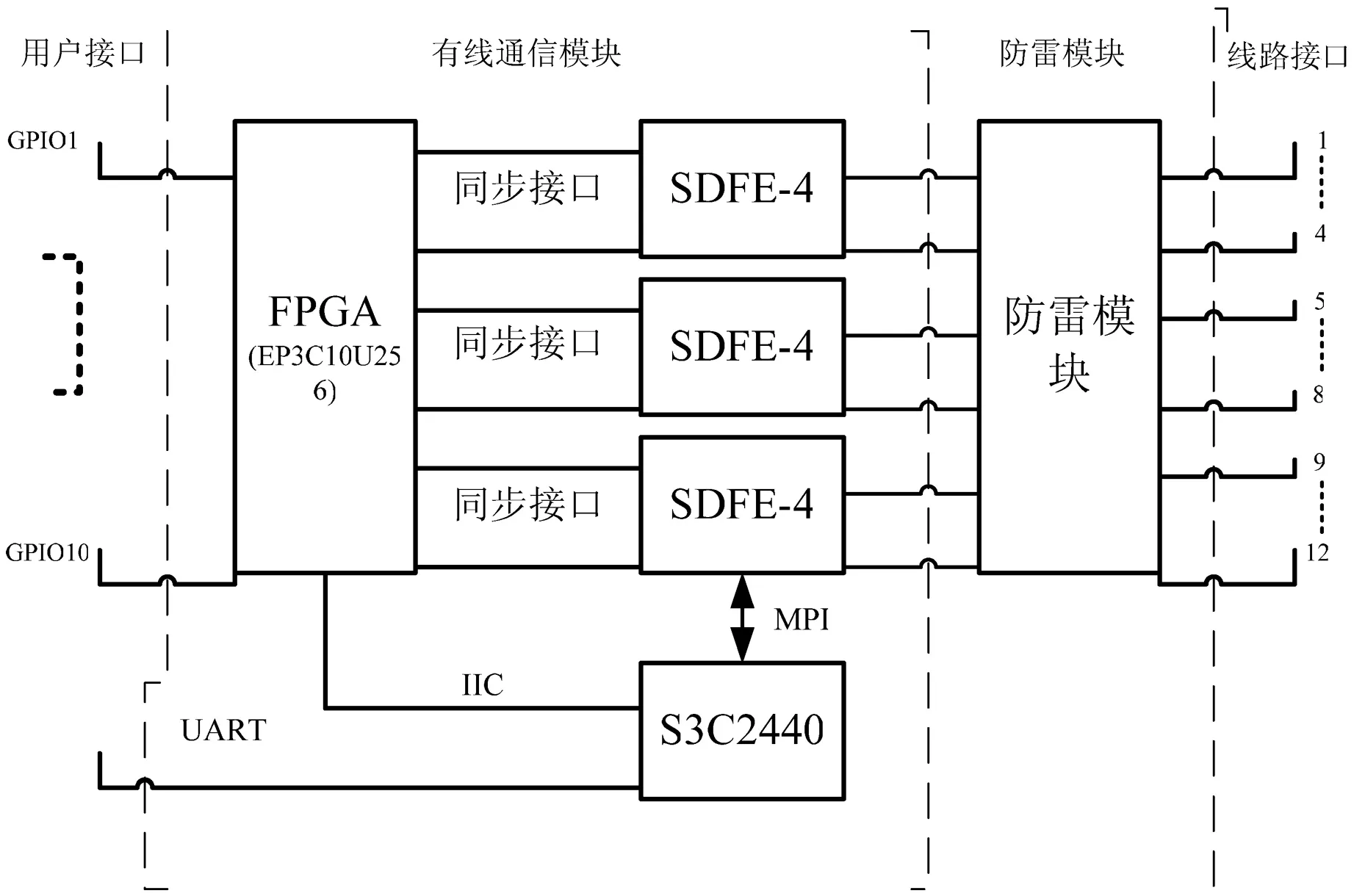

系统的被复线有线通信模块由主机模块和从机模块组成,主机与从机间通过采用TEG-707被复线进行连接.主机模块通过12个独立的线路界面连接多至12个从机模块,实现主机分别与12个从机的数据通信,模块硬件框图如图1所示.

基于VxWorks的有线通信模块的主、从模块具有完全一样的硬件设计.主从的选择可以通过硬件跳冒的连接或者软件设置的方法选择.有线通信模块硬件中,参数配置功能及芯片的管理主要由S3C2440完成,另外处理器还需要状态上报及状态控制管理等功能.

1.2 主控芯片及其使用

被复线有线通信系统主控采用ARM9嵌入式的微处理器S3C2440A,其包含ARM920T内核及0.13 μmCMOS标准宏单元和存储器单元,低功耗,简单,精致,且全静态设计,特别适合于对成本和功率敏感型的应用.S3C2440A采用了新的总线架构,如先进微控制总线构架(Advanced Microcontroller Bus Architecture,AMBA),其突出的特点是含有一个由Advanced RISC Machines(ARM)公司设计的16/32-bit ARM920T的RISC处理器.ARM920T实现了MMU、AMBA总线和哈佛结构高速缓冲体系结构.这一结构具有独立的16 KiB指令高速缓存和16 KiB数据高速缓存,每个都由8字长的行组成.除通过提供一套完整的通用系统外设,S3C2440A减少了整体系统成本,且无需配置额外的组件.其内部框图如图2所示.

图1 模块功能框图

1.3 S3C2440A UART总线概述

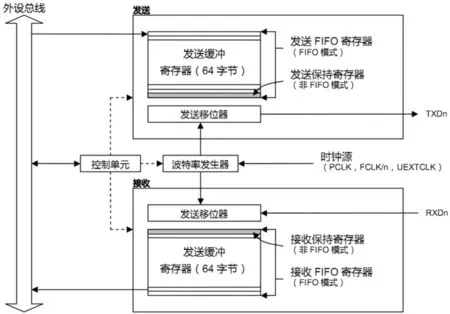

S3C2440A的通用异步收发器(Universal Asynchronous Receiver/Transmitter, UART)配有3个独立异步串行I/O端口,每个都可以是基于中断或基于DMA模式的操作.UART可以通过产生中断或DMA请求来进行CPU和UART之间的数据传输.UART通过使用系统时钟以支持最高115.2 Kibit/s的比特率.如果是外部器件提供UEXTCLK的UART,则UART可以运行在更高的速度.每个UART通道包含2个64 B的FIFO.每个UART包含一个波特率发生器、发送器、接收器和一个控制单元.波特率发生器可以由PCLK、FCLK/n或UEXTCLK(外部输入时钟)时钟驱动.发送器和接收器包含了64 B FIFO和数据移位器.将数据写入到FIFO,接着在发送前复制到发送移位器中,随后在发送数据引脚(TxDn)移出数据.同时,从接收数据引脚(RxDn)移入收到的数据,并从移位器复制到FIFO,内部结构如图3所示.

图2 S3C2440A内部框图

图3 S3C2440A内部UART框图

1.4 看门狗

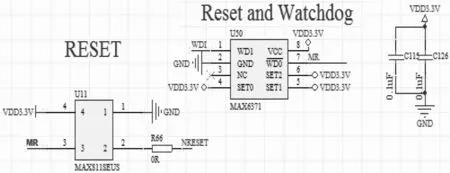

被复线通信模块中,为了防止系统意外运行失败,因此需要用到看门狗芯片.S3C2440A本身自带看门口,但是为了避免意外,本研究采用外置看门狗的方式.如果达到硬件设置的时间(这里设置为1 min)没有喂狗,那么看门狗将发出复位信号,其硬件电路设计如图4所示.

图4 看门狗电路

2 系统软件设计

2.1 软件系统整体设计

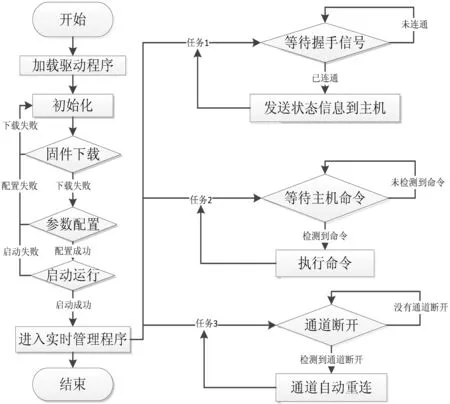

基于VxWorks被复线控制通信系统主要实现SDFE-24624配置和管理工作.在模块上电后,通过发送消息的方式对芯片进行配置,在芯片启动以后对芯片返回的数据进行管理,控制芯片及其上报目前各个通道的状态信息等.控制步骤如下:硬件初始化,包括控制I/O、中断、芯片初始化等;下载SDFE-24624运行所需要的固件到片内;参数配置,包括SDFE-24624运行参数配置、模式配置、参数处理等;管理任务,包括芯片运行状态、上报状态到主机、断线重连等.

被复线控制系统程序采用模块化的思想,将各个部分程序进行模块化,让使用过程更加方便程序的调用,整个系统的程序设计框图如图5所示.

图5 程序总体框图

2.2 驱动程序设计

在对芯片进行初始化之前,首先加载SDFE-24624的驱动程序.VxWorks操作系统中,系统提供的iosDrvInstall函数可以将驱动设备的驱动程序绑定到系统当中,绑定完成以后只需要通过系统打开设备进行读写即可.部分绑定程序如下:

IFX-int32-t Pef24624e-DevCreate(void)

{

PEF24624E-DEV-t*pDevice=NULL;

charbuf[64];

IFX-uint32-t dev-no;

SetTraceLevel(PEF24624E-DRV,DBG-LEVEL-LOW);

SetLogLevel(PEF24624E-DRV,DBG-LEVEL-HIGH);

if (Pef24624eDrvNum<=0)

{

Pef24624eDrvNum=iosDrvInstall(NULL,NULL,

(FUNCPTR) Pef24624e-Open,

(FUNCPTR) Pef24624e-Close,

(FUNCPTR) Pef24624e-Read,

(FUNCPTR) Pef24624e-Write,

(FUNCPTR) Pef24624e-IoCtl);

if (Pef24624eDrvNum<=0)

{

Pef24624eDrvNum=0;

return (-1);

}

}

else

return (-1);

}

此绑定函数中涉及到的操作函数及其功能如下:

Pef24624e-Open:打开设备获取设备号.

Pef24624e-Close:关闭设备.

Pef24624e-Read:对芯片进行读操作.

Pef24624e-Write:对芯片进行写操作,发送Message消息.

Pef24624e-IoCtl:芯片配置命令,包括AUX及RAMSHEEL配置等.

2.3 主机与芯片通信

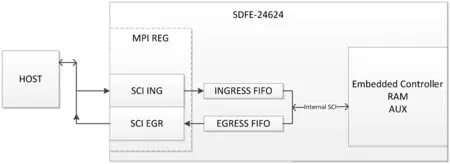

SDFE-24624内置有Embedded Controller、RAM及AUX几大功能模块,外部主控与内部通信的连接方式如图6所示.

图6 内部连接框图

2.4 固件下载

SDFE-24624内部有4个通道,每个通道都配有内部控制器用于配置管理通道.内部控制器和单片机一样需要有应用程序供其运行,所以需要下载固件文件到SDFE-24624中供内部控制器使用.SDFE-24624的固件文件分为2个段,分别为代码段和数据段,他们的大小分别为144 KiB和48 KiB.固件下载过程如图7所示.

图7 固件下载流程

3 结 果

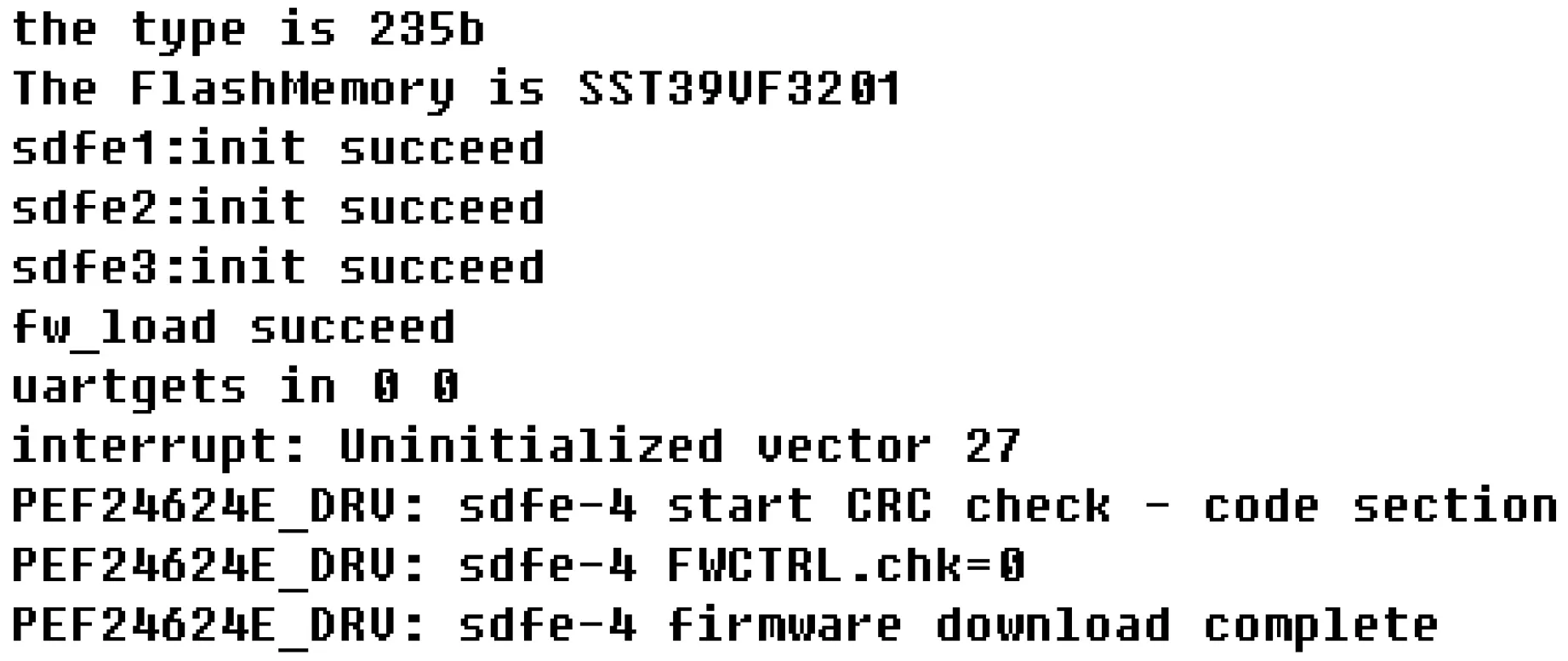

3.1 固件下载结果

图8为固件下载结果.下载过程主要有初始化及固件下载,其执行结果为Init Succeed和Download Complete.

图8 固件下载结果

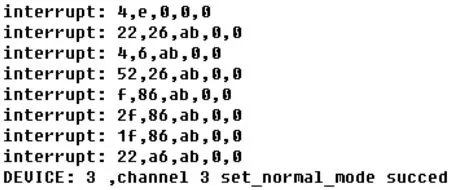

3.2 配置结果

图9为参数配置成功后的结果.在此过程中,主要执行的是芯片参数的配置以及ACK消息的处理.

图9 数据配置结果

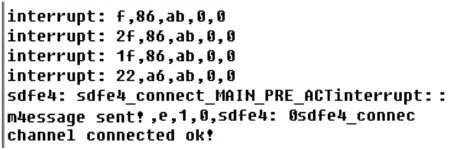

3.3 连接结果

图10为通道建立的结果.当通道建立成功后,就可以实现正常通信.

图10 连接成功结果

3.4 信息上报结果

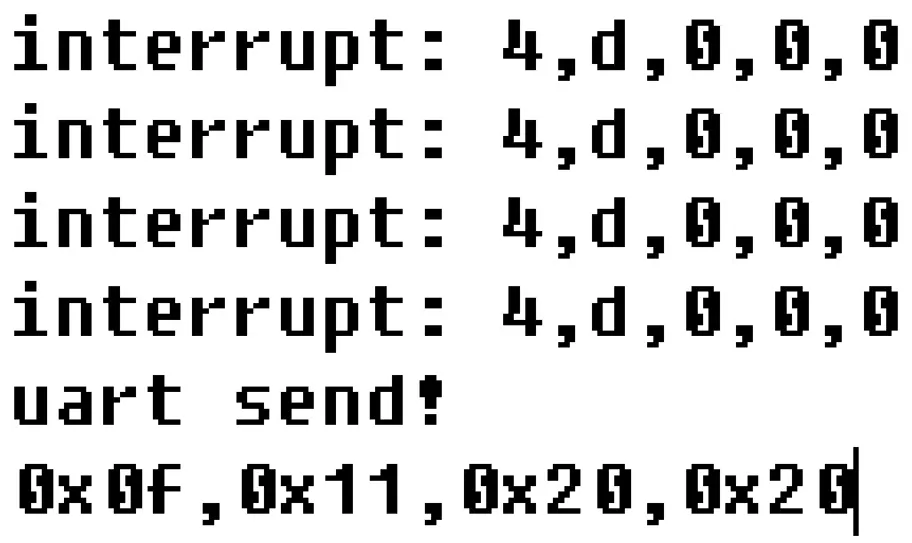

图11为通道连接成功后将状态信息上报给主机的发送结果.可以看出,连通的通道是第一块设备的第一个通道.

图11 uart发送

3.5 下发控制命令

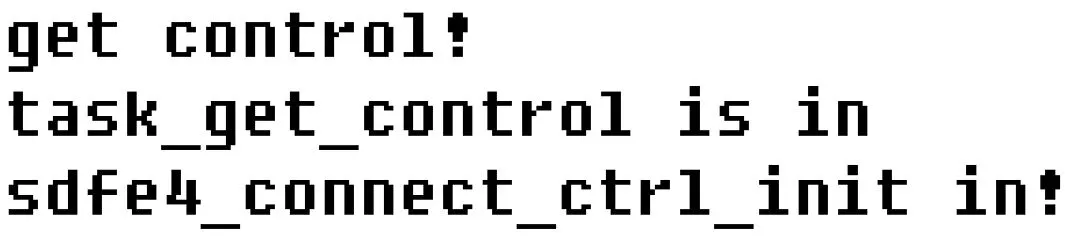

图12为获取主机发来的消息后进行控制的信息,显示的是芯片初始化结果.首先执行task-get-control程序,再执行sdfe4-connect-ctrl-init,即完成初始化.

图12 下发命令控制

[1]曹桂平.VxWorks设备驱动开发详解[M].北京:电子工业出版社,2011.

[2]田志民.VxWorks操作系统下PCI总线驱动设计[J].电子测量技术,2006,29(2):1-3.

[3]罗国庆.VxWorks与嵌入式软件开发[M].北京:机械工业出版社,2003.

[4]温彦军.VxWorks程序开发实践[M].北京:人民邮电出版社,2004.

[5]李开荣.SHDSL接入技术特点及其发展趋势[J].现代电子技术,2004,27(22):1-3.

[6]刘光海,傅丰林.单线对高比特率数字用户线(SHDSL)简介[J].现代电子技术,2002,26(1):62-65.

[7]刘谦.DSL技术的发展趋势[J].现代电信科技,2005,35(9):33-37.

[8]叶字煦.SHDSL接入技术及其应用[J].电信科学,2004,20(3):36-38.

[9]童诗白,华成英.模拟电子技术基础[M].北京:高等教育出版社,2001.

[10]李征,王晓宁,金添.接入网与接入技术[M].北京:清华大学出版社,2003.

[11]刘琦.主流ADSL技术比较及其前景[EB/OL].[2003-12-25].http://www.ccidnet.com/2003/1225/77756.shtml.

[12]Walter Goralski.ADSL和DSL技术[M].刘勇,译.北京:人民邮电出版社,2000.

[13]Dennis J Rauschmayer.ADSL/DSL原理[M].杨威,译.北京:人民邮电出版社,2001.

Software Design of Wire Communication Module Based on VxWorks

CAOWenji1,WANGXiaolong1,YANGXiangjun1,BAIFengqiang2

(1.School of Mechanical Engineering, Chengdu University, Chengdu 610106, China;2.School of Information Science and Engineering, Chengdu University, Chengdu 610106, China)

SHDSL is a kind of point to point high speed transmission technology.It can also be used in remote LAN connection.Besides it can meet the users' enterprise network special line interconnection with a comparatively smaller transmission capacity and symmetrical bandwidth Internet access,etc.Wire communication module based on VxWorks uses the ARM9 controller which is produced by the Samsung as the main controller.Parameter configuration and controlling function of SDFE-24624 is finished.The program can also upload the state of devices,control the main engine and reconnect the channel which is out of connection.The module can run and complete connection automatically without human control which promotes the module to be used in an easier way.

field telephone wire;VxWorks;ARM9;SHDSL;SDFE-24624

1004-5422(2016)04-0375-04

2016-09-14.

曹文继(1974 — ), 男, 硕士, 高级工程师, 从事数据通信与图像处理传输研究.

TN919.2;TP311.52

A