一种基于UVM加快功能验证收敛的方法

2016-02-27徐文进王世中王宣明

徐文进,田 泽,王世中,王宣明

(中航工业西安航空计算技术研究所 集成电路与微系统设计航空科技重点实验室,陕西 西安 710068)

一种基于UVM加快功能验证收敛的方法

徐文进,田 泽,王世中,王宣明

(中航工业西安航空计算技术研究所 集成电路与微系统设计航空科技重点实验室,陕西 西安 710068)

功能验证是IC设计最重要的步骤之一。随着设计复杂度的增加,定位缺陷成本也日益增加,许多设计验证团队将相当一部分精力放在高效验证过程开发上。文中以航电CNI系统主机接口模块功能验证为例,采用基于统一覆盖率验证管理技术、UVM验证技术、接口时序断言监控技术,分别从验证计划制定、平台搭建、验证管理与验证结果分析等方面,介绍一种新型的基于统一覆盖率加速功能验证收敛的闭环验证方法。结合UVM验证方法学和断言技术,详细论述构建一种高效率可重用、快速收敛的验证平台的过程。

UVM;VM;验证计划;验证平台;覆盖率

0 引 言

过去10年,设计方法和技术变得越来越成熟和稳定,而功能验证技术的发展已经超越人们的认知水平,验证方法学和技术不断的演化,新的流程和工具不断被发明出来。在这种快速变化的大背景下,设计的稳定增长将更多更复杂的IP集成到越来越大的SoC复杂系统当中[1],如何采取更好的验证流程和验证方法加快复杂设计功能验证的收敛成为难题。

文中以某航电系统控制接口模块为例,采用基于统一覆盖率验证管理技术、UVM验证技术、接口时序断言监控技术,分别从验证计划制定、平台搭建、验证管理与验证结果分析等方面,介绍一种基于统一覆盖率加快功能验证收敛的闭环验证方法。

1 主机接口模块

应用于航空电子的通信、导航、识别(CNI)系统中的某产品主机接口模块主要实现了外部处理器MPC8270对模块内部资源的访问控制,将处理器端的读写控制信号转换为模块内部的读写控制逻辑,保证外部处理器能正确访问模块的内部寄存器和存储器资源。外部处理器通过主机接口模块来完成对某产品的配置和数据交互功能,因此对主机接口模块进行充分的功能验证具有重要意义。

模块功能框图如图1所示。

图1 主机接口功能框图

2 验证实施过程

任何管理过程应该需求清晰和目标明确,IC设计的功能验证也不例外。为了保证IC设计的关键功能不出现问题,需要定义验证计划。传统的验证计划不具有可执行性或维护性,只能人为根据验证列表和验证结果“PASS”与否去判断验证是否完备,是否完成,没有一个确定性判断指标来保证验证是否可靠地达到目的,项目流片存在较大的失败风险[2]。

文中将结合最新的UVM验证技术、基于统一覆盖率的验证管理技术,通过对控制接口模块的验证,介绍一种闭环的新型验证流程,见图2[3]。

图2 闭环验证流程图

闭环验证流程管理过程具有直观、可追踪、可控制等优点,通过验证结果分析不断迭代优化验证方案和验证流程,使模块验证工作快速收敛。闭环验证流程能最大限度降低大项目流片失败的风险,可以减小整个项目验证团队的巨大压力。

2.1 创建验证计划

制定验证计划的目的是有效控制整个验证流程,利用验证计划不断度量验证进行的程度,这可以衡量最终以流片为目的的差额工作量[4-5]。

验证计划制定应该遵循以下原则[6]:

(1)验证计划是一个全面的需要精心策划的验证列表,包括定义所有功能验证点、所有覆盖率(代码覆盖率、功能覆盖率、断言覆盖等)的要求[6-7]。

(2)验证计划应能捕获验证过程的目标,如验证活动停止标准应该清晰明确,或一个验证团队定义当验证活动覆盖到75%列表特性时,RTL代码就可以冻结了[8-10]。

(3)验证计划应具有可执行性,易自动度量。

(4)验证计划要定义验证功能点的优先级、验证人员名单、管理人员名单、项目名称、项目进展等,此外还包括验证采用的工具,如要使用的脚本、仿真器、采用的语言及其验证方法学等[10-12]。

(5)验证计划的重用性。该验证计划将会在控制接口模块的虚拟原型验证中重用。

该验证平台的验证计划使用mentor公司的AddIn工具实现。

2.2 验证平台搭建

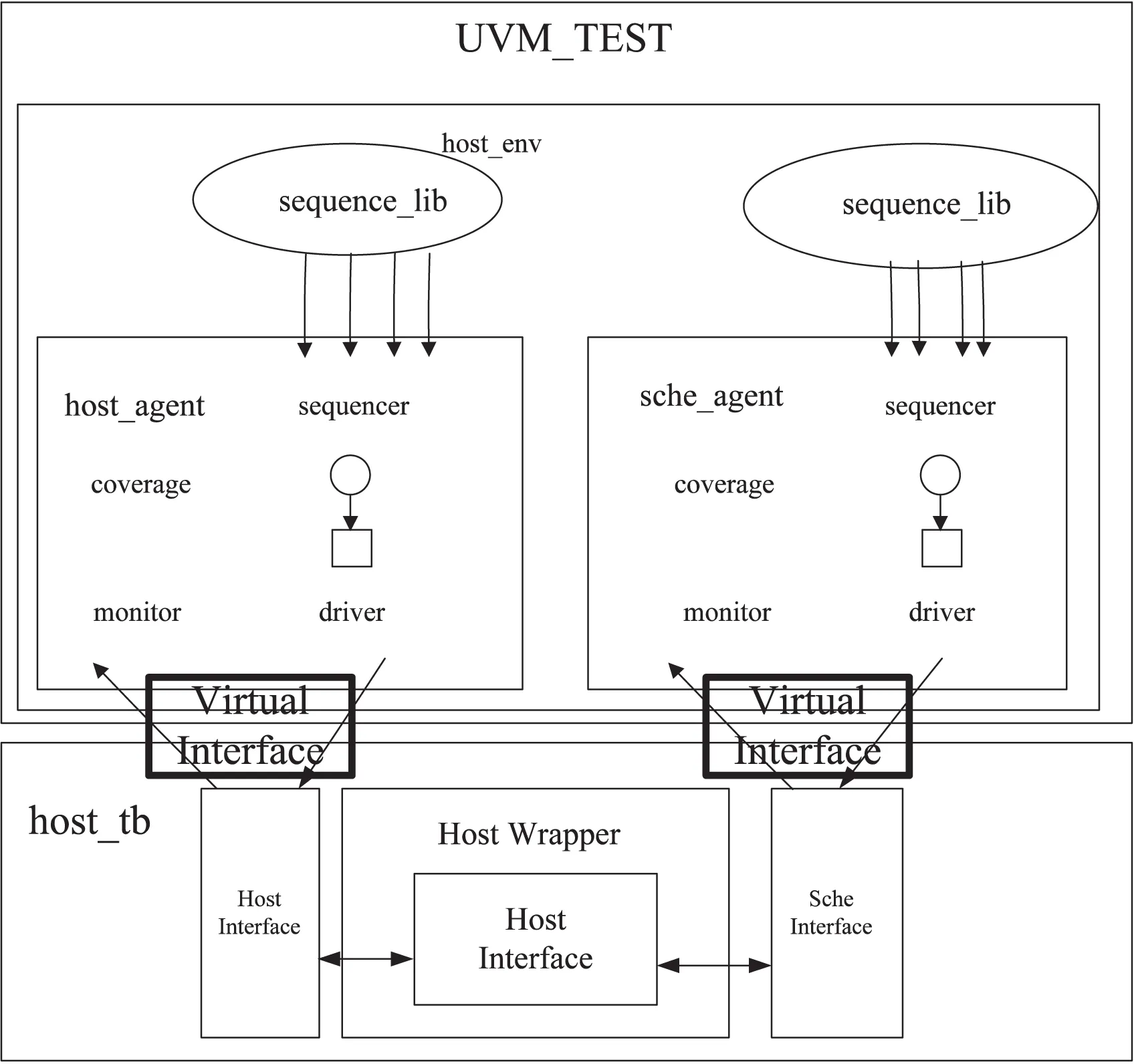

验证平台采用基于SystemVerilog的UVM验证方法学构建,如图3所示。

图3 主机接口模块验证平台框图

下面从自底向上的顺序简述验证平台的构建过程。

(1)Interface,是连接主机接口模块和验证环境接口的一些信号集合,如以下代码所示。

interfacehost_interface #(parameter setup_time =1 ns,parameter hold_time= 1 ns);

logic HSTREGCSn=1'b1;

logic HSTWRn=1'b1;

logic HSTPSDVAL='Z;

bithas_checks=1;

clocking Cb_host_if @(posedge HSTCLK);

default input #setup_time output #hold_time;

input HST_RST_N;

output HSTREGCSn HSTWRn;

inout HSTPSDVAL;

…

在多接口的复杂设计中,团队成员完成了设计集成后,模块间接口互操作时,难免出现非期望的结果。如果根据仿真最终结果判断出现异常情况,而逐个排查必然要花费大量的时间,虽然并发断言很难添加到UVM验证环境当中,但依然可以采用基于Systemverilog的SVA并发断言技术,精确描述模块接口处信号的时序关系,实时监测和诊断模块运行时是否与设计的接口时序关系一致,在发现错误时尽可能减少调试时间。

图4为主机接口仿真运行到t=1 220ns时发生断言失败的ATV(AssertionThreadViewer)窗口,该窗口可方便调试SystemVerilog断言。

always@(posedgeHSTCLK)

begin

assertHSTPSDVALnUnkown_a:assertproperty(disableiff(!has_checks)

($rose(~HSTREGCSn&HSTWRn)|->## [10:11] $fell(HSTPSDVAL)));

assertHSTPSDVALnUnkown_c:coverproperty(disableiff(!has_checks)

($rose(~HSTREGCSn&HSTWRn)|-> ##[10:11]$fell(HSTPSDVAL)));

…

图4 调试断言的ATV窗口

(2)virtualinterface,即虚接口,是连接DUT和验证环境接口的例化,验证平台通过驱动虚接口信号翻转,把激励施加到DUT上。

(3)driver,相当于总线功能模型(BFM),有pull和push两种模式。推荐采用pull模式,通过事务级TLM接口的方法发起新事务请求,并将获得的事务转换为接口信号的翻转,代码如下所示。

classhost_driverextendsuvm_driver#(host_trans) ;

foreverbegin

seq_item_port.get_next_item(req)

case(trans.kind)

REG_WR:reg_write(req) ;

REG_RD:reg_read(req);

…

(4)uvm_transaction,是验证组件sequencer和driver之间通信时的事务载体,如该平台host_agent中,host_trans就是事务载体,其包含了由sequence发出的读写类型、地址和数据,其部分代码如下。

classhost_transextendsuvm_sequence_item;

randtrans_tkind;

randbit[15:0]addr;

randbit[31:0]data;

…

(5)Sequencer,控制sequences的产生,并把sequence激励传递到driver。

(6)Sequence_lib,即包含了很多sequence的集合,sequence是事务级激励。

(7)Monitor,用来监控接口事务,并将监控的数据广播到覆盖率收集组件。

(8)Coverage,主要完成功能覆盖率统计,功能覆盖率的实现不是自动的过程,需要对功能规范进行详细分析,使用SystemVerilog覆盖率语法构建覆盖率模型结合仿真运行的一种统计过程。如下代码是用覆盖组进行读写信息收集,结合地址信息,可以判断整个验证过程对所有分配地址空间是否进行覆盖。

covergrouphost_cov;

OPCODE:coverpointanalysis_txn.we{

binswrite={0};

binsread={1};

}

endgroup

2.3 验证管理与验证结果分析

该模块验证采用Mentor的VM(Verification Management)技术来管理整个验证过程,通过验证计划的输入、平台构建和运行,验证计划和回归测试后,统计功能覆盖率、代码覆盖率、断言覆盖率的映射结果,分析优化验证方案。通过整个过程不断迭代,加快功能验证的收敛,整个验证过程具有可控性。

回归测试1次完成后,验证计划与覆盖率数据统计映射关系如图5所示。

图5 回归测试后覆盖率的映射关系

在测试项中,深色0%的验证项是没有执行过的,验证管理人员可以督促验证人员尽快进行验证项的开发。所有验证项运行后,显示的所有代码覆盖率、功能覆盖率统计如果达不到要求,需要验证人员对验证结果进行分析优化,删除对覆盖率没有帮助的冗余验证项,根据未覆盖到的场景修改开发更多的验证项,并可能与设计人员沟通,删除可能存在的冗余逻辑,从而使整个验证过程可控和快速收敛。当覆盖率达到100%或预期覆盖率时,验证过程结束。

3 结束语

在验证主机接口模块过程中,在任意时刻都可以很容易采用图形化界面或HTML报告的形式,回答项目管理者的问题,如“验证进程到达哪一步了”“何时验证可以收敛”。闭环的验证流程增加了验证项目的可见性,使验证工程师和项目管理人员交流起来方便容易,进一步提高了验证效率,降低了验证工作的时间[1]。

[1] Bhattacharya B,Decker J,Hall G.Advanced Verification Topics[M].[s.l.]:Cadence Design Systems,Inc.,2012.

[2] May D.Process management:are you driving in the dark with faulty headlights[M].[s.l.]:[s.n.],2013.

[3] Idrissi R E.ST-Ericsson speeds time to functional verification closure with the questa verification platform[M].[s.l.]:ST-Ericsson,2012.

[4] Lam W K.Hardware design verification:simulation and formal method-based approaches[M].[s.l.]:[s.n.],2005.

[5] Processorlocal bus functional model toolkit[M].USA:IBM,2003.

[6] 韩 霞,杨洪斌,吴 悦.面向SoC的事务级验证研究[J].计算机技术与发展,2007,17(3):33-36.

[7] 华为技术有限公司.一个成功的百万门级芯片验证平台[J].中国集成电路,2005(6):36-43.

[8] 杨海波,田 泽,蔡叶芳,等.FC IP软核的仿真与验证[J].计算机技术与发展,2009,19(9):168-172.

[9] 李 哲,田 泽,张荣华.AFDX网络交换机芯片关键性能验证方法研究[C]//第十六届计算机工程与工艺年会暨第二届微处理器技术论坛文集.出版地不详:出版者不详,2012:483-486.

[10] 田 靖,田 泽.AFDX-ES SoC虚拟仿真平台的构建与应用[J].计算机技术与发展,2010,20(8):192-194.

[11] 郭 蒙,田 泽,蔡叶芳,等.1553B总线接口SoC验证平台的实现[J].航空计算技术,2008,38(6):99-101.

[12] 吴晓成,田 泽,郭 蒙,等.AFDX交换芯片虚拟验证关键技术研究[J].计算机技术与发展,2013,23(8):177-180.

A Method of Speeding up Convergence Functional Verification Based on UVM

XU Wen-jin,TIAN Ze,WANG Shi-zhong,WANG Xuan-ming

(Key Laboratory of Aeronautics Science and Technology of Integrate Circuit and Micro-system Design,AVIC Computing Technique Research Institute,Xi’an 710068,China)

Functional verification is one of the most important steps in the IC design.With the increase of design complexity,the cost of locating defects is also raised.Many designers will be a great deal of efforts on the development of efficient verification.In this paper,a new type of closed-loop verification method based on uniform coverage is introduced,taking functional verification of the host interface module of CNI system as example,using authentication management technology based on uniform coverage,UVM verification technology,and monitoring interface timing assertions respectively from the verification plan,platform building,management and authentication results analysis,etc.The process of constructing an efficient,reusable and fast convergent verification platform is discussed in detail by combining UVM verification methodology and assertion technology.

UVM;VM;test plan;test bench;coverage

2015-08-31

2015-12-09

时间:2016-05-25

中国航空工业集团公司创新基金(2010BD63111)

徐文进(1983-),男,工程师,研究方向为集成电路设计与验证;田 泽,博士,研究员,中国航空工业集团首席技术专家,研究方向为SoC设计、嵌入式系统设计、VLSI设计等。

http://www.cnki.net/kcms/detail/61.1450.TP.20160525.1700.010.html

TP39

A

1673-629X(2016)06-0111-04

10.3969/j.issn.1673-629X.2016.06.024