集成电路老化测试系统的数据通信接口设计

2016-01-22胡舜峰张福洪陈妍芬徐春晖

胡舜峰,张福洪,陈妍芬,徐春晖

(杭州电子科技大学通信工程学院,浙江 杭州310018)

集成电路老化测试系统的数据通信接口设计

胡舜峰,张福洪,陈妍芬,徐春晖

(杭州电子科技大学通信工程学院,浙江 杭州310018)

摘要:新一代大规模集成电路高温动态老化系统的设计是近年来研究的热点。以现场可编程逻辑门阵列作为核心平台,通过高速数据接口,将上位机中的数据传输到老化测试芯片中,同时把老化过程中的相关数据反馈回上位机。通过FPGA软硬件平台验证表明,该数据通信接口设计能够很好地完成集成芯片的老化过程,较传统的静态老化系统有很大的改进和提高。

关键词:集成电路;动态老化;接口设计;现场可编程逻辑门阵列

0引言

随着信息产业的快速发展,半导体集成电路被广泛地应用于通信、电子、计算机等相关的各个领域[1],集成电路的可靠性问题也得到越来越多人的关注。因此制造商对生产出的芯片进行出厂前的测试是必不可少的,比如在高温环境下对芯片供给正常值以上的电压,不断地给予动态信号等。但这些常用的方法并不高效,老化的成本也较高,如果在这些方法的基础上加上一些必要的功能测试,收集故障点的一些有用信息,是比较合理的方法。集成电路高温动态老化测试就是在高温下对芯片施加应力的同时进行各类功能测试,让芯片超负荷工作而使其缺陷加速暴露,从而剔除有故障芯片的过程[2]。本文设计了一种数据通信系统,以Altera公司的Cyclone系列现场可编程门阵列(Field-Programmable Gate Array,FPGA)芯片EP3C16Q240C8为核心,结合三星公司的16/32位高级精简指令集微处理器(Advanced RISC Machines,ARM)芯片S3C2440A,采用并行处理和流水线技术,完成整个集成电路动态老化的测试过程。

1系统总体设计

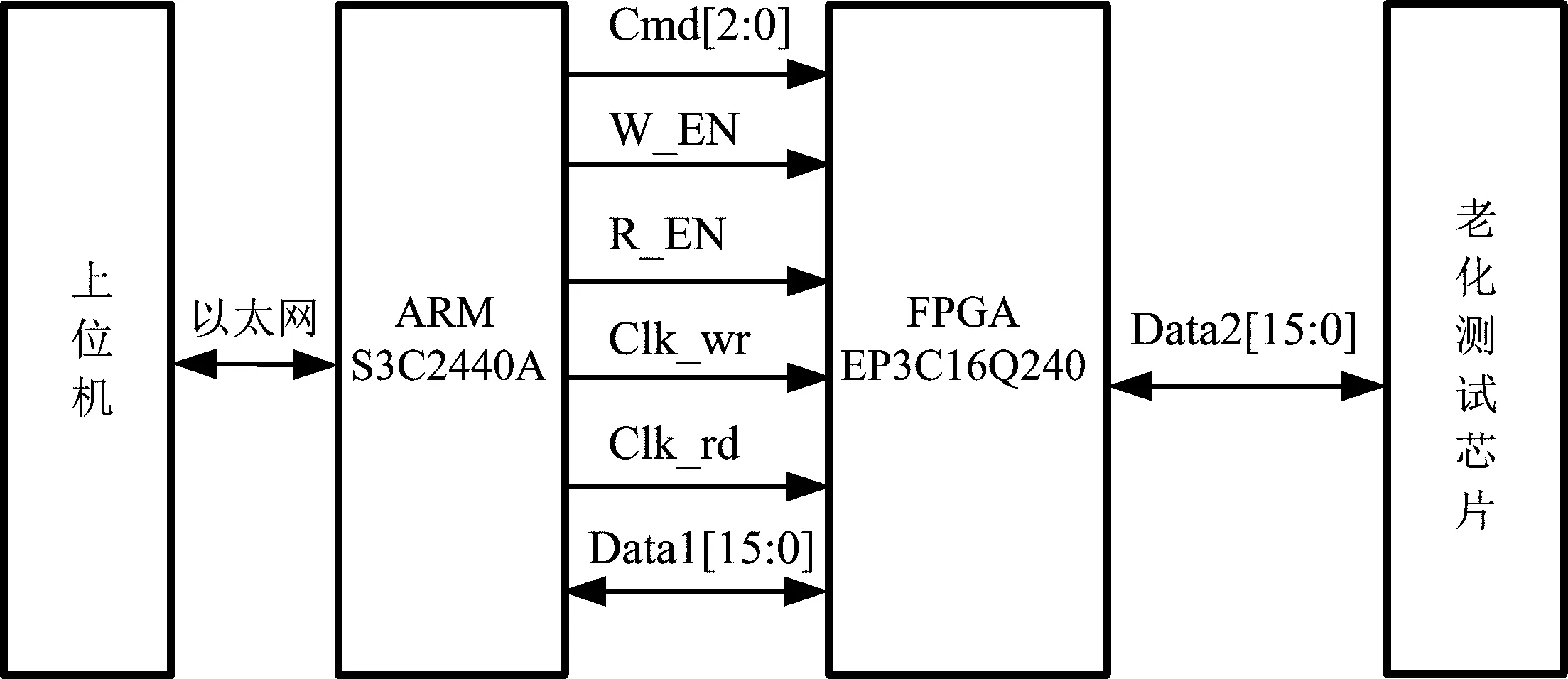

本文设计的系统总体结构如图1所示。

图1 系统总体结构

S3C2440A采用了新的总线架构如先进微控制总线架构,低功耗,简单,精致,且全静态设计特别适合于对成本和功率敏感型的应用[3]。EP3C16Q240C8拥有丰富的I/O资源和逻辑资源,具有高速并行处理能力,在数据采集领域具有重要的应用价值[4]。两者之间的信号传输方式采用外部总线:指令Cmd[2∶0],数据Data1[15∶0]。FPGA受ARM写使能W_EN和读使能R_EN的控制,当W_EN为低电平时,ARM在写时钟Clk_wr的上升沿将相应的数据通过16位数据总线Data1写入到FPGA中,此时FPGA内与16位数据总线相对应的IO口全部变成输入状态;当R_EN为低电平时,ARM在读时钟Clk_rd的上升沿通过16位的数据总线Data1从FPGA中读取相应的数据,此时FPGA内与16位数据总线相对应的IO口全部变成输出状态。上位机中的数据通过以太网传输到ARM中,最终通过流水线技术储存到FPGA内部的RAM中;同时FPGA也时刻接收来自测试芯片反馈回的数据,将其保存到内部的另一块RAM空间中。由于RAM空间有限,反馈回的数据将不断地被新接收到的数据刷新。

RAM内部储存的数据如图2所示。数据帧长度即上位机一个周期内需要给测试芯片发送的老化测试数据的数据总量,在这里以16 bits为一帧;理论反馈数据为在测试芯片正常工作的情况下理论上应得到的反馈数据;老化测试数据经上位机向ARM发送后存入FPGA内部的RAM后,FPGA以自身内部独立的时钟将此数据通过双向总线Data2[15∶0]的形式不断地发送到老化测试芯片中,与此同时测试芯片也将通过Data2不断地向FPGA发送老化反馈数据。最终FPGA将理论上的反馈数据和老化反馈数据进行数据比对处理,得到老化测试错误报告数据上传到上位机。由于不同的老化测试芯片有着不同的管脚定义,导致Data2总线的16根数据线的输入/输出状态并不是确定的,需要FPGA通过上位机向ARM发送的16位IO口状态数据进行配置。

图2 RAM内部储存的数据

2FPGA内部模块的设计

2.1 模块的总体设计

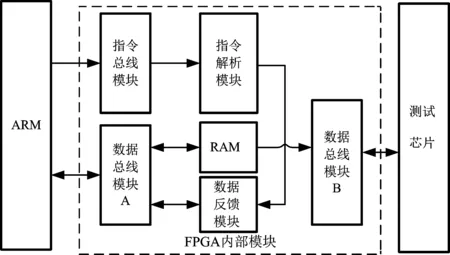

FPGA内部模块结构如图3虚框内所示。

图3 FPGA内部模块结构图

FPGA内部中的指令总线模块的功能是FPGA接收来自ARM的相应指令,通过指令解析模块,将ARM送到数据总线上的数据存入到片内的寄存器中,于此同时FPGA通过数据反馈模块将数据的接收成功或失败的状态反馈回ARM。数据总线模块A的功能是当ARM向FPGA读取数据时,总线的模式被配置成输出;而当ARM向FPGA写入数据时,总线的模式被配置成输入[5]。数据总线模块B根据16位IO口状态数据配置16位双向总线的输入输出模式,如果IO口状态为1,则总线中相对应的数据线的模式为输出,FPGA向测试芯片写数据;如果IO口状态为0,则总线中相对应的数据线的模式为输入,FPGA从测试芯片中读数据。

2.2 模块的软件设计

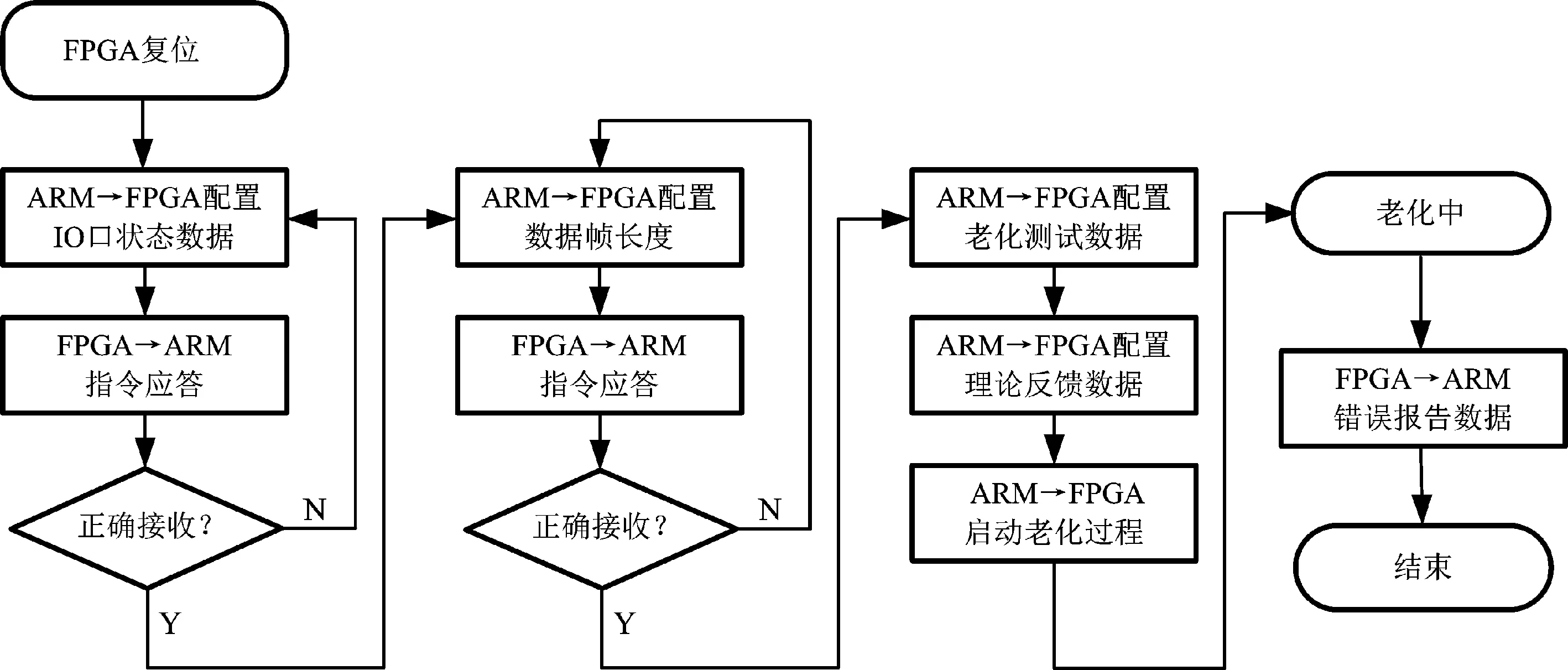

本文设计的系统中,ARM负责在每次老化过程实施前,完成向FPGA传送工作指令、配置参数、老化测试数据、用来比对的正确结果预期图案;FPGA则根据工作指令完成向ARM反馈测试结果信息的任务。本系统中ARM和FPGA之间的协议流程图如图4所示。

图4 协议流程图

FPGA经过系统复位后,ARM将给FPGA发送相应的数据,如果经奇偶效验后数据被成功接收,FPGA通过16位的数据总线给ARM发送回FFFFH的数据,随后ARM将给FPGA发送协议流程中下一个环节的数据;如果经奇偶校验后数据接收失败,FPGA通过16位的数据总线给ARM发送回0000H的数据,ARM将给FPGA重新发送协议流程中上一个环节的数据。

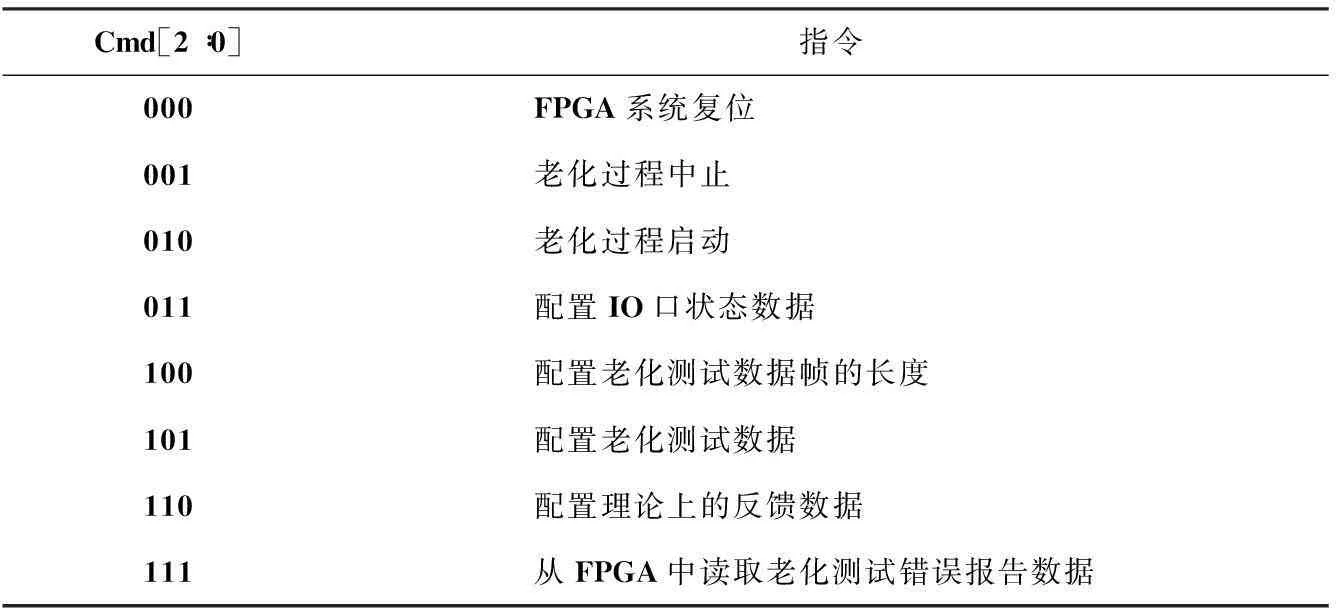

对于ARM向FPGA传送的指令模式Cmd[2∶0],如表1所示。

表1 指令模式

FPGA内部模块的指令解析和数据处理采用有限状态机的形式进行描述。本系统中共有8个状态:系统空闲Idle、老化过程中止Lh_stop、老化过程启动Lh_start、配置测试数据帧长度Data_lgth、配置IO口状态数据Io_data、配置老化测试数据Lh_data、配置理论上的反馈数据Fd_data、读取测试错误报告数据域Error_data。FPGA根据ARM发送的指令数据Cmd[2∶0],使状态机进入相应的状态,处理相应的命令。

RAM模块由Altera公司提供的IP核生成。本系统中共使用了3块RAM空间,分别用来存储老化测试数据、理论和实际反馈数据。

3测试结果

采用74LS04作为系统的测试芯片,行走walking算法实现激励信号图案的产生。在Quartus 9.1开发平台下使用Verilog HDL语言测试该系统。使用逻辑分析仪随机抓取各信号的时序效果如图5所示。

时序中IO口状态数据IO_data为16’h00ff,测试数据帧长度Data_lgth为255。当实际反馈数据Sj_Fd_data和理论反馈数据LI_Fd_data不同时Error_data的值累加1。

4结束语

本文设计的数据通信系统实现一个自动控制老化作业的过程。经软硬件验证,该系统能够很好地应用于集成电路动态老化测试平台。经实际测试,该系统工作稳定可靠,老化自动化程度高,具有较好的应用前景。

参考文献

[1]温平平,焦慧芳,贾新章,等.VLSI老化筛选试验技术的挑战[J].电子产品可靠性与环境验,2004,10(2):21-24.

[2]贾建革,段新安,李咏雪.VLSI超大规模集成电路测试和验证的发展趋势[J].中国测试技术,2005,31(6):94-96.

[3]施智雄,胡玉红.基于ARM9控制的二氧化碳生物反应器系统[J].农机化研究,2009,(7):89-92.

[4]吴继华,蔡海宁,王诚.Altera FPGA/CPLD设计[M].北京:人民邮电出版社,2011:43-45.

[5]陈鑫旺,姜秀杰.基于嵌入式Linux和FPGA的数据通信系统设计[J].微计算机信息,2012,28(6):76-78.

Design of Data Communication Interface and Its Application for Integrated Circuit Burn-in Test Device

Hu Shunfeng,Zhang Fuhong,Chen Yanfen,Xu Chunhui

(SchoolofCommunicationEngineering,HangzhouDianziUniversity,HangzhouZhejiang310018,China)

Abstract:How to design a new generation of high-temperature dynamic burn-in system LSI is a hot issue in recent years.In this paper,we use field-programmable gate array(FPGA) as a key design platform of the whole system,let the data in host computer transmit to the aging test chip,meanwhile the aging process relevant data feedback to the host computer,through a variety of high-speed data interface.Some experiments and tests based on FPGA show that the data interface can well complete the dynamic burn-in process,has greatly improved and enhanced comparing with the traditional static system.

Key words:integrated circuit;dynamic burn-in;interface design;field-programmable gate array

中图分类号:TP274+.5

文献标识码:A

文章编号:1001-9146(2015)06-0046-04

通信作者:

作者简介:胡舜峰(1989-),男,浙江磐安人,在读研究生,电子与通信工程.张福洪教授,E-mail:fuhong@vip.sina.com.

收稿日期:2014-11-03

DOI:10.13954/j.cnki.hdu.2015.06.010