基于TRF3765的本振源设计

2016-01-05王永升臧小杰

王永升++臧小杰

摘要:介绍了一款具有宽频带压控振荡器的频率合成器TRF3765的功能特点。基于MSP430F169单片机的SPI通信和TRF3765的工作原理,给出了1090MHz本振源系统的设计,应用于ADS-B时钟输入。详细介绍了TRF3765芯片的结构、原理和应用,并给出了完整的硬件电路和软件程序。经实物测试,该系统的性能指标完全符合要求。

关键词:压控振荡器;TRF3765;MSP430F169;SPI通信;1090MHz

中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2015)29-0202-04

1 引言

在无线通信领域,本振信号性能的优劣是影响混频器输出频谱纯度的主要因素[1]。

频率合成技术作为现在电子系统中的一种关键技术,广泛应用于通信、雷达、电子对抗、定位导航、广播电视、遥测遥控、仪器仪表等领域并得到了快速的发展。该技术是参考一个或多个高精度的离散频率,对频率进行加、减、乘、除等一系列变换,产生同样高精度的大量离散频率[2-3]。本文运用频率合成技术设计一款能够精确产生1090MHz频率的本振源系统。

2 工作原理

2.1 TRF3765的工作原理

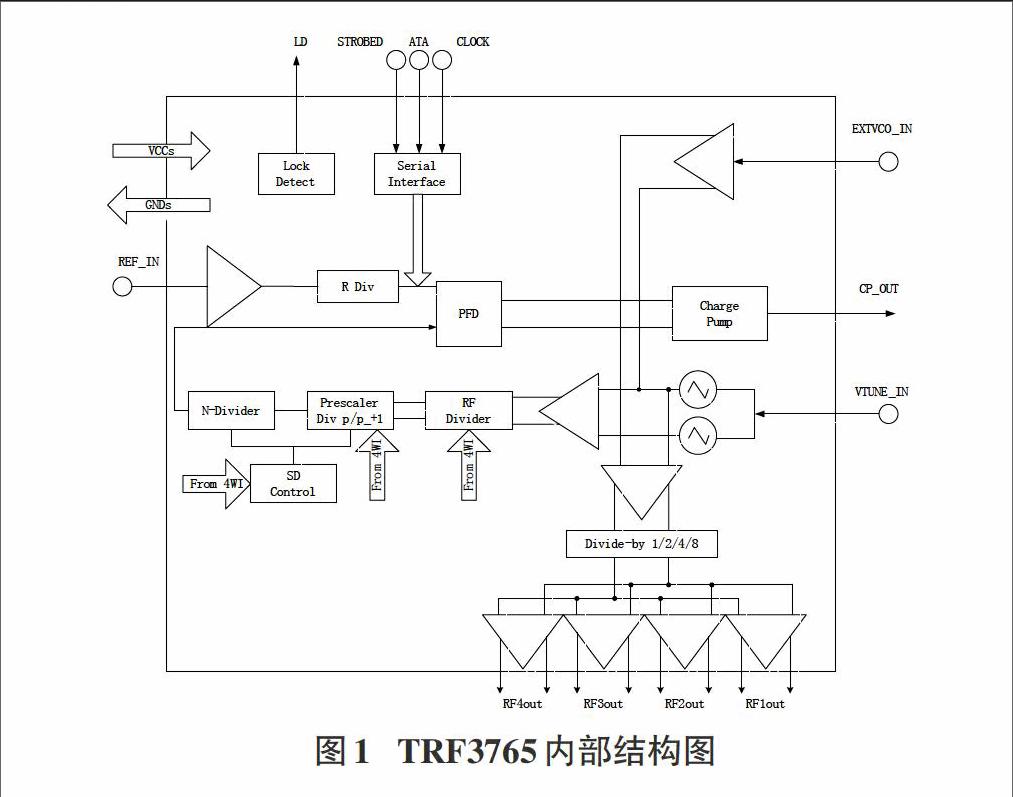

TRF3765 是一款宽频带整数、分数频率合成器,此合成器具有集成的宽频带压控振荡器 (VCO)。可编程输出分压器可实现300MHz至4.8GHz 频率范围的连续覆盖。4个单独的差分、开集 RF 输出可在无外部分离器的情况下并行驱动多个器件。TRF3765也接受外部VCO输入信号,并且可通过一个可编程控制输出来实现开/关控制。TRF3765的内部结构图如

TRF3765的外部输入频率源有外部参考频率源和外部压控振荡器频率源。外部参考频率经过参考分频器(R Div)生成内部参考频率,输入到相位探测器;外部压控振荡器输入端可以将此频率作用在内部压控振荡器上,供系统使用。控制信号由时钟信号(CLK)、 数据信号(DATA)和锁存信号(STROBED)组成。写操作时,在时钟信号的控制下串行输入32位数据信号, 暂存在32位移位寄存器中。在接收到锁存信号后,输入的32位数据根据地址位到达对应的寄存器。读操作时,首先完成一次对寄存器0的写配置,设置寄存器0为读模式以及指定将要读取数据的寄存器;在时钟信号的控制下,内部的数据被传递到READBACK引脚。

TRF3765的锁相环有两种操作模式:整型模式和分数模式[5]。如果所需的本振频率是相频探测器频率的整数倍,整型模式可以被使用;否则运用分数模式。锁相环环路图表如图2所示。

R分频器将外部参考输入频率进行分频得到相位探测器的频率。反馈环路由RF分频器、预分频器、NINT分频器和NFRAC分频器组成,压控振荡器输出频率经过反馈回路输入到相频探测器,从而将频率进行锁定。值得注意的是:TRF3765拥有八路本振频率输出端。

2.2系统的组成分析

频率合成部分采用TRF3765芯片。TRF3765运用25位分数和整数锁相环得到精确的0.5MHZ至350MHZ的频率。

控制器部分采用TI公司的MSP430单片机。MSP430F169不仅具有超低功耗的特点,而且拥有硬件SPI与UART,通过SPI与UART分别实现与TRF3765和上位机的通讯。多种省电模式结合硬件SPI使MSP430能够胜任工作。

操作显示部分采用Visual Studio开发的上位机。该上位机将计算好的寄存器数据写入TRF3765寄存器,并读出寄存器的数值进行核对。通过在调试端进行配置,开发者可以缩短开发周期。

TRF3765的通信是通过3脚(DATA)接收数据,通过6脚(READBACK)送出寄存器数据,通过4脚(CLOCK)接收时钟脉冲。MSP430F169采用硬件SPI实现对TRF3765的读写配置;采用硬件UART与上位机实现可视化的调试。

3 TRF3765电路设计

3.1 环路滤波器

在实现低的闭环相位噪声方面,环路滤波器的设计是至关重要的[4]。这里我们采用的是8M晶振作为参考输入时钟,经过四分频,得到fPFD为2MHZ。元件参数如表1所示,环路滤波器电路设计如图3所示。为了实现最小的噪声,环路滤波器设计了1.94mA的泵电流。

4 TRF3765软件设计

4.1 时序分析

TRF3765以四线串行编程为特点,可以控制内部的32位移位寄存器。它有三个信号端必须使用:时钟信号引脚4、串行数据引脚3和锁存使能引脚5。寄存器串行数据从最低位开始装载,并在时钟的上升沿写入数据。锁存使能端与时钟信号同步;在它的上升沿,转换寄存器的数据被装载到内部寄存器中。

通过初始化寄存器0,TRF3765可以读回每一个串行编程接口寄存器的内容。每一个读操作由两个阶段组成:写寄存器和读寄存器。写阶段,在配置寄存器0,设置读模式并选择读取的寄存器;在读阶段,TRF3765在时钟的上升沿将数据转换到READBACK引脚,并稳定于接下来的下降沿。写时序如图5所示,读时序图如图6所示。

图5 写时序图

图6 读时序图

4.2 整型模式配置分析

这里采用8M有源晶振作为参考时钟输入源,期望得到的是输出频率是1090MHz,寄存器参数的配置与计算方法如下所示。

[fREF=8MHz];[StepRF=2MHz];[fRF=1090MHz];VCO的配置范围是2400MHz至4800MHz;因此,[LO_DIV_SEL=4];[fVCO=LO_DIV_SEL*fRF=4360MHz];为了使预分频器的输入频率小于3000MHz,取[PLL_DIV_SEL=2],得到[fPFD=fREF/PLL_DIV_SEL=2MHz],最终我们得到其它的寄存器参数:

[RDIV=fREF/fPFD=4];[NINT=(fVCO*RDIV)/(fREF*PLL_DIV_SEL)=1090];

因为NINT大于75,因此,选择8/9预分频器。

[fN,MAX=4360MHz/(2*8)=272.5MHz<375MHz];满足TRF3765配置要求。寄存器1至寄存器6的配置分别为:0X41100089、0X8A0884A、0X0B、0X4A00E00C、1DA6968D、5541100E。程序流程图如图7所示。

图7 程序流程图

4.3 TRF3765配置程序

SPI初始化操作:8位SPI主模式,时钟源设置为SMCLK,三线模式,上升沿数据有效,设置时钟频率为4MHz。下面是TRF3765的寄存器配置和寄存器信息读出程序。

void trf_wr(uchar com1,uchar com2,uchar com3,uchar com4)

{

uchar i;

uchar frame[4];

frame[0]=com1;frame[1]=com2;frame[2]=com3;frame[3]=com4;

for(i=0;i<4;i++)

{

SPI_SER(0);

trf_latch_l;

trf_latch_h;

trf_latch_l;

while (!(IFG1 & UTXIFG0));

TXBUF0=frame[i];

trf_latch_h;

trf_latch_l;

}

}

void trf_config(void)

{

trf_wr(0x89,0x00,0x10,0x41);

trf_wr(0x0B,0x00,0x00,0x00);

trf_wr(0x0C,0x00,0x00,0x4A);

trf_wr(0x8D,0x96,0xA6,0x1D);

trf_wr(0x0E,0x10,0x41,0x55);

trf_wr(0x0A,0x99,0x80,0x08);

}

uchar trf_rd(uchar com1)

{

uchar i,j;

uchar frame;

frame=com1;

for(i=0;i<6;i++)

{

SPI_SER(0);

SPISENDBYTE(0x08,0x00,0x00,0xc0,frame);

SPI_SER(1);

trf_latch_h;

trf_clock_h;

trf_clock_l;

trf_latch_l;

SPI_SER(0);

for(j=0;j<6;j++)

{

while (!(IFG1 & UTXIFG0));

com[j]=RXBUF0;

}

}

}

5 总结

设计中有两点必须注意:因为当寄存器2的第31位被写入后,TRF3765配置便会进行更新,所以寄存器2应该最后配置,其他的寄存器首先配置;输入参考时钟往往不是整数,要得到准确的输出频率只能够借助分数模式进行调整。

本文介绍了利用具有压控振荡器的频率合成器TRF3765实现1090MHZ频率本振信号源的设计,提供了具体的硬件设计、寄存器参数、设计算法以及部分程序代码。实验测试得到的相位噪声为-117dBc/ Hz @1 kHz , 达到了基本标准。因为TRF3765 采用四线串行通信方式,单片机可以通过SPI与TRF3765进行通信。因此,该系统的硬件电路设计简单,串口读写易于调试、功耗非常低,可以在射频电路系统和无线通信系统中进行推广。

参考文献:

[1] 邹玲,石小磊.基于ADF4360-1的本振源设计[J].现代电子技术,2009(21):71-73.

[2] 任鹏,周资伟,朱江.一种基于DDS和PLL技术本振源的设计与实现[J].现代电子技术,2009(9):178-180.

[3] 张厥胜,曹丽娜.锁相与频率合成技术[M].成都:电子科技大学出版社,1995 .

[4] Texas Instruments.TRF3765 Integer/Fractional-N PLL With Integrated VCO Evaluation Module[Z]. 2011-2012.

[5] Texas Instruments. Integer-N/Fractional-N PLL with Integrated VCO Datasheet[Z].2011-2013.