消除锁相环中由于短沟道效应导致的抖动

2015-12-31李龙镇

李龙镇

(延边大学工学院计算机系,吉林延吉,133002)

0 引言

锁相环技术自从在1930 年问世以来,虽然其基本结构虽着时间的进程没有发生多大变化,但其各个组成部分一直被业界研究并得到显著的改善。目前,由于电子产品的小型化和微型化,移动通信、掌上电脑等各种微型终端更是提高了对锁相环技术的相关要求,因此,国内外对锁相环技术展开了深入的研究。

本文采用 Magnachip 0.13 μm 工艺设计了455MHz 锁相环,并在设计中克服了短沟道工艺中漏栅电容所带来的影响,实现了低功耗、快速锁定的特点。

1 电路设计

1.1 总体结构

锁相环系统如图1 所示,电路可分为5 个基本模块(鉴相鉴频器、电荷泵、低通滤波器、电压控制振荡器和分频器)。整个电路采用了负反馈技术,即输入的外部数字信号和反馈回来的内部振荡信号进行相位和频率比较,产生的数字信号相位差经过电荷泵转换为电流,然后经由低通滤波器转换成直流电压来控制电压控制振荡器来追踪输入数字信号的相位,并通过分频器得到相应频率的数字信号。

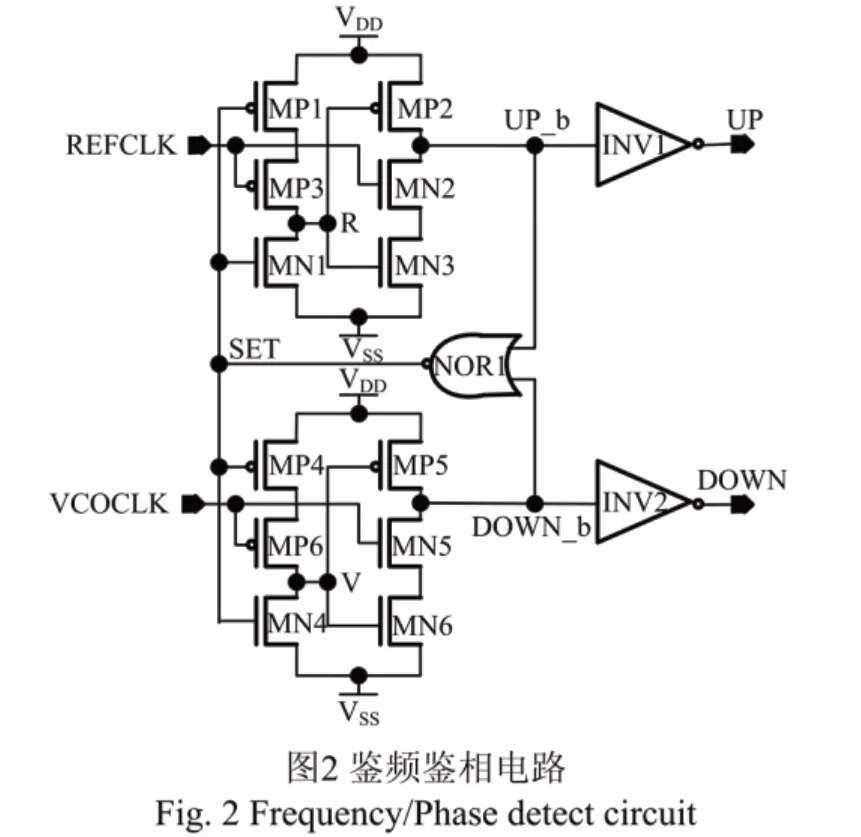

1.2 鉴频鉴相器

为了减少锁相环系统的锁定时间,本系统采用了图2 所示的预充电型鉴频鉴相器。该鉴频鉴相器是由Kondoh 提出,文献[6]中并有述及。电路的详细工作原理可参阅文献[4],基本工作原理简述如下:当参考信号REFCLK 和由振荡器产生的信号VCLOCK同时为高电平时,由于存储在R 点和V 点的电荷在高阻抗状态下短时间内保持不变,因此导致MN2、MN3、MN5 和MN6 导通,使UP_b 和DOWN_b 同时为低电平,SET 点设置为高电平,导致MN1和MN4 导通,导通的MN1 和MN4 使R 点和V 点上存储的电荷释放出去,即R 点和V 点的电压转换为低电平。(由于电路的上下两个部分完全相同,所以下面只分析上半部分电路),R 点的低电平又促使MN3 截止,MP2 导通,使UP_b 又回到高电平,使SET 点又转换为低电平,使MP1 导通,此时如果REFCLK 转换为低电平,则MP3 导通,使VDD 可以对R 点进行充电,电路又回到初始状态。这样通过对电路的分析,可以知道延迟时间仅为3 个门电路延迟时间,且该电路对输入信号占空比没有特别要求。

1.3 电压控制振荡器

为了抑制电源噪声的影响,在本设计中采用了如图3 所示的差分环形VCO 电路。其振荡器延迟单元电路如图4 所示,为了改善PLL 系统的抖动效应,需要降低振荡器延迟单元电路的增益,因此,在振荡器延迟单元电路中,采用了输出端和以二极管连接方式的NMOS 三级管并联来降低增益。

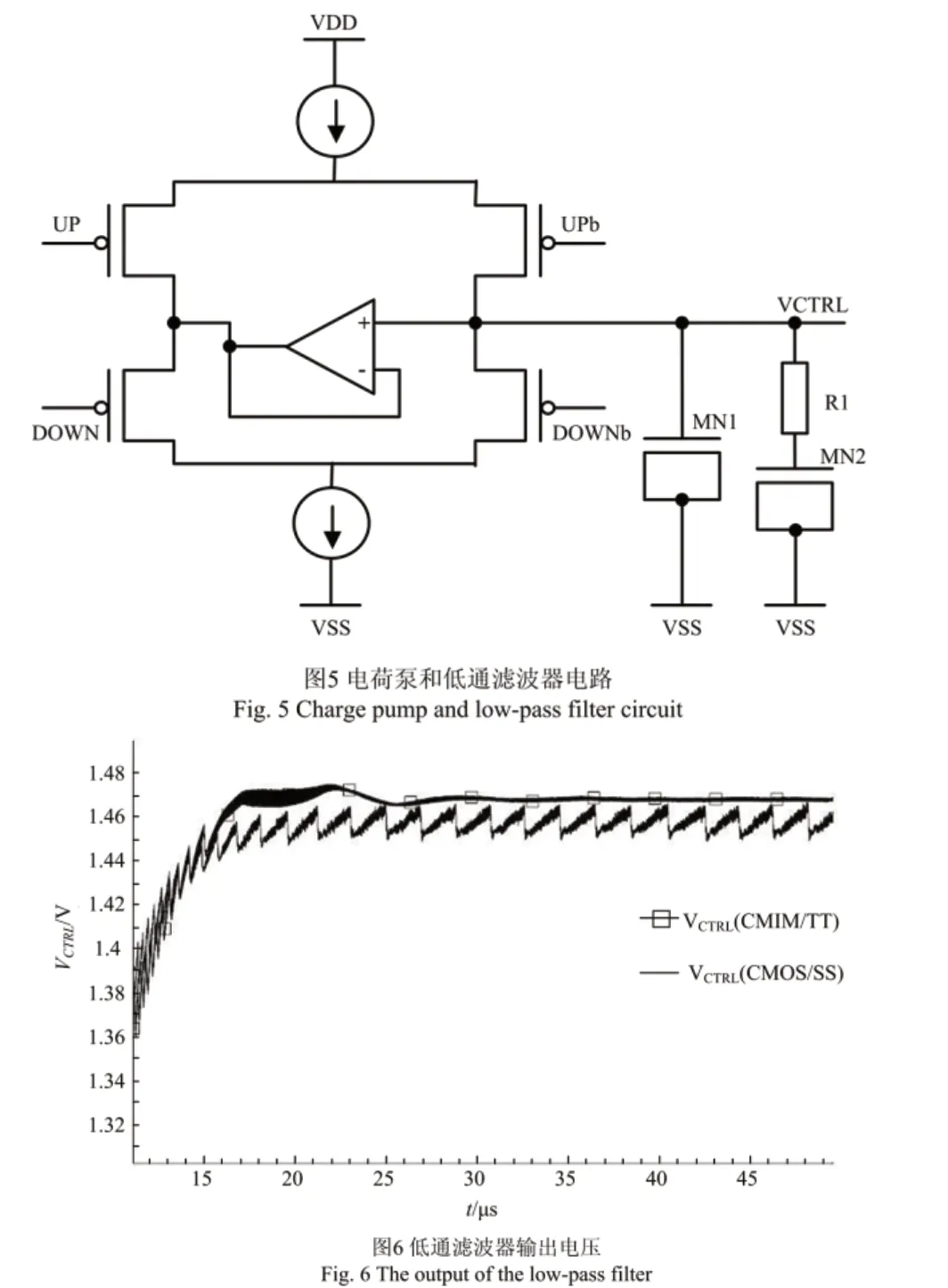

1.4 电荷泵、低通滤波器电路

电荷泵、低通滤波器电路如5 所示,在初步设计中,采用MOS三级管源极和漏极相连并和栅极构成的MOS 电容来作为滤波电容。通过Hspice 仿真测试发现整个PLL 系统出现相位锁定不住的现象。通过观察图6 中的低通滤波器的输出电压Vctrl,发现该电压出现抖动现象,而采用Magnachip 0.25μm 以及Magnachip 0.18μm 工艺实现的同样电路,却没有此现象。因此,可以断定是短沟道效应的影响。仔细分析发现噪音是通过振荡延迟电路(图5)的三级管MN3 和MN4 的栅漏交叠电容回馈给低通滤波器,并使图5 中的三级管电容 MN1 的容量随回馈信号发生了变化,即回馈的噪音信号对MN1 构成的电容实行了调制,导致锁相环出现永远锁定不住的现象。可以通过在滤波器和振荡电路间增加一个单位增益运算放大器来隔离回馈信号,但考虑到增加的运算放大器在信号的主要通道上,引入的零极点有可能对PLL 系统的稳定性产生影响,使锁相环设计复杂化。因此在本设计中采用了另外一种方法,即Magnachip 0.13μm 工艺提供了金属层-绝缘层-金属层(CMIM)电容,考虑到本设计中MN1 电容的容量为6.1pF,容量相对较小,可以用MIM 电容实现且不会增加多少芯片面积,并保证其电容容量不随回馈信号的调制发生改变。为了在一个图中进行比较,在图6 中分别绘制了在SS(Slow-Slow)工艺角条件下和TT(Typical-Typical)工艺角条件下的VCTRL 电压,从图中可以看出采用CMIM 后的低通滤波器的输出电压(TT 工艺)VCTRL 没有出现抖动现象。

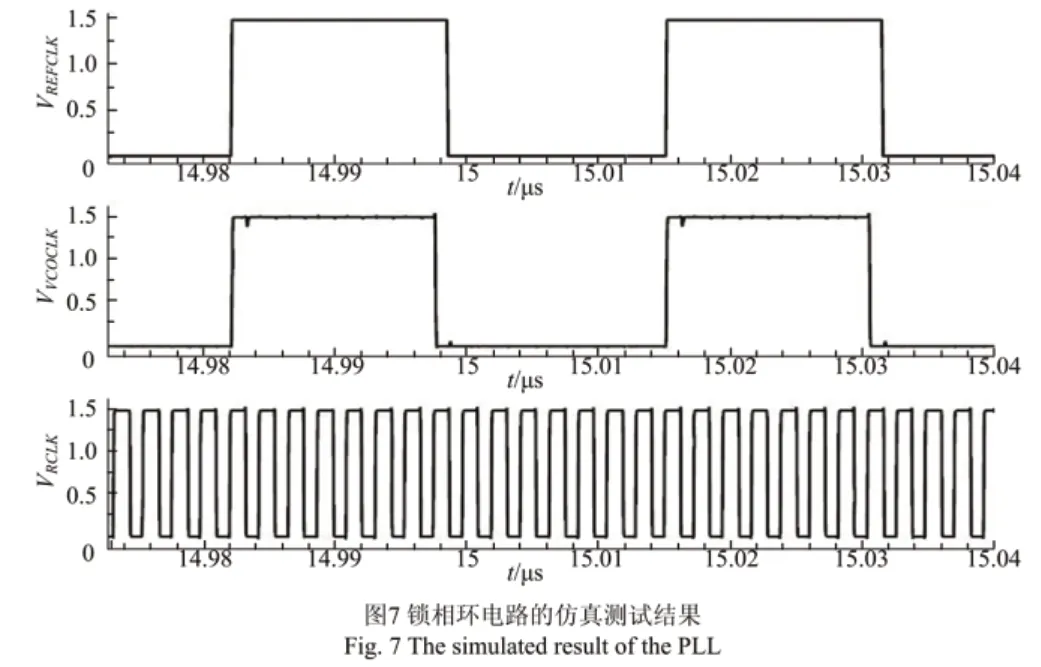

2 仿真结果

本设计采用Magnachip 0.13 μm 工艺实现了PLL 锁相环系统,整体电路的工作电压为1.5V。对设计的锁相环系统进行了仿真测试,结果如图7 所示。图中VREFCLK 为输入的参考脉冲,VVCOCLK 为锁相环振荡器产生的振荡信号经过分频后与VREFCLK相比较的反馈脉冲,VRCLK 为振荡器产生的振荡信号经过整形电路后形成整个锁相环的输出信号。仿真测试结果表明设计的锁相环电路能在455MHz 速率下可靠地工作,整个电路的功耗小于8mW,锁定时间小于15μs。

3 结论

本文阐述了一种采用Magnachip 0.13 μm 工艺实现的锁相环电路,其输出频率为455MHz。整个电路的功耗小于8mW,锁定时间小于15μs。并在文中介绍了一种如何消除由于短沟道原因而产生的回馈信号影响的方法,对于如何采用单位增益运算放大器来抵消回馈信号的影响有待于进一步的研究。

[1] 宋颖,王源,贾嵩等.一种低抖动、宽调节范围的带宽自适应CMOS 锁相环[J].半导体学报,2008,29(5):908-912

[2] 张序,于海勋.高性能电荷泵电路设计与HSPICE 仿真[J].微电子学,2010,40(3):317-320

[3] 梁岩,吴金.低抖动锁相环中压控振荡器的设计[J].微电子学,2009,39(1):29-33

[4] 任正权,李龙镇.CMOS 锁相环中快速鉴相鉴频器的设计[J].延边大学学报,2011,37(4):342-344

[5] KONDOH H.1.5-V 220-MHz to 3.0-V 622-MHz operation CMOS phase-locked loop with precharge type phasefrequency detector[J].IEICE Trans Electronics.1995,78-C(4):381-388

[6] 周海峰,韩雁,董树荣等.一种低功耗射频CMOS 电荷泵锁相环的设计[J].微电子学,2009,39(1):49-52