一种FIFO队列的总线仲裁器的设计

2015-12-31朱丽蔡瑞

朱丽,蔡瑞

(中航飞机西安飞机分公司,西安 710089)

0 引言

进入纳米加工时代以来,集成电路芯片的特征尺寸越来越小,单位芯片上的晶体管也越来越多,因此在单一集成电路芯片实现复杂的电子系统已成为学者们研究的热门课题之一,集成电路设计也迎来了SOC片上系统(System on Chip)时代。

随着SOC的高速发展,同一芯片上集成的模块越来越多,系统各模块之间的通信总线技术也随之成为SOC的关键问题之一。各类总线技术、通信架构和资源调配已经被广泛研究和试验验证。

总线架构和仲裁调度是解决片上系统资源冲突主要办法,当片上系统上有多个主设备同时发出请求信息时,就会出现对资源的竞争,这时就应该对设备进行合理的调度,避免出现毫无秩序的一拥而上,而造成拥塞或者数据的丢失,因而设计出合理、公平、高效的仲裁机制尤为重要。为此,本文提出了一种基于队列的混合优先级仲裁机制,从而避免了“死锁”和“饥饿”。

1 仲裁机制的基本原理

在系统中,总线可以看成是共享资源,多个主设备对总线的请求可以看成是资源的竞争,仲裁器是管理机构,监视每个主设备发出的请求,根据其设定的仲裁算法而响应相应的主设备,并给出控制信号。所有的仲裁机制都还应满足:每一时刻至多只能有一个主设备访问总线;每次的访问都不能被打断;先请求者先响应,若有多个主设备在同一时刻发出请求时,按优先级的高低依次响应;算法应相对公平,保证每个主设备有同样的概率访问总线。常用的仲裁算法有:固定优先级(FP)和循环优先级(RR)。

固定优先级:各个主设备的优先级是确定的,不会因为其他外在的条件而改变。当多个主设备同时请求总线时,仲裁器可以快速的响应高优先级的设备,以便有效的利用总线,这种算法的优点是使得主要的设备可以及时快速的得到响应。但缺点在于当高优先级的主设备一直占用总线资源的时候,低优先级的主设备得不到响应,而造成高优先级“撑死”和低优先级“饿死”的现象。

循环优先级:各个主设备的优先级随着请求访问的过程在变化,且根据轮转的规律变化,随着主设备访问总线的结束,其优先级变为最低,在其后的主设备优先级就变为最高。这种算法在某种程度上来讲保证了公平性,但是当某个主设备需要对总线进行多次访问请求时,会由于优先级的降低而增加访问延时,降低效率。

基于以上两种算法的特点,在实际中往往将两种算法结合起来,从而构成更灵活的仲裁机制。

2 仲裁算法设计

2.1 设计思想

FIFO队列(Queue)是一种先来先服务的存储器,包括一个存储块和一个能对数据进出通道进行管理的控制器,一是数据进出有序,先进先出;二是输入输出口独立[1]。队列有两个地址指针,一个读指针和一个写指针,读指针用于读出下一个有效单元的数据,写指针用于将数据写入下一个有效单元。在读写操作时,队列会先判断是否空或满。

本文采用的设计思路是先将频繁访问总线的主设备的优先级确定为最高,如果有请求则优先响应,基于循环队列的仲裁算法就是利用了以上队列的特性,当只有一个主设备请求总线时,将仲裁结果进入队列。由于队列先来先服务的特性,可以先申请先得到响应,当有多个主设备请求总线时,先采用仲裁算法进行仲裁,然后根据优先级的高低依次进入队列,最后依次进行响应。在进入和出队列时,每次要先进行判断队列是否空或满,如果空,说明当前队列中没有对总线发出请求的设备,如果满,说明在有对总线发出请求的设备时,已无法入队列,只有当队列中有其他设备出队列后,才能再次进入队列。

这种设计方法的即保证了高优先级主设备的优先性,又保证了其他主设备的公平性,且响应时间短,采用队列的方式不会由于同时访问总线而产生“死锁”和“饥饿”现象。

2.2 仲裁器的组成分析与设计实现

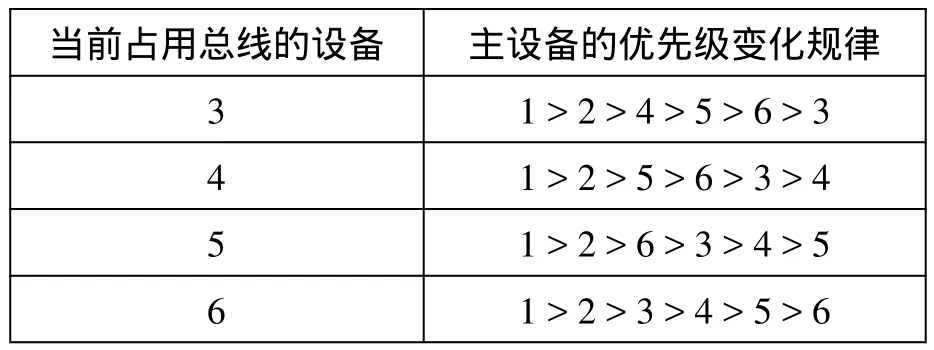

本文设定有6个主设备,且主设备1和2的优先级最高(主设备1的优先级高于主设备2),对于主设备3、4、5和6采用循环优先级的方式进行优先级的判断,优先级的算法如表1所示。

表1 优先级算法

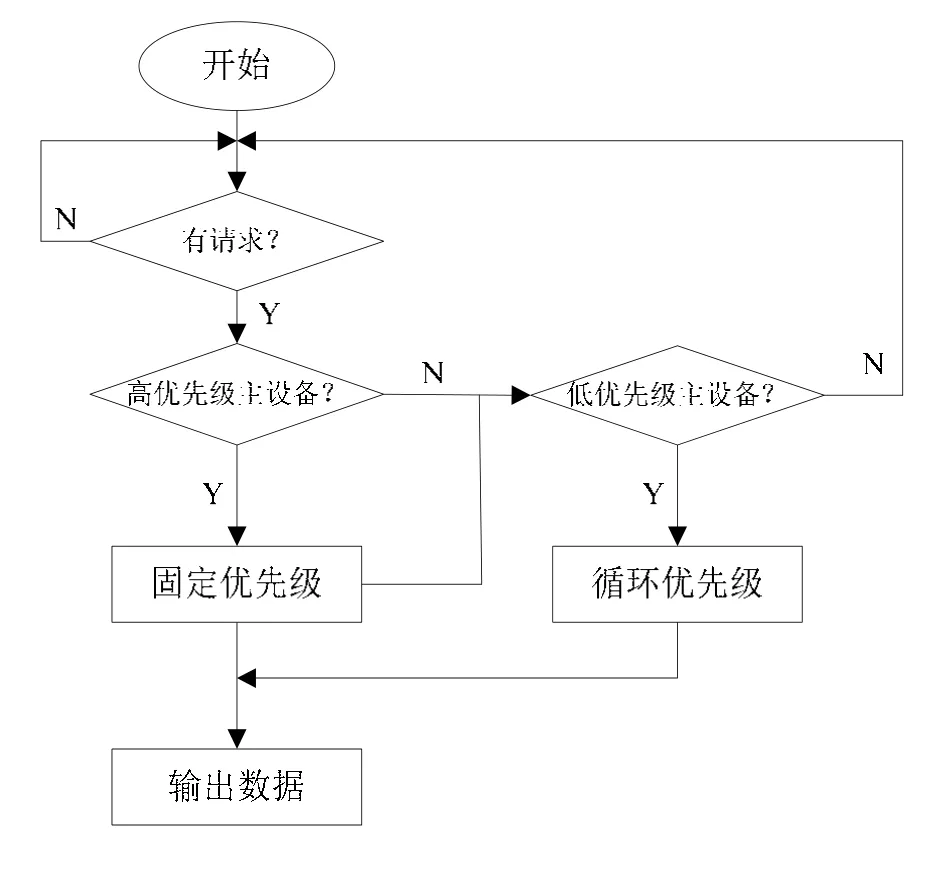

本设计采用自顶向下的设计方法可分为H_round_arb/L_round_arb、H_queue_ram/L_queue_ram(H表示高优先级,L表示低优先级)和grant五个模块,顶层设计原理如图1所示。

图1 总线仲裁器顶层设计原理图

H_round_arb/L__round_arb模块:此模块的功 能是完成对请求总线主设备的仲裁,对同一时刻有多个主设备请求总线时H_round_arb采用固定优先级进行仲裁,L_round_arb采用循环优先级进行仲裁。具体流程如图2所示。

图2 仲裁过程设计原理图

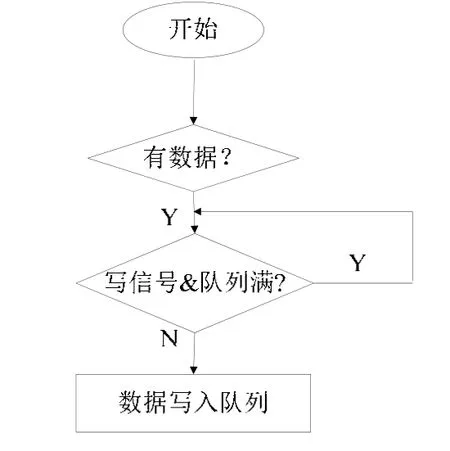

H_queue_ram/L_queue_ram模块:此模块的功能是根据仲裁模块产生的主模块先后顺序依次写入队列中,队列可直接利用FPGA中的FIFO进行实现。具体流程如图3所示。

图3 队列写入原理图

Grant模块:此模块的功能是根据队列中的顺序依次对主设备响应总线。当ctrl=1时,响应高优先级队列,当ctrl=0时响应低优先级队列。具体流程如图4所示。

3 实验验证情况

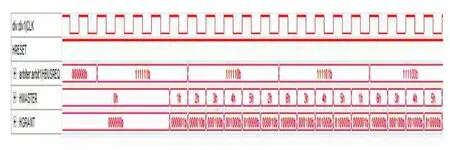

本设计采用Verilog HDL硬件描述语言进行了RTL级的代码描述,在Modelsim6.4a环境下进行了功能仿真验证,并采用Altera CycloneIV E系列芯片,在Altera的QuartusII11.0上进行了设计及布局布线,用SignalTap II Logic Analyzer观察波形,所得设计仿真波形如图5所示。

图4 队列读与响应原理图

图5 仿真波形

当所有的设备向总线发出请求时,总线会优先响应1和2主设备,当高优先级响应完时,接着根据循环优先级的判断来依次响应主设备,如图中的主设备3、4、5、6,当主设备5响应完时由于主设备2发出了请求,因此要优先响应,当响应完主设备2之后,接着响应之前未响应的在队列中的主设备6,然后依次响应主设备3,当主设备3响应完后,此时主设备4的优先级较高,因此当主设备3、4、5、6同时请求时,优先响应主设备4。HGRANT=0和HMASTER=0表示当前总线空闲。仿真结果表明,该设计达到了预期的目标。

4 总结

在基于总线协议的SOC系统中仲裁算法有着广泛的应用,本文提出的算法结合了固定仲裁算法和循环优先级算法的优势,并通过队列存储的方式有效的解决了“死锁”问题,避免了拥塞现象,同时本设计既保证了高优先级的优先响应,又保证了低优先级的公平性,且本算法的响应时间短,设计实现简单可靠。

[1]周先谱,仝晓梅.基于FIFO队列的PCI总线仲裁器的设计与FPGA实现[J].现代电子技术,2007(22).

[2]杨冬勤,黄航,张小燕,于忠臣.多路有序优先级和有序环形仲裁器设计[J].计算机工程,2011,24.

[3]Banerjee,B.LS,Bangalore,India.TREAT THY SECONDARY(ALMOST)LIKE THY PRIMARY-A FAIRARBITERIN MASTER-SLAVECONFIGURATION[J].IEEE Xplore,2013:184-190.

[4]杨哲,张萍,马佩军,李康,史江一,舒保健.基于动态混合优先级算法的仲裁器设计[J].电子器件,2011,34(3).

[5]李耀荣,王光军,梁利平 等.SoC总线仲裁算法的研究[J].微型计算机信息,2007.23(6-2):113-115.

[6]夏宏,王媛,李文娟.基于混合优先权算法的AHB总线仲裁器设计[J].中国电力教育,2008,(S1).

[7]李玲,王祖强.AHB总线仲裁器的设计[J].电子工程师,2005(1).