基于FPGA的多路高速数据传输同步时延测量系统*

2015-12-22逄锦昊熊梓成

逄锦昊,苏 涛,杨 涛,熊梓成

(西安电子科技大学雷达信号处理国家重点实验室,西安710071)

PANGJinhao,SU Tao*,YANGTao,XIONGZicheng

(National Laboratory of Radar Signal Processing,Xidian University,Xi’an 710071,China)

串行数据传输技术具有传输速度快,抗干扰能力强的优点,广泛应用于雷达,航空航天和其他测控领域[1-4]。随着 FPGA 技术的发展,出现一种多路串行数据同步传输方式[2],具有速度高、链路数量少和设计复杂度低的优点。这种方式的关键是测量和调整同步时延,文献[2]借助FPGA的SelectIO资源测量同步时延,要求传输数据已知,量程是FPGA能够实现数据的最大延迟值。在实际应用中,存在传输数据需处理才能得知以及超出量程的问题。为了满足更为复杂的测量需求,本系统采用Xilinx公司的Virtex6系列XC6VLX240T FPGA,通过输入输出延迟单元(IODELAYE)延迟数据和混合模式时钟管理器(MMCM)移相采样时钟,扩大了测量范围,实现多路高速数据传输同步时延的高精度测量。

1 多路串行数据同步传输

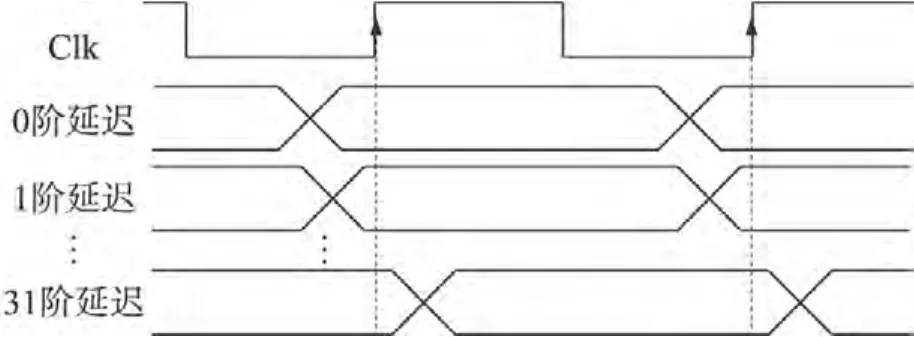

多路串行数据同步传输时序图如图1所示,在数据链路的发送端和接收端使用同源的数据传输时钟Clk,采用一个帧同步信号Frame标志每帧串行数据的起始位,同步传输多路高速数据Data。由于存在PCB走线不等长等多种因素,多路数据的稳定期并不能完全对齐,出现同步时延问题。接收端只有一个采样时钟,同步时延较大时,采样时刻可能是某路数据的不稳定期,造成误采样,使数据传输出错,例如图中的Datan路数据。解决上述问题的关键是在接收端测量和调整数据的同步时延,保证数据正确传输。

图1 多路串行数据同步传输时序图

2 系统方案设计

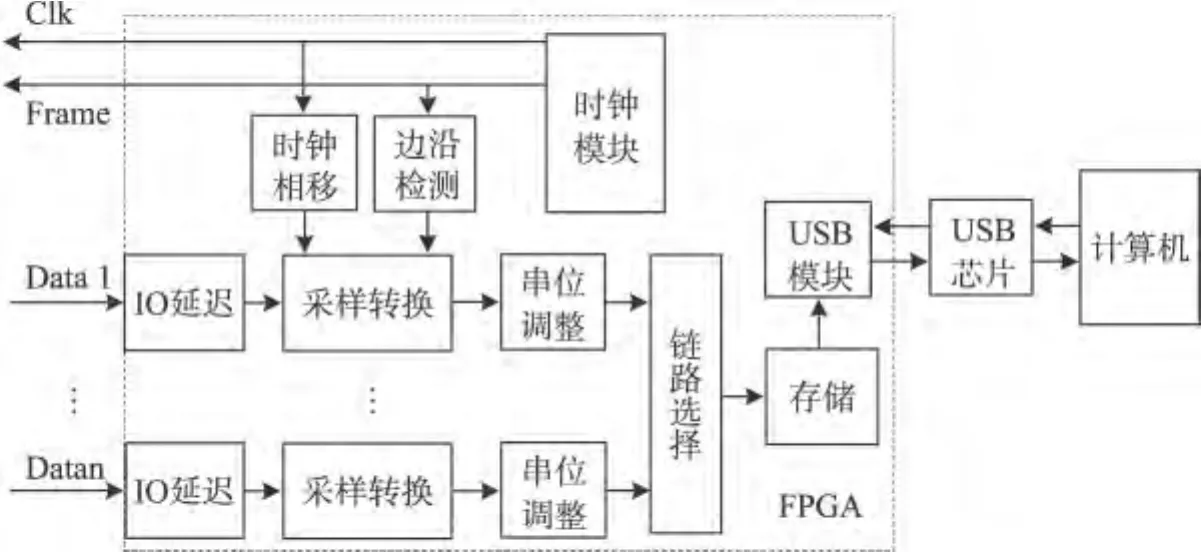

时延测量系统框图如图2所示。系统主要由FPGA、USB芯片和计算机组成。系统工作时,在FPGA中产生数据传输时钟Clk和帧同步信号Frame,对多路串行数据Data进行采样、串并转换和串位调整,将调整串位后的数据存储后通过USB芯片传送到计算机。由计算机处理采样数据,计算和显示同步时延。本文设定的数据传输时钟为133.3 MHz,帧同步信号为 260.4 kHz。

图2 时延测量系统框图

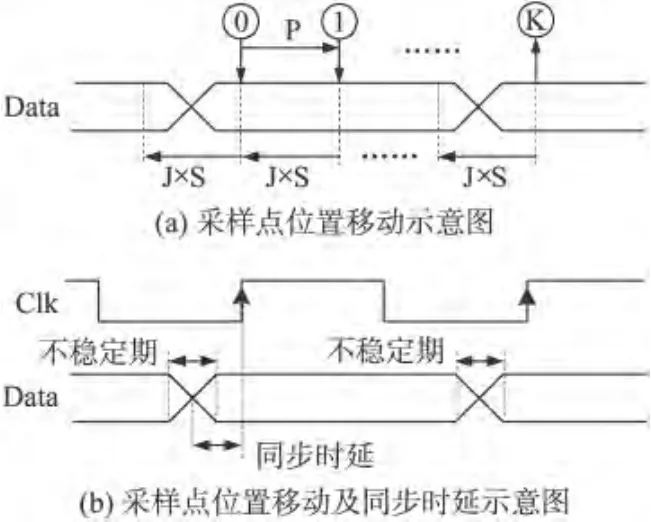

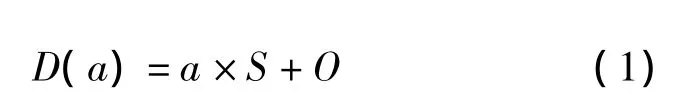

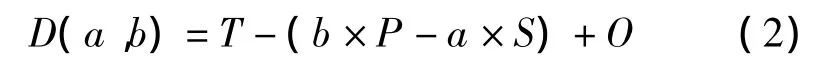

采样点位置移动示意图如图3(a)所示,单路数据的起始采样点在位置0,IO延迟模块通过IODELAYE对串行数据进行延迟实现采样点位置左移,左移的间隔是其一阶延迟值S ns,数目是最大延迟阶J,达到J后,采样点回到位置0。移相模块使用MMCM对数据传输时钟移相P ns,由于存在移相精度误差,P近似且小于JS,采样点到达位置1,依次重复上述采样点位置左移和移相的操作,使采样范围覆盖一个数据传输周期T的间隔,移相的次数K取大于T/P的最小正整数。一个采样点位置可由到达该位置时经过的左移次数a和移相次数b确定,a的取值范围是0~J,b的取值范围是0~K,测量的流程图如4所示,在完成一次采样点位置的移动后,采样转换模块使用移相时钟采样延迟后的数据,得到该采样点位置的数据,采样持续多个时钟周期,采样转换模块对数据解串,调整串位,将调整串位后的数据存储后批量传输到计算机。计算机通过对调整串位后的数据进行分析处理,判断采样点位置的传输是否稳定,记录传输不稳定的采样点位置,传输不稳定的采样点位置在不稳定期,如图3(b)所示,当找到两个不稳定期时,取前一个不稳定期,根据不稳定期中点的左移次数a和相移次数b,计算数据传输时钟上升沿和不稳定期中点的时延,称之为同步时延,当b=0时,计算公式如下:

图3 采样点位置移动与同步时延示意图

图4 单路数据同步时延测量的流程图

其中S是一阶延迟值,O是可编程延迟单元传播延迟。

当b>0时,计算公式如下:

其中T是数据传输周期,S是一阶延迟值,P是时钟相移时间间隔,O是可编程延迟单元传播延迟。重复上述测量单路数据同步时延的操作,完成多路数据同步时延的测量。

3 系统功能实现

3.1 串行数据延迟

XC6VLX240T的可编程引脚都集成了IODELAYE,其内含可变延时线,分32阶,每阶可使串行数据延迟0.078 ns,串行数据延迟示意图如图5所示。延迟控制器(IODELAY_CTRL)用于保证延迟的精度,需为其提供1个200 MHz的参考时钟[5],只需在顶层例化一次,ISE编译器将自动为每个时钟区域添加一个IODELAY_CTRL。

图5 串行数据延迟示意图

串行数据延迟仿真图如图6所示,IODELAYE工作在VAR_LOADABLE模式[5],传播延迟(0阶延迟)是0.144 ns,Value显示设置的延迟阶。图中延迟阶由1递增到2,通过ISim两个光标测量输入数据Data和延迟数据DataDelay之间的1阶延迟是0.222 ns,与理论值相符。

图6 串行数据延迟仿真图

3.2 采样时钟相移

XC6VLX240T具有12个功能强大的MMCM,每个时钟管理器可输出7路不同频率和相位的时钟,同时具有多种分频形式满足不同的时钟需要,系统采用小数分频产生高精度的数据传输时钟,通过2路分频计数器级联产生低频的帧同步信号。现主要讨论MMCM动态移相功能,相位移动按步长计算[6],步长公式为:

Step=1/(56×FClk×M/D) (3)其中FClk为输入参考时钟的频率,M为倍频因子,D为分频因子。本文使用的参考时钟为数据传输时钟,M 为8,D 为1,得到步长 Step 为 0.0167 ns。根据上文计算JS为2.418 ns,由于存在移相精度误差,相移间隔P取近似且小于2.418 ns的值,相移一次需144个步长,相移间隔为2.413 ns。采样时钟相移示意图如图7所示。

图7 采样时钟相移示意图

图8 采样时钟相移仿真图

相移仿真图如图8所示,MMCM增加一个步长所用的时间是13个Clk周期,通过每隔13个Clk时钟周期将PSEN拉高一次,使步长加1,PSDONE信号变高标志操作完成[6]。在完成相移后,通过ISim两个光标测量参考时钟Clk和相移时钟Clk-Shift之间的延迟是2.413 ns,与理论值相符。

3.3 采样转换和串位调整

采样转换和串位调整结构图如图9所示,采样转换模块在检测到帧同步信号的上升沿后,使用ISERDES(串并转换器)完成数据的采样和解串,将数据解串为8 bit并行数据,数据时钟是移相时钟的8分频时钟[5]。为了便于数据处理,从每帧的第1个串行数据开始将8 bit并行数据对齐,当数据没有对齐时,通过串位调整对其进行重组,例如,发送并行8 bit数据 A[7:0],B[7:0],C[7:0],…解串时可能按{A[2:7],B[0:1]},{B[2:7],C[0:1]},…恢复数据,从而产生2个串位[7-9]。如图9所示,为正确恢复数据,使用2个寄存器将串位数据缓存一个数据时钟周期,实现数据的对齐。

图9 采样转换和串位调整结构图

由于USB芯片是批量传输数据[10],在调整完串位后,将一路数据存储到RAM。在接到计算机的上传数据指令后,USB模块将RAM里的数据传输到计算机。

3.4 计算机数据处理

相比于FPGA,计算机软件处理数据更为灵活,计算机软件采用VC和MATLAB混合编程的方法,VC程序作为前端界面,通过调用MATLAB引擎,与后台MATLAB连接,实现动态通信[11]。VC简明的界面显示和快捷的编程设计与MATLAB强大的计算和图形显示功能融为一体,缩短了程序开发周期,提高了编程效率,适用于数据内容复杂和实时性要求不高的场合。

计算机软件接收数据后,根据已定协议,通过VC数据拼接恢复数据,再使用VC调用MATLAB的函数库处理数据。当传输的数据已知时,将每个恢复数据和已知数据进行对比,若出现对比结果不同的情况则在该采样点位置传输不稳定,记录所有传输不稳定的采样点位置。当传输的数据为波形数据时,波形的频率f、信噪比已知,首先对数据进行FFT运算,根据FFT的结果,取频点f及其两旁适当频点对应的幅值,求均方根值作为信号有效值,其余频点对应幅值的均方根值作为噪声的有效值,计算信噪比[12],计算公式如下:

其中Asignal是信号的有效值,Anoise是噪声的有效值。将求得的信噪比和已知的信噪比进行对比,若对比结果相差δ,则在该采样点位置传输不稳定,记录所有传输不稳定的采样点位置,其中δ根据具体的应用环境确定,例如在本文试验测试环境下通过大量试验数据分析确定δ为1 dB。

4 测试与分析

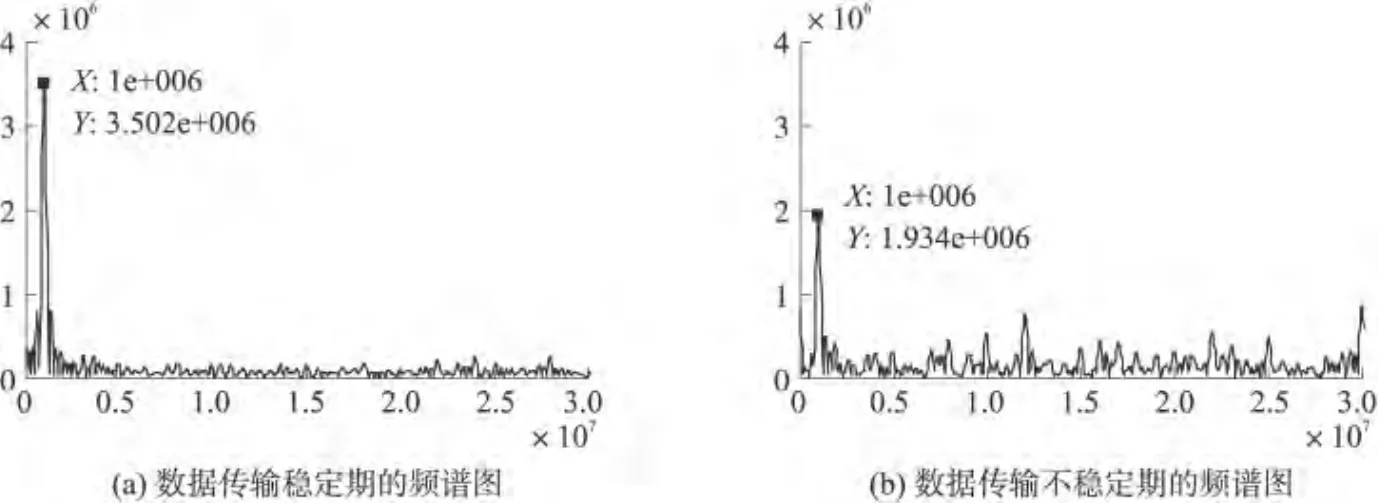

现对一个AD采集系统输出的多路串行数据同步时延进行测量,数据传输时钟为133.3 MHz,帧同步信号为260.4 kHz,每路数据均为正弦波下变频后的数据,频率为1 MHz,信噪比为25 dB,I/Q两路数据位宽均为16 bit。系统对每路数据进行采样,采样时钟经过4次相移,每次相移后数据遍历31阶延迟,共有124个采样点位置,在每个采样点位置采样得到132个I/Q两路数据。计算机对每个采样点位置的数据做FFT,当采样点位置在稳定期时,频谱很明晰,如图10(a)所示,由式(4)计算信噪比均在24 dB以上;当采样点位置在不稳定期时,频谱的噪声很大,如图10(b)所示,信噪比均在21 dB以下。

图10 采样点在不同时期的数据传输的频谱图

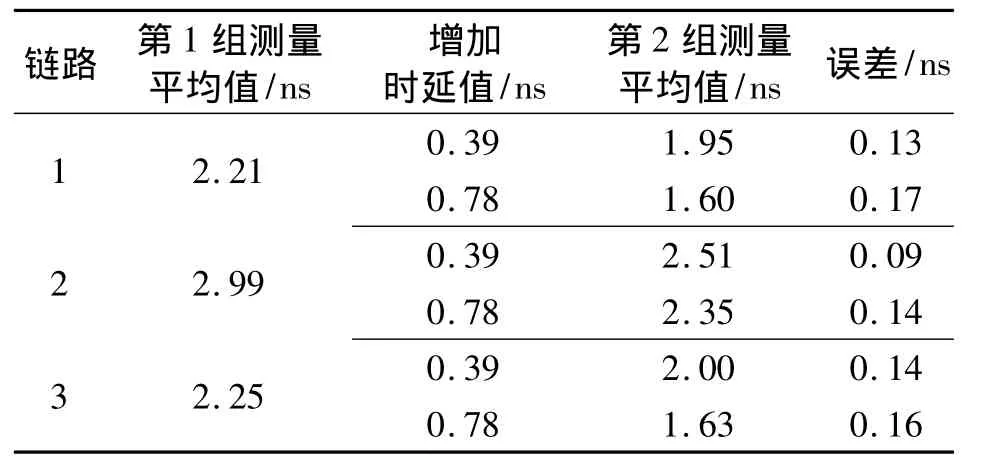

系统通过对一组测量结果求平均值保证测量的精度。为了进一步检验系统测量时延的精度,在完成单路第1组测量后,在该路的发送端利用IODELAYE对输出数据的延迟进行调整,增加数据的时延,通过第2组测量调整后的时延,得到测量的误差,实验结果如表1所示。由实验结果误差分析可知,系统测量的误差小于0.20 ns,能够满足高精度的测量需求。

表1 实验结果表

5 结束语

本文设计了一种多路高速数据传输同步时延测量系统,基于Xilinx公司的Virtex系列FPGA芯片XC6VLX240T进行测试分析。利用IODELAYE模块,系统时延测量分辨率可达0.078 ns,通过和MMCM资源结合,测量范围可覆盖一个数据传输周期的间隔。测试分析中,采用正弦波信号验证本文系统的性能,实测测量误差小于0.2 ns,能够精确实现同步时延的测量。

[1] 张小军,廖风强,王录涛,等.多通道高速串行LVDS信号解串器设计[J].电子测量技术,2013,36(4):63-67.

[2] 武荣伟,苏涛,翁春蕾.基于FPGA的高速数据传输方案设计与实现[J].重庆邮电大学学报(自然科学版),2010,22(2):205-208.

[3] Zhang Huixin,He Qi,Liu Suhua,et al.The Design for LVDSHigh-Speed Data Acquisition and Transmission System Basedon FPGA[C]//Robin Baldwin,Jennifer Stout,eds.Communication Software and Networks(ICCSN).Piscataway:IEEE,2011:383 -386.

[4] 何航峰,郑步生.一种DSP高可靠快速数据传输方法的研究[J].电子器件,2014,37(1):157-161.

[5] XILINX.Virtex-6 FPGA SelectIO Resources[J/OL].http://www.xilinx.com/products/virtex6,2010 -8 -16/2014 -4 -20.

[6] XILINX.Virtex-6 FPGA Clocking Resources[J/OL].http://www.xilinx.com/products/virtex6,2011 -1 -17/2014 -4 -20.

[7] 徐文波,田耘.Xilinx FPGA开发实用教程[M].2版.北京:清华大学出版社,2012:219-240.

[8] 隆志远,陈仁文,朱莉娅.一种基于FPGA的旋转机械非接触双向红外信号传输系统的实现[J].传感技术学报,2011,24(4):559-563.

[9] Wang Hai,Zhou Wei,Li Zhiqi,et al.A Time and Frequency Measurement Method Based Ondelay-Chain Technique[C]//Aaron Partridge,eds.Frequency Control Symposium.Piscataway:IEEE,2008:484 -486.

[10]赵林,孟令君,于磊,等.基于CY7C68013A的USB2.0高速接口设计[J].电子技术应用,2014,40(1):131-133.

[11]穆以东,赵岭.VC++与MATLAB混合编程方法研究[J].测控技术,2013,32(9):111 -116.

[12]李玉峰,韩晓红,刘洋,等.基于FPGA的高速数据采集系统的实现与性能分析[J].电子器件,2012,35(6):709-712.