改进的可配置RO PUF及其实现

2015-12-20王建业

丁 浩,王建业

(空军工程大学 防空反导学院,陕西 西安710051)

0 引 言

基于环形振荡器的物理不可克隆功能 (ring-oscillatorbased physical unclonable function,RO PUF)[1-3],是 安 全领域一项新兴的技术。它利用硅芯片在制造过程中产生的物理性质上的差异,生成每块芯片独一无二的 “ID”。该ID随芯片的不同而变化,可在线产生,无需存储,可以很好地应用于设备认证、数据流加密[4]。

RO PUF的缺点在于每个RO 的结构都是固定的,“只能产生一个ID”,即使增加RO 的数目也只能增加ID 的位数,而不能增加ID 的个数。实际应用中,为保证安全性与可靠性,往往需要众多的ID,从中筛选出一个或数个最合适的。对于此,Maiti对RO PUF的结构及原理进行了详细阐释,提出了 “可配置RO PUF”[5],在不增加占用LAB资源的情况下,提高了产生的ID 个数,但其产生的ID 数量仍不能满足要求。为此,文中对Maiti的 “可配置RO PUF”进行了改进,在保证ID 位数的同时,大大增加了可生成的ID 数量,并使得ID 具有更高的 “片内稳定性”和“片间差异性”。

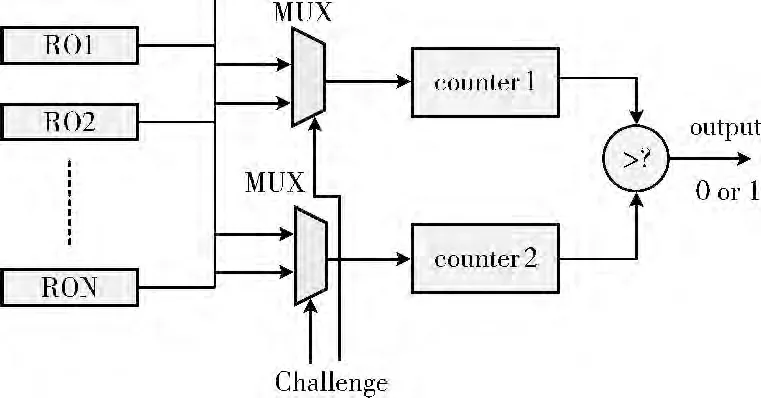

1 RO PUF原理

RO PUF是PUF[6,7]中应用较为广泛的一种,其基本结构单元是环形振荡器 (ring-oscillator,RO)。RO 的构成如图1所示。

图1 RO 的基本构成

图2 RO PUF原理

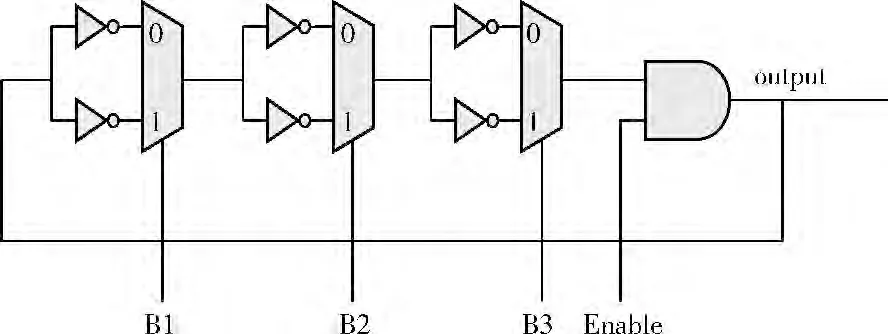

Maiti在RO PUF的基础上设计出了 “可配置的RO PUF”[5],其结构如图3所示。

图3 Maiti可配置的RO

Maiti的可配置RO PUF 可以产生8 种不同的结构形式,改变输入信号 “B1、B2、B3”,可以选择其中任意一种结构。每一种结构都有特定的振荡频率。在两个RO 进行频率比较时,必须使它们的 “B1、B2、B3”保持相同,如此才能保证频率的差别来自制造误差,而不是RO 的结构,也不是布局布线的差异。

除RO PUF 外,另一种广泛研究的PUF 是Arbiter PUF[8]。与 之 相 比,RO PUF 具 有 更 大 的 优 势。Arbiter PUF要求布局布线和器件放置必须达到严格的对称,否则制造误差引起的延时将被布局布线的不对称所抵消。而RO PUF只要求每个RO 是相同的,不要求整体的布线是对称的。更重要的是,完全的相同的RO 布线可以通过Altera Quartus II的 “Logic Lock”功能来轻松实现。

在使用 “Logic Lock”时,Maiti的 “可配置RO PUF”与基本的RO PUF一样都占用了一个LAB,没有增加LAB资源的消耗。而Maiti的 “可配置RO PUF”一对儿RO 可以分别在8 种结构下产生输出,增加了输出个数。文献[5]还研究出该RO PUF具有更好的稳定性。

然而,在实际应用中,Maiti“可配置RO PUF”产生的ID 数量还不足以满足使用要求,为提高安全性,必须增加ID 个数。为此本文做出了改进,设计了新型的可配置RO PUF,以增加产生的ID 数量。

2 改进的可配置RO PUF

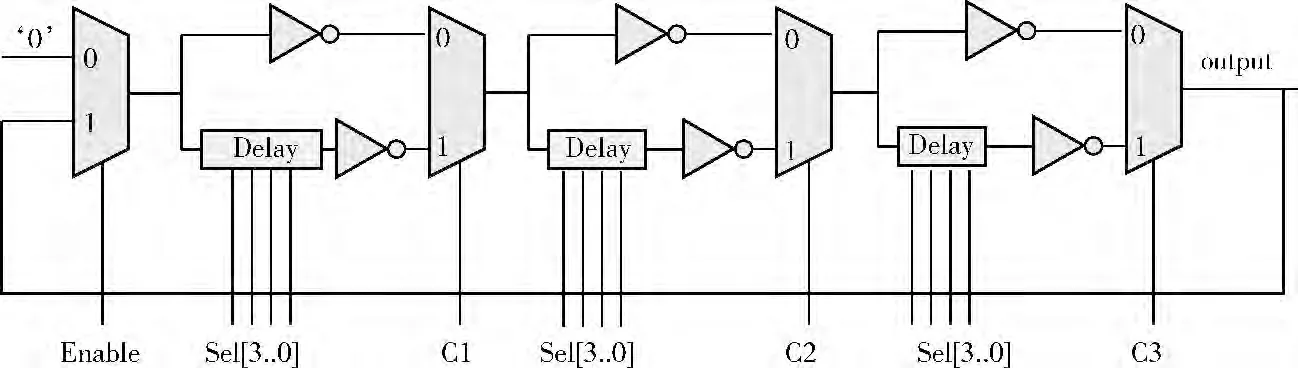

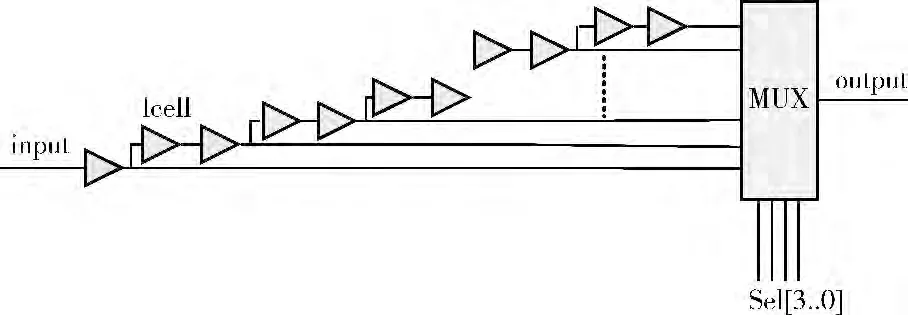

改进的可配置RO PUF可以产生128种不同的结构形式,单个RO 的结构如图4所示。

图4 改进的可配置RO

改变输入信号Sel[3..0]和C1、C2、C3可以选择其中任意一种结构形式。图4 中 “Delay”是可调延时单元,可以通过Sel[3..0]选择不同的延时,其结构如图5 所示。与Maiti的 “可配置RO PUF”相比,可调延时单元Delay的加入,显著增加了可以产生的结构形式,也就增加了可以产生的ID 个数。同时,Delay的结构比较灵活,可以根据需要增加或减少其内部的延时单元数。更重要的是,在使用 “Logic Lock”时,改进的可配置RO PUF 共占用了9个LAB,是Maiti“可配置RO PUF”的9倍,但产生的ID 数量为128个,是Maiti“可配置RO PUF”的16倍,显著提高了LAB的利用率。

一站式的检查预约首先需要完善的软件支持。信息科牵头完成“检查预约平台”的开发设计,让医技资源与检查需求互联互通,从而实现了以患者为中心的检查预约服务和一个平台的多检查预约管理。

图5 可调延时单元Delay结构

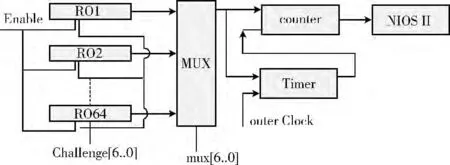

在实验中,共设计了64 个改进的RO (RO1、RO2、RO3……),结构如图6所示。

图6 改进的可配置RO PUF原理

激励信号Challenge[6..0]决定着RO 的结构,它由图4中的Sel[3..0]和C1、C2、C3组成。Sel[3..0]对应Challenge[3..0],C1、C2、C3对应Challenge[6..4]。所有RO Challenge[6..0]的对应位都连接到一起,保证每个RO 的布线完全相同,保证其频率差异只与制造误差有关。选择信号mux [6..0]用来选择一个RO 进行计数。定时器 “Timer”与计数器 “counter”同时开始工作,控制计数器的工作时间,此段时间内的计数值交给NIOS II进行处理。NIOS II对计数器得到的计数值进行采集、存储,并经串口发送给上位机。待处理完毕后,选择下一个RO进行计数。

同样的,为免除数据关联性的影响,上位机在进行频率比较时,只比较相邻RO 的频率,如此可以得到128 个63位的 “ID”,数目远远大于Maiti的8 个 “ID”。通过后文的实验,还证明了改进的可配置RO PUF拥有其它更优的性能。

3 实验结果与分析

文 中 的 实 验 是 在 Altera 公 司 Cyclone IV 系 列EP4CE6F17C8的FPGA 上实现的,开发软件为Quartus II,编程语言VHDL。取外部时钟 “outer Clock”为100MHz。

3.1 RO 激励信号对振荡频率的影响

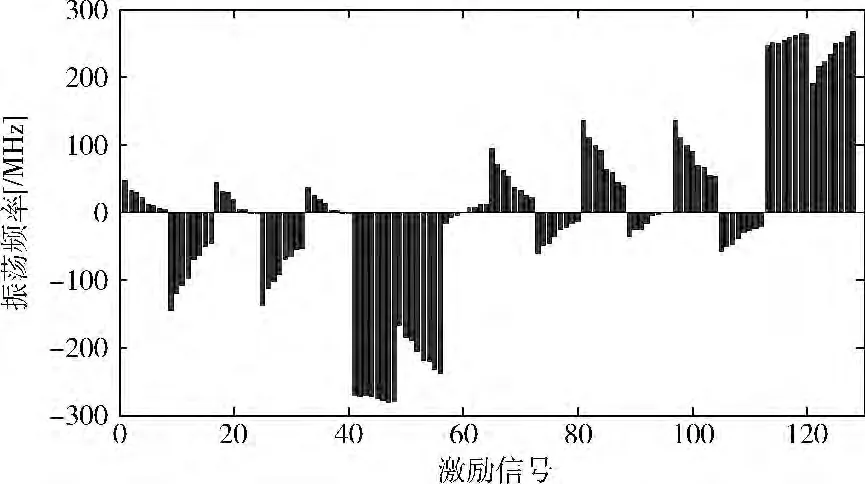

在进行ID 提取之前需要验证所改进的RO 的结构是否有效,即当改变激励信号Challenge [6..0]时,RO 的振荡频率是否会发生变化,以及相邻两个RO 之间的频率是否会有差别。选取图6中相邻的RO1、RO2研究RO 激励信号对振荡频率的影响。

图7显示了RO1、RO2 的频率差,若频率差大于0,表示RO1的频率高于RO2;反之,则低于RO2两个RO 进行频率比较时,它们的激励Challenge[6..0]中对应位应连接在一起,保证它们的结构时刻保持相同。图7可以发现,在这种情况下,RO1 与RO2 之间仍然存在着频率差异。并且,RO1与RO2的频率差会随着Challenge[6..0]的变化而改变。说明引入的 “可调延时单元”并没有抵消制造差异的影响,在同一芯片内不同位置摆放的两个RO,会以不同的频率进行振荡。并且引入的 “可调延时单元”并没有对RO1 和RO2 的频率差产生倾向性的影响,即RO1与RO2的频率差并不为常值,且不恒为正或恒为负,说明产生的ID 仍然具有随机性,无法从输入激励预测产生的ID,提高了ID 的安全性。

图7 RO1与RO2的频率差

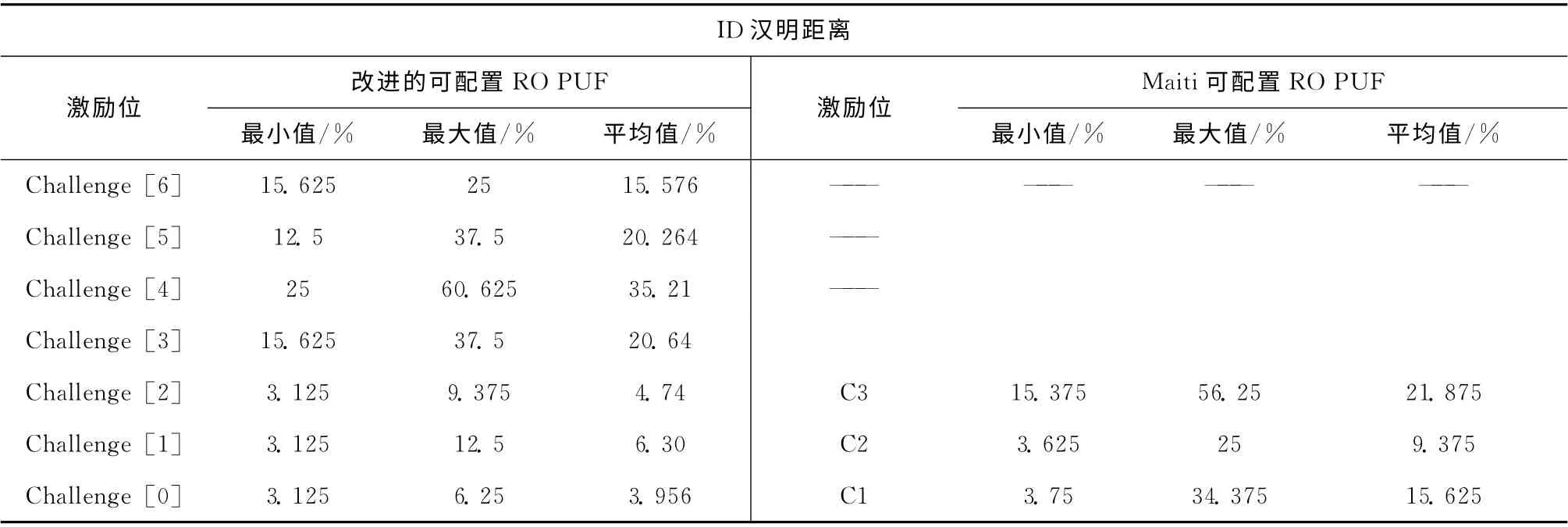

其次,研究激励信号Challenge [6..0]中Sel[3..0]和C1、C2、C3单个位的改变对 “ID”的影响。这里利用该位改变前后ID 的汉明距离与ID 位数的比值来表示改变的程度。

当激励信号中的某一位改变时,计算该位改变前后对应的 “ID”汉明距离与ID 位数的比值的变化情况。汉明距离指两个等长的字符串中对应位置的字符不同的个数。汉明距离与字符串长度的比值可用来表征两个字符串不相同的程度。

表1给出了只改变一位激励信号时, “改进的可配置RO PUF”与Maiti“可配置RO PUF”输出ID 汉明距离的变化情况。分别计算了它们在单个位改变前后对应 “ID”的汉明距离与ID 位数比值的最小值、最大值以及平均值。其中平均值能较好的反应该位对ID 的影响程度。值越大,说明这一位改变时ID 的影响越大,这一位起到的作用越显著。从表1中可以发现Challenge[4]~Challenge[6]引起的ID 变化要大于Challenge[0]~Challenge[3],这是因为Challenge[4]~Challenge[6]位对应C1~C3,它们的改变会决定RO 中存不存在 “可调延时单元”,也就决定了RO 中包不包含 “可调延时单元”中的缓冲器Lcell。Lcell是人为添加的缓冲单元,数目越多,对制造差异的抵消越大,产生的ID 越趋向于相同。而Challenge [0]~Challenge[3]对应调延时单元的sel[3]~sel[0],控制的可调延时单元内部的延时,受制造差异的影响较小。同时,对比 “改进的可配置RO PUF”与Maiti“可配置RO PUF”,可以看出,在改进的可配置RO PUF中,激励信号Challenge[6..0]的改变,尤其是Challenge [6]~Challenge[4]对ID 产生的影响要大于Maiti的可配置RO PUF,也就是说,改进的可配置RO PUF产生的ID 独立性更高,安全性更高,也就越难以从一个ID 推测出另一个ID,越符合设备认证等对ID 的使用要求。

表1 单个激励位改变时ID 汉明距离的改变量

3.2 片内稳定性与片间差异性

片内稳定性与片间差异性是衡量RO PUF的重要指标。

设备认证与数据流加密等场合要求同一芯片的ID 产生后必须保持不变,并且能重复生成。这就要求RO PUF 必须要能适应环境的改变,尤其是在供电电压与环境温度变化时,保证产生的ID 稳定不变。片内稳定性就是用来衡量ID 稳定性的指标。

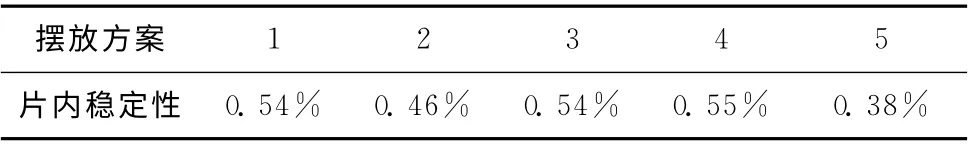

片内稳定性是指同一芯片内摆放于同一位置的同一结构的RO 在不同电压、温度等工作条件下,重复运行多次,计算ID 的汉明距离,距离越小,代表响应之间的差别越小,RO PUF的工作越稳定;由于实验条件的限制,本文只研究了温度对片内稳定性的影响,在20℃~70℃的环境中进行了稳定性实验。每隔10℃,运行每种结构RO PUF 50次,计算ID 的改变程度,仍以汉明距离与ID 总位数的比值来表示,见表2。

表2 片内稳定性

提取的ID 在具有稳定性的同时,还必须具有 “设备唯一性”,即不同的芯片必须具有不同的ID。而且ID 之间必须有足够的差异,以保证ID 能唯一的标识FPGA 芯片,保证不能从一块芯片的ID 推测出另一块的ID,确保安全。片间差异性就是用来衡量不同芯片ID 的差异程度的指标。

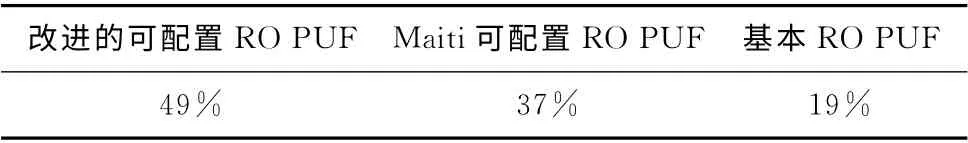

片间差异性是指相同结构的RO 放置在不同芯片的相同位置,计算ID 的改变程度,仍以汉明距离与ID 位数的比值来表示。比值越大,代表ID 之间的差别越大,ID 安全性越高,越能区分开不同的芯片。本文在10 块EP4CE6F17C8的FPGA 上进行了实验。表3给出了改进的RO PUF与Maiti的 “可配置RO PUF”,以及最基本的RO PUF各自ID 汉明距离的变化。

表3 片间差异性

从表2和表3中可以发现,在实验设定的温度范围内,本文改进的RO PUF与Maiti的 “可配置RO PUF”,以及最基本的RO PUF 均具有较好的片内稳定性。而改进的RO PUF具有最高的片间差异性,可以更有效地进行芯片认证,区分开不同的芯片。

3.3 内部摆放位置对ID的影响

同一芯片内部也存在着制造误差,因此RO 在芯片内的摆放位置也会对最终的ID 产生影响。通过改变 “LOGIC LOCK”的锁定区域,改变RO 在片内的位置,比较其片内稳定性的变化。共设计了5 种RO 在片内的摆放方案,计算每种情况下产生的ID 的汉明距离与ID 位数的比值,结果见表4。实验在40℃环境中进行。

表4 不同摆放方案下的片内稳定性

表中结果反映了芯片内部制造工艺的均匀性,由于制造不均匀,不同的位置会产生不同的ID。因此,在使用RO PUF时,需要控制其在芯片内部的摆放,寻找最合适的摆放位置,以使响应的片内稳定性与片间差异性均达到较高水平,满足使用要求。

4 结束语

本文对Maiti的可配置RO PUF 做出了改进,使其可以产生更多的ID,以提高安全性。而且通过实验验证本文改进后的可配置RO PUF 拥有更高的 “片内稳定性”和“片间差异性”。最后讨论了温度、片内位置等因素对ID的影响。

文中得到的ID 还需要经过去噪声等操作才能用作密钥[9-11]。“纠错编码 (ECC)”[12]和模糊提取是目前解决噪声问题比较有效的方法。但大多数的EEC 和模糊提取都是在产生ID 之后进行复杂的数据处理,再将得到的结果送入加密算法,占用了较多片内空间。如果在设计PUF 的时候,就处理这个问题,将节省大量资源。这是未来研究的重点内容。

同时,环境温度、供电电压是影响片内稳定性的重要因素。研究片内稳定性随着温度、电压的变化情况,并保证ID 的准确重复生成也是未来研究的重点内容。

[1]Zhang JL,Qu G,Lv YQ,et al.A survey on silicon PUFs and recent advances in ring oscillator PUFs [J].Journal of Computer Science and Technology,2014,29 (4):664-678.

[2]Muslim M,Mohammed N,Mansoor A,et al.Frequency uniqueness in ring oscillator physical unclonable functions on FPGAs[C]//IEEE 56th International Midwest Symposium on Circuits and Systems,2013:465-468.

[3]Fruhashi K,Shiozaki M,Fukushima A,et al.The arbiter-PUF with high uniqueness utilizing novel arbiter circuit with delay-time measurement[C]//IEEE International Symposium of Circuits and Systems,2011:2325-2328.

[4]Maes R,Herrewege VA,Verbauwhede I.PUFKY:A fully functional PUF-based cryptographic key generator[G].LNCS 7428:Cryptographic Hardware and Embedded Systems,2012:302-319.

[5]Maiti A,Schaumont P.Improved ring oscillator PUF:An FPGA-friendly secure primitive [J].Journal of Cryptology,2011,24 (2):375-397.

[6]Merli D,Sigl G,Eckert C.Identities for embedded systems enabled by physical unclonable functions [G].LNCS 8260:Number Theory and Cryptography,2013:125-138.

[7]Nithyanand R,Solis J.A theoretical analysis:Physical unclonable functions and the software protection problem [C]//IEEE Symposium on Security and Privacy Workshops,2012:1-11.

[8]Hu B,Satoshi G,Yukiyasu T.A multiple bits output ring-oscillator physical unclonable function [C]//IEEE International Symposium on Intelligent Signal Processing and Communication Systems,2011:1-5.

[9]Maiti A,Schaumont P.Improved ring oscillator PUF:An FPGA-friendly secure primitive [J].Journal of Cryptology,2011,24 (2):375-397.

[10]Yu M,Devadas S.Secure and robust error correction for physical unclonable functions [J].IEEE Design & Test of Computers,2010,27 (1):48-64.

[11]Merli D,Schuster D,Stumpf F,et al.Side-channel analysis of PUFs and fizzy extractors [G].LNCS 6740:Trust and Trustworthy Computing,2011:33-47.

[12]Yin C,Qu G.Improving PUF security with regression-based distiller[C]//50th ACM/EDAC/IEEE Design Automation Conference,2013:1-6.