一种高性能数字输出端口电路设计*

2015-12-19陈迪平陈思园曾健平

陈迪平,陈思园,曾健平

(湖南大学 物理与微电子科学学院,湖南 长沙 410082)

在多电源域系统中,数字输出端口主要实现低电源域到高电源域逻辑之间的电平转换以及提供输出驱动能力等功能.数字输出端口的速度、功耗与噪声性能是高速、低电压、低功耗系统设计的重要环节[1].本文提出了一种高性能数字输出端口的设计方案,通过改进传统低转高电平转换单元,解决了传统结构上升沿与下降沿不对称的问题,降低了电平转换单元的延时功耗积,改善了输出端口的传输性能;同时,增加了抗地弹效应电路,降低了端口的同步开关噪声(SSN),提高了端口输出信号的传输质量.

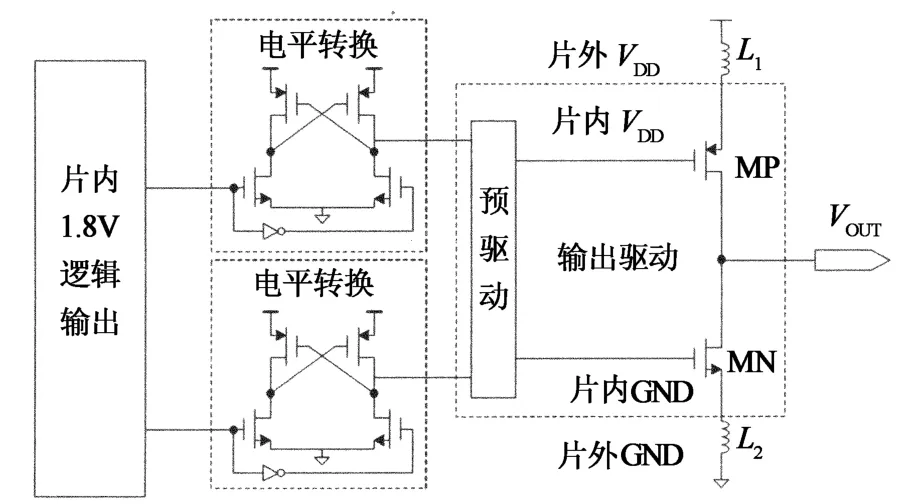

1 数字输出端口结构及原理分析

传统多电源系统数字输出端口结构如图1 所示,主要包括电平转换和输出驱动2 个部分[1].其中,数字输出端口用于实现系统内部的1.8V 逻辑信号到端口3.3V 信号的切换;输出驱动实现对信号的输出.图1中传统低转高电平转换单元为了解决上拉、下拉竞争的问题,需设计NMOS管的尺寸为PMOS管的4倍左右[2],从而使输出存在上升沿与下降沿的严重不对称.因此,传统的电平转换电路结构存在较大的延时功耗积.使电平转换的上升沿与下降沿对称能有效降低电平转换电路的延时功耗积,提升端口的传输性能[3].

图1 传统多电源域数字输出端口结构Fig.1 Conventional multiply powers digital output I/O architecture

图1中传统输出驱动结构在输出状态发生翻转时有较大的瞬态电流流过电源与地线的寄生电感L1和L2,引起地弹效应[4].地弹效应所产生的地弹噪声电压可简单表示为:

如果芯片上有N个同时向低电平翻转的输出,此时流过地线寄生电感的电流将变为N倍[5-6],此时产生的地弹噪声电压可表示为:

式中:NVg为地线上的电压噪声,即同步开关噪声(SSN).同理可知电源线上也将产生同等的SSN 噪声.当这个电压波动的值足够大时,就会影响信号的完整性导致寄存器和逻辑电路的误触发,恶化时钟性能(时钟脉冲漏失或增插)等.降低单个端口的地弹噪声电压Vg能有效降低SSN 噪声电压NVg,抑制端口对系统电源及地的干扰,同时提高输出信号的质量.随着电路规模的增大,工作频率的增加,如何有效降低高速开关电路的SSN 噪声已成为提升系统性能的关键[7].

2 新型数字输出端口设计

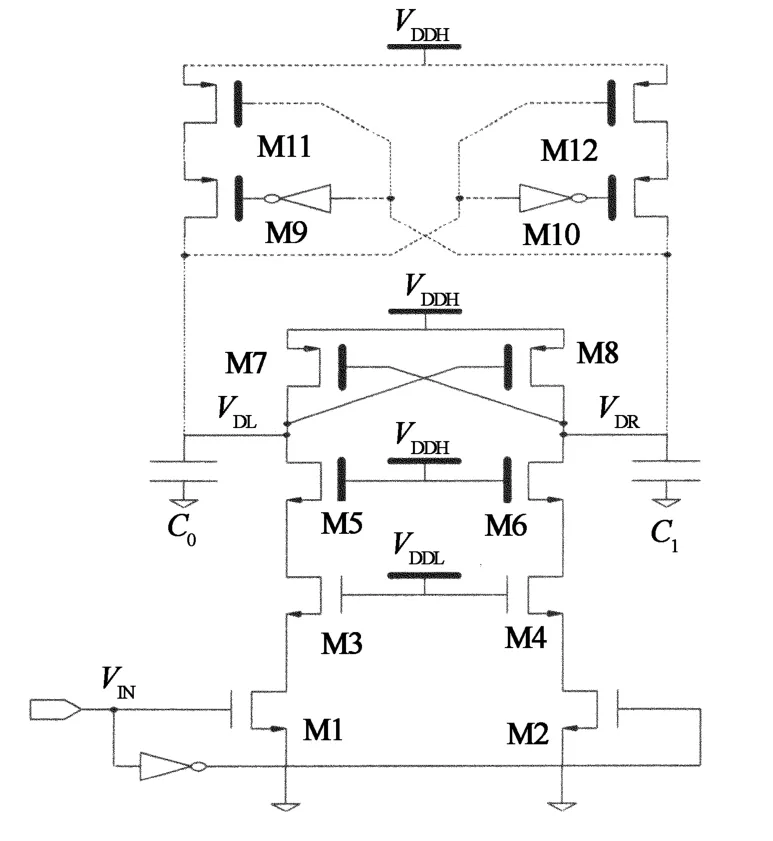

2.1 新型快速低转高电平转换单元设计

新型快速低转高电平转换单元电路如图2 所示.其中实线部分为传统电平转换电路,M1和M2为低阈值NMOS,M3-M6构成保护M1与M2的耐压单元,M7和M8为高阈值PMOS.本文增加了加速上拉单元如图2 中虚线部分,其中,M11/M12管在VDL/VDR下拉时关闭,不与M1/M2 管构成竞争;而在VDL/VDR上拉时开启,提升电路的上拉能力,从而达到在增强上拉的同时,不用同时增强下拉来对抗上拉竞争的目的,降低了提升转换速度所需的功耗,有效降低了功耗延时积.

图2 快速低转高电平转换电路原理图Fig.2 Quick voltage levels transform circuit

在smic18mmrf工艺中,高阈值PMOS管与低阈值NMOS管,VDDL为1.8V,VDDH为3.3V,Vtn为480mV,Vtp为-630 mV,依据文献[3],可得M1/M2管(下拉NMOS)的尺寸约为M7/M8管(上拉PMOS)尺寸的6.5倍.在这个条件下,M1/M2管的最大下拉电流ID1max与M7/M8 的最大上拉电流ID7max满足关系式:

将式(3)代入smic18mmrf下数据参数可得ID1max约为ID7max的10倍,此时需增加上拉管尺寸W7/L7至之前的10倍才能使上拉与下拉的能力相当,因此,设计M11/M12管尺寸为M7/M8管9倍即可使上拉能力与下拉能力相当.

2.2 新型抗地弹效应输出驱动电路设计

由公式(1)可知,在同等寄生电感的条件下,地弹噪声主要取决于输出驱动管的电流变化率,即

因此,降低SSN 噪声可以通过降低电路的电流变化率来实现.本文提出如图3所示的抗地弹效应输出电路结构,该电路主要包括控制逻辑和输出驱动2部分.其中,MP1管和MN1管为输出驱动管,MP2管和MN2管为输出续流管,驱动管的尺寸远大于续流管.该结构利用PMOS控制逻辑模块和NMOS控制逻辑模块对输出电压采样,实现对输出管的切换.其具体工作原理为:当输出电路输出信号由高电平向低电平转换时,连接预驱动上、下节点(A,D)的电压由高电平转向低电平,此时MP1管和MP2管关断.同时节点(D)的信号通过反相器以及传输门传输到MN1管的栅极,MN1 开启,输出电路输出电压开始下降;通过对输出信号采样,关断传输门,即关断大尺寸管MN1,同时开启小尺寸管MN2.在这个过程中,大尺寸管MN1 上出现一个大的负电流变化率,小尺寸管MN2 上出现一个小正电流变化率,有效的降低了整体的电流变化率.同时本结构采用大尺寸管MN1 提供大的泄放电流,采用小尺寸管MN2续流,满足了电路对于延时的要求.

图3 新型抗地弹效应输出电路具体电路图Fig.3 New resistance of ground bounce output circuit

3 仿真与测试

以频率为150 MHz,上升时间与下降时间均为100ps的信号为输入,以20fF电容为负载,得到传统型结构与新型结构电平转换电路的低转高传输延时对比仿真结果,如图4(a)所示.从图4(a)可知,传统型结构传输延时为0.38ns,新型结构传输延时为0.24ns,改良后的结构对转换信号的爬升有明显的加速作用.

图4 电平转换单元模拟仿真结果Fig.4 Simulation results of levels transform

传统型与新型电平转换电路驱动为20~200fF电容负载延时功耗积仿真结果如图4(b)所示.在负载为120fF时,传统型与新型电平转换电路的延时功耗积分别为0.425与0.377ns·mW,新型结构相较传统结构延时功耗积减小了11.3%.仿真测试总共取20~200fF 中等间距的10个点,结果显示新型结构功耗延时积相较传统结构减小5%~15%.负载为20fF减小最多为15%,随着负载电容的增加延时功耗积减小的比例减小.原因在于随着负载电容的变大,电压爬升的时间越长,而由M9/M10管构成的开关延时是一定的,便会造成负载越大改良越小的情况.因此,根据负载的情况选择合适的开关延时是该电路设计的一大关键.

图4(c)所示为传统型与新型电平转换电路在延时为500ps条件下的功耗仿真结果.由图4(c)可知,在相同延时情况下,新型结构较传统型结构消耗更小的功耗.

在电路面积方面,传统型电平转换电路为187.11μm2,新型电平转换电路为223.91μm2.新型电平转换电路面积与传统型转换电路相当,新型结构并未过多增加额外的面积消耗.

在smic18mmrf工艺下,以频率为150 MHz,上升时间与下降时间均为100ps的信号为输入,模拟寄生电感为3nH 的情况下,通过Spectre仿真工具得到信号输出质量与SSN 噪声的仿真结果如图5所示.图5(a)和图5(b)分别为4个传统输出端口同时翻转时,SSN 噪声在信号输出端与地线上的瞬态响应,其幅度大小可达到1.5V 左右,严重影响了输出信号的质量,给地线带入了严重的噪声干扰.图5(c)为新型与传统型结构在同时翻转个数分别为0,2,4,6,8,10时的最大SSN 噪声结果对比.相较于传统型结构,新型结构的SSN 噪声减小30%以上.其中,当同时翻转个数为4个时,新型结构的最大SSN 噪声为0.819 V,相较传统型减少了44.7%.

图5 抗地弹效应输出电路仿真结果Fig.5 Resistance of round bounce simulation result

在不同测试条件下,不同架构的结果不具备可比性.采用参考文献所提出的电路结构,在本文所给出的相同测试条件下,利用smic18mmrf工艺进行功耗延时积和SSN 的模拟仿真,得到其仿真结果如表1所示.

表1 参考文献与本文设计方法性能对比Tab.1 Performance comparison

由表1可知,文献[8]所提出的结构在功耗延时综合性能上最优,但其结构中包含电容,其面积高达885.53μm2,因此,本文所采用结构在较小面积的应用中优势更大.综上所述,本文所设计端口电路无论从功耗延时积还是从SSN 方面都具备很大的优势.

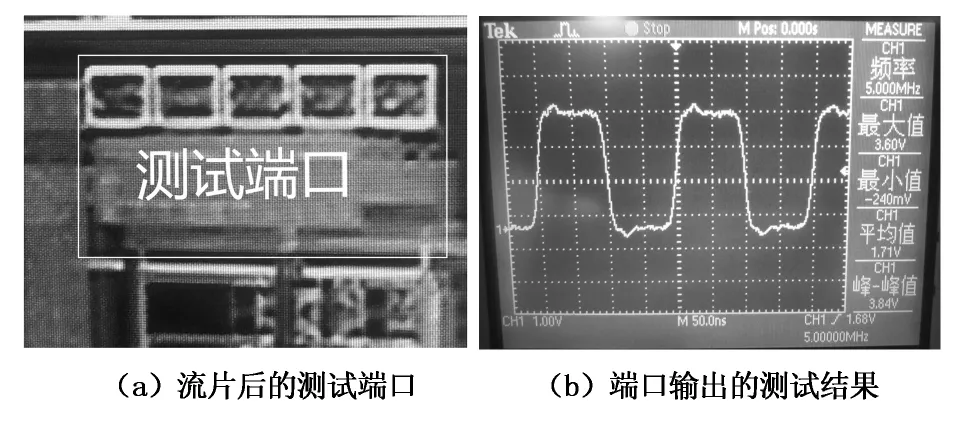

将本文所设计电路应用于输出端口,在smic18mmrf工艺下流片得到的芯片顶层照片及4个端口同时翻转时的信号输出结果如图6所示.

图6 流片结果照片及测试结果Fig.6 Photo of the layout and test result

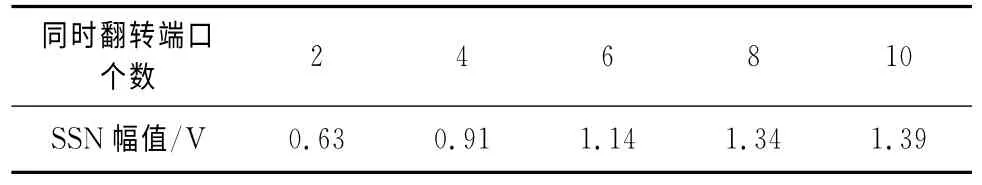

由图6(b)可知,本文设计电路信号输出端没有表现出明显的SSN 噪声干扰.当外接3nH 接地电感,测试端口在2~10个同时翻转时,接地电感上反应出的SSN 噪声幅度如表2所示.与图5(c)仿真结果相比,当翻转个数分别为2,4,6个时所得的测试结果与仿真结果相近,随着翻转个数的增加,测试结果与仿真结果的偏差增大,这是由于测试电路中连线的寄生电感增大了等效接地电感,随着翻转个数增大,寄生电感的影响增大,但相较图5(c)中传统型的仿真结果,测试结果仍存在较大的改进.

表2 端口SSN 噪声幅值测试结果Tab.2 SSN amplitude testing results

4 结 论

本文通过对电平转换单元与地弹效应的原理分析,通过并联加速上拉电路与采样负反馈的方法,提出了一种快速电平转换与低SSN 噪声的端口电路.该输出电路在保持原有下拉延时的情况下,有效地抑制了地弹效应并降低了电路的功耗.仿真结果表明,所设计电平转换单元功耗延时积较传统结构减小5%~15%,SSN 噪声幅度减少30%以上,有效降低了端口的延时功耗积与SSN 噪声幅度.

[1]DABRAL S,MALONEY T.Basic ESD and I/O design[M].New York,USA:A Wiley-Interscience Publication,1998:121-126.

[2]GARCIA J C,MONTIEL-NELSON J A,NOOSHABADI S.High performance CMOS dual suply level shifter for a 0.5 V input and 1 V output in standard 1.2 V 65nm technology process[C]//Communications and Information Technology,ISCIT.Icheon:IEEE,2009:963-966.

[3]MOGHE Y,LEHMANN T,PIESSENS T.Nanosecond delay floating high voltage level shifters in a 0.35μm HV-COMS technology[J].IEEE Journal of Solid-state Circuits,2011,46(2):485-496.

[4]徐栋麟,郭新伟,徐志伟,等.SSN 研究及其在VLSI设计流程中的应用[J].电子学报,2001,29(11):1471-1474.

XU Dong-lin,GUO Xin-wei,XU Zhi-wei,etal.VLSI design automation procedure to optimize SSN performance[J].ACTA Electronica Sinica,2001,29(11):1471-1474.(In Chinese)

[5]PAYAM H,MASSOUND P.Analysis and optimization of ground bounce in digital CMOS circuits[C]//Computer Design.Austin T X:IEEE,2000:121-126.

[6]JOU S J,CHENG Wei-chung,LIN Yu-tao.Simultaneous switching noise analysis and low bouncing buffer design[C]//Custom Intergrated Circuits Conference.Santa Clara,CA:IEEE,1998:545-548.

[7]CHAN S R,TAN F N,MOHD-MOKHTAR R.Simultaneous switching noise impact to signal eye diagram on high-speed I/O[C]//Quality Electronic Design (ASQED).Penang:IEEE,2012:200-205.

[8]DWIVEDI D,DWIVEDI S,POTLADHURTHI E.Voltage up level shifter with improved performance and reduced power[C]//Electrical & Computer Engineering (CCECE).2012 25th IEEE Canadian Conference:IEEE,2012:1-4.

[9]SUHWAN K,STEPHEN V K,DANIEL R K,etal.Mimizing inductive noise in system-on-a-chip with multiple power gating structures[C]//Solid-State Circuits Conference.Estoril,Portugal:IEEE,2003:635-638.

[10]KUMAR Y,PALIWAL S,CHANDAN K R,etal.A novel ground bounce reduction technique using four step power gating[C]//Engineering and Systems(SCES).Allahabad:IEEE,2013:1-5.