基于MSP430电力参数监测的设计与实现

2015-12-10司其东郭顺生

司其东 郭顺生

武汉理工大学(430070)

基于MSP430电力参数监测的设计与实现

司其东 郭顺生

武汉理工大学(430070)

设计了一种电力系统参数测试仪,以CPLD与MSP430单片机为核心,实现了对电网关键性参数进行多通道测量的软件和硬件系统设计,为电力系统参数的准确检测提供了重要保障。

CPLD;MSP430;频率测量;相位测量

0 引言

电网常见的污染如电压的上凸和下凸、谐波、三相不平衡等[1]是影响电能质量的重要因素,不对它们加以控制会造成严重的经济损失。所以有必要设计一套高效的监控测量装置,实现对电能质量全面、长期的跟踪。本设计以CPLD和MSP430单片机为核心,设计了一种电网关键性参数,包括各相幅度、频率和相位差的六路通道测量仪器。仪器对电力系统的调控管理具有重要意义。

1 系统总体方案设计

1.1 系统的总体结构

电力参数测量仪具体工作流程为:三相电源的各相电流、电压分别经过电流和电压变换器后,全部转换为电压信号,并且电压信号的幅度在10V以内。然后这些信号分别进入线性整流电路和波形转换电路。

线性整流电路的主体为TL082运放,该电路将原始正弦信号转换为直流电压信号,再通过MSP430的ADC通道得出直流电压信号的幅度,推算出原始信号的幅度有效值。由LF356运放为主要构件的波形转换电路是将原始信号转换成与原始信号过零点相同且符合LVTTL电平标准的方波信号,CPLD中的计数器通过对该方波信号进行计数就可以得到输入信号频率的计数值,同时对比两路信号波形的上升得到这两路信号的相位差。这些数据将由单片机周期性地读取。

1.2 系统软件程序框架

图1 系统软件总体程序流程图

系统的总体程序流程图如图1所示。系统进行初始化后等待按键按下,接收命令。初次启动时会要求对时间进行设置,因为系统所有测量数据都必须有对应的时间参数,否则数据将不能反映出电网的运行情况。完成按键解析后,MSP430单片机使CPLD开始对输入信号测量频率和相位差,同时MSP430单片机开启ADC通道,测量输入信号幅度。

2 系统的设计与实现

2.1 幅度测量的设计

本设计对于幅度测量A/D电路使用的是MSP430F169单片机里的A/D模块。本系统设计的要求是处理六路输入信号的模数转换,使用MSP430单片机本身的A/D功能模块,不仅进一步缩小系统的面积,同时充分利用了MSP430F169单片机自身的资源,使用单片机8个A/D通道中的6个,发挥出了MSP430单片机在本系统中相对其他型号单片机的优势[2]。

2.2 CPLD逻辑单元设计

2.2.1 频率测量的设计与实现

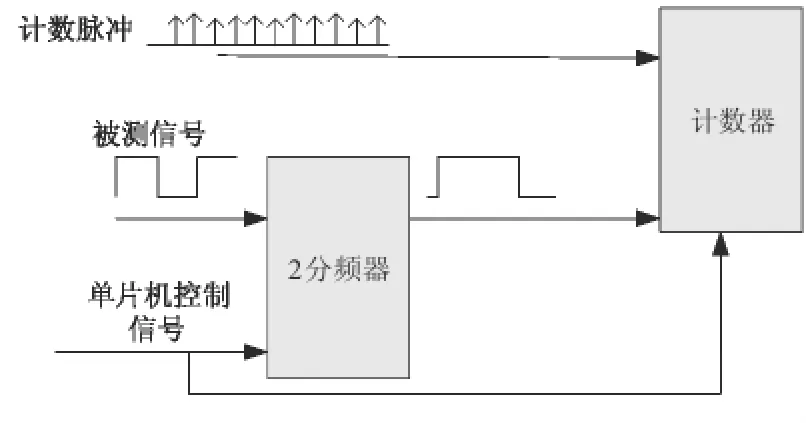

图2 频率测量示意图

分频器对被测信号进行分频,得到的门控信号控制计数器进行计数,使得计数器以被测信号的周期时间长度进行计数。因为分频器具有自锁功能,所以当完成一次分频后它将停止工作,这也使得它给计数器发出的门控信号只有一次,保证当计数完成后计数器里的数据将保持不变,等待单片机取走数据。因为计数的时间为被测信号的一个周期,考虑到分频器需要等待被测信号的上升沿进行分频,本系统中计数器计数时间最长为2个被测信号周

期时间,而本设计的信号测量最低频率为40Hz,所以计数器完成计数最长需要50ms,远小于单片机两次读数时间。同时设计的计数器为16位,在2 MHz计数脉冲下,最低可以测量到的频率为2000 000Hz/65536=30.5Hz,满足系统设计要求。

2.2.2 相位测量的设计与实现

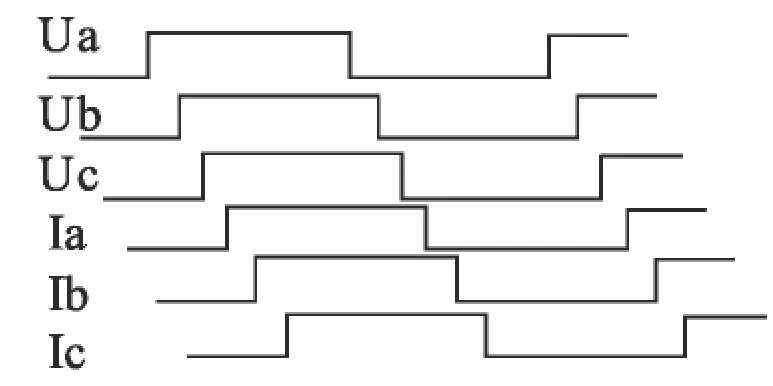

对于6路输入信号,要测量的相位差有6个,分别记输入的6路信号名称为Ua、Ub、Uc、Ia、Ib、Ic、则要测量的相位差为Ua与Ub、Ua与Uc、Ub与Uc、Ua与Ia、Ub与Ib、Uc与Ic。

图3 6路输入信号的相位关系示意图

当Ub上升沿到来时,计数器的计数值就会锁存起来,这样锁存器里的数据就是Ua上升沿到Ub上升沿之间的计数值,也就是它们两者上升沿的时间差,再根据信号的频率就可以得到它们的相位差。

2.2.3 CPLD与MSP430单片机通信模块

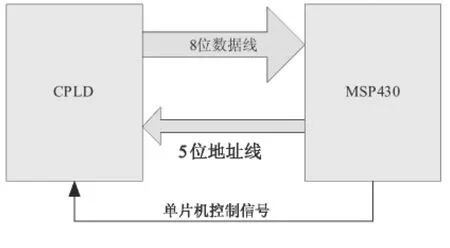

本设计中的CPLD有6个计数器,并以这6个计数器为基础测量9个相位差,因此实际需要15个16位的寄存器。因为需要切换计数脉冲,所以计数脉冲的信息需要告诉单片机,使单片机选用合适的计算公式。计数脉冲的选择有3个,因此有3个编码。对于MSP430单片机而言,IO组输入寄存器都是8位的,因此CPLD的寄存器数据都以8位数据宽度进行传输。即频率和相位差的数据共有30个8位寄存器,再加上计数脉冲编码的1个8位寄存器,总共31个寄存器。对这些寄存器进行地址编码,可以知道使用5根地址线就可以使得MSP430单片机读取到CPLD中所有的数据。

如图4所示,MSP430对CPLD的控制是通过一根控制信号线。当单片机通过这条信号线发出高电平给CPLD时,CPLD进行测量,由于测量时间远小于单片机读取周期,当单片机读取数据时所有测量结果已经得到。读完数据后单片机会发出低电平,使CPLD清零,除了计数脉冲编码的信息以外所有的数据将被清零。清零等待一段时间后,单片机再次发出高电平。通过这根控制信号线,实现MSP430单片机对于CPLD的控制[3]。

图4 CPLD与单片机通信结构

3 总结

本设计采用了CPLD以及MSP430F169单片机进行系统设计。利用CPLD的可编程逻辑器件的特点,大大简化了过去用独立芯片搭建的数字电路。使用MSP430单片机的多通道ADC可以有效简化模数转换电路。结合CPLD和MSP430可以完成6路输入信号的频率相位和幅度的测量。

本系统还存在不足之处,有待改进,主要表现在以下方面:

1)由于原始信号输入需要经过各种调理电路,这些电路的原器件会引入测量误差,加入误差表,这样才能真正做到测量结果与实际相同。

2)由于测量电压的幅度和相位的输入源相同,所以测量相位的输入信号也是经过互感器后的信号。由于互感器的比例关系,在输入信号微弱时,输入到波形转换电路中的信号幅度很小,这将导致在此时测量的电压相位不够准确。

[1]牛博,王建华,宋政湘,等.基于现场可编程门阵列的电能质量检测系统设计[J].电力自动化设备,2007,27(4):91-94.

[2]高秀英.浅谈电能质量与改善措施[J].应用能源技术,2010 (04):41-45.

[3]Awad,M.S.Reviewpowerqualityissues[J].ModernApplied Science.2012,6(2):52-59.

[4]葛小燕,李朋,拜国栋.FPGA技术在电力系统电能质量监测中的研究应用[J].科技综述,2008,36(3):36-40.