基于SCCB总线配置的FPGA视频采集系统设计

2015-12-07杨会建杨阳张环朱莹

杨会建,杨阳,张环,朱莹

(长春理工大学 电子信息工程学院,长春 130022)

视频图像采集传感器主要有CCD传感器和CMOS传感器两种。CMOS传感器是利用CMOS工艺制造的图像传感器,主要利用了半导体效应。它可以轻易地将周边电路(如AGC、CDS、Timing generator、或DSP等)集成到传感器芯片中[1]。因此与CCD传感器相比,CMOS传感器具有成本低、低功耗及高整合度等特点[2]。近年来,CMOS传感器得到了越来越广泛地应用,视频监控系统就是其中一个领域。本设计正是针对这一领域,利用FPGA的强大并行处理能力,将CMOS传感器采集信息进行并行处理后实时显示。

1 SCCB通信设计

1.1 硬件设计

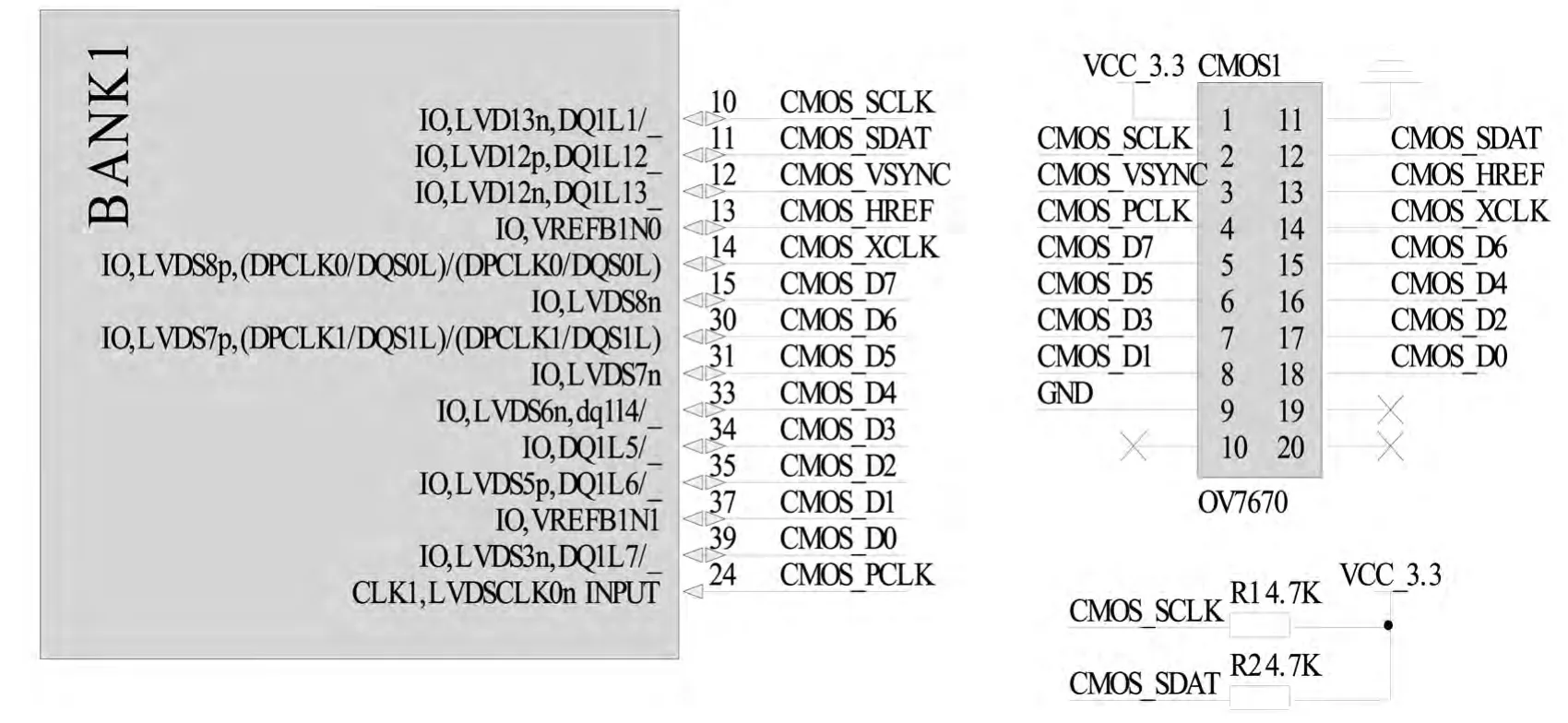

采用FPGA的EP2C8Q208C8作为主控芯片,CMOS传感器采用具有内嵌放大器、A/D转换、颜色空间转换、白/黑像素校正等单元的由OmniVision所研制的OV7670图像传感器。每次上电复位后首先通过主控芯片根据SCCB通信协议对OV7670相关寄存器进行配置,使其工作在RGB或YUV、自动白平衡等状态。在初始化CMOS传感器之后,为确保数据的准确性,前10帧数据丢弃,然后开始进行图像采集。

图1 OV7670硬件原理图

OV7670的硬件连接图如图1所示。采用3.3V电压供电,CMOS_XCLK为系统输入时钟,由FPGA分频后的25M时钟提供,CMOS_PCLK为输出像素时钟,用来为数据采集提供时钟。CMOS_SCLK和CMOS_SDAT为SCCB通信时所需的时钟信号和数据信号,其中时钟信号为单向输入,数据信号为双向传输,初始化OV7670只需通过这两个信号线即可。CMOS_D[7..0]为8位数据信号,用来采集视频信息。CMOS_HREF和CMOS_VSYNC是视频采集时的行帧同步信号,配合像素时钟使用。值得注意的是,对于SCCB通信信号CMOS_SCLK和CMOS_SDAT必须外接上拉4.7K电阻,才能输出高电平。因为SCCB内部采用了Open Drain结构,如果不接上拉电阻只能输出低电平。

1.2 通信原理和寄存器配置

1.2.1 通信协议

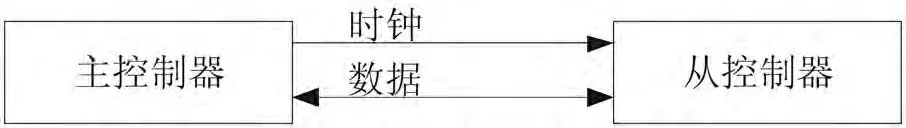

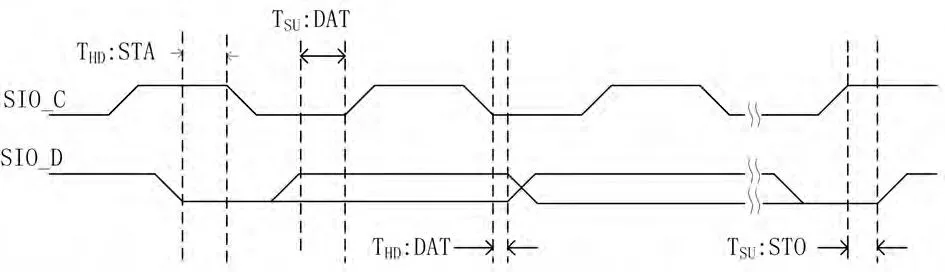

SCCB(OmniVision serial camera control bus),是欧姆尼图像技术公司开发的串行摄像头控制总线[3],广泛应用于OV系列图像传感器上。SCCB是一种三线总线,由SCCB_E、SIO_C和SIO_D组成。SCCB_E是控制芯片工作的信号,当进行通信时,必须置1,SIO_C是时钟信号,SIO_D是双向数据信号,一个主控制器可以控制至少一个以上从设备。当SCCB_E无效时,变为两线控制总线,兼容I2C总线接口。本文采用两线SCCB接口如图2所示[4],只有SIO_C(时钟信号线)和SIO_D(数据信号线)两条[5]。FPGA作为主控制器,用来对OV7670(从控制器)的寄存器地址0x00-0xC9进行相关配置,使其工作在不同的模式下,如RGB(565)或YUV、镜像方式、自动白平衡等。

图2 两线控制模块

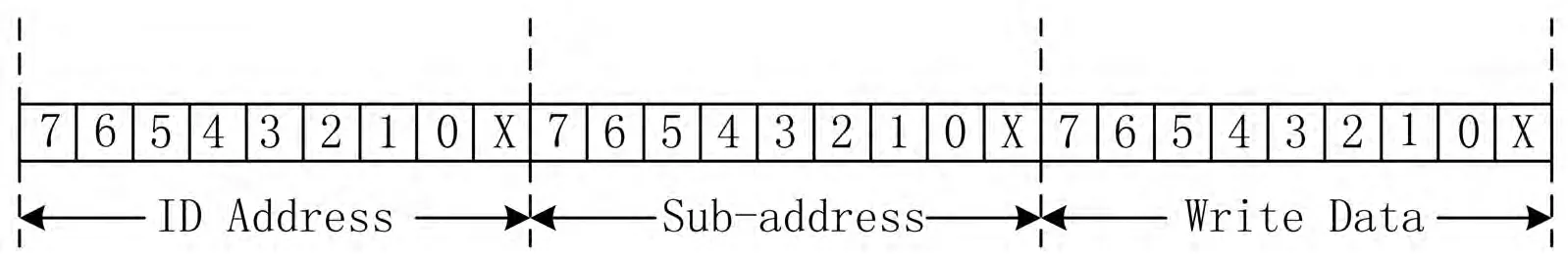

SCCB的写操作通信协议如图3所示。ID Address是CMOS的器件地址,OV7670为0x42;Sub-address为寄存器地址;Write data是具体的写入数据,X表示无关位。对于读操作通信协议,第一、二相和写操作一样,第三相的地址为0x43,第四相为写入数据,最后一位NA必须置1。

通信过程如下:首先发送器件ID地址,然后发送寄存器地址,对于写通信格式,通过FPGA往CMOS寄存器里写数据。对于读通信格式,需要再次发送CMOS器件地址,但需注意此时最低位应为1,最后再将寄存器里数值读出。THD:STA为在将时钟拉低之前必须提前将数据位拉低的最小开始条件保持时间,至少为0.6μs。

图3 SCCB写通信数据格式

系统在检测到SIO_C和SIO_D都为逻辑低后就进行数据通信。在通信过程中,每次传输一位数据在时钟上升沿到来之前必须至少有0.1μs的建立时间。而在时钟上升沿之后同样数据要保持一定的时间不变,这个时间称为保持时间THD:DAT,最小值可以为0。只有当建立时间和保持时间都满足通信协议要求,数据才能被写入触发器。

每次通信完之后,在将数据位SIO_D拉高之前需将时钟SIO_C拉高TSU:STO的时间,至少为0.6μs。通信协议如图4所示。

图4 SCCB通信协议

1.2.2 SCCB寄存器配置

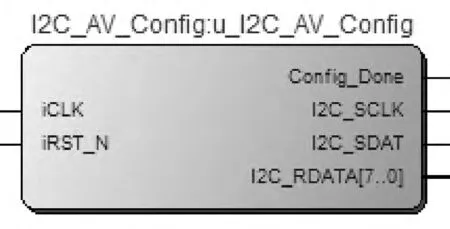

利用Verilog语言在Quartus中对CMOS传感器进行模块化设计,生成的RTL视图如下图5所示。iCLK是FPGA提供的25M时钟用来给OV7670的系统时钟,iRST_N是系统复位信号,Config_Done是寄存器配置完后的标志位。主要是通过I2C_SCLK和I2C_SDAT根据SCCB协议来设置相关寄存器值,从而驱动OV7670,使其在一定的模式下采集视频信息。

图5 SCCB配置RTL视图

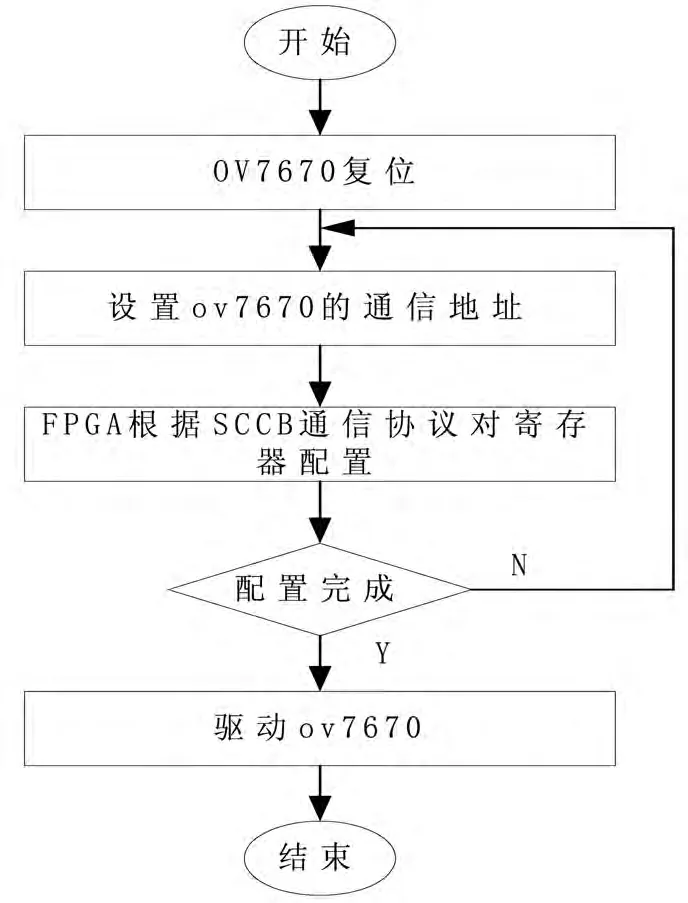

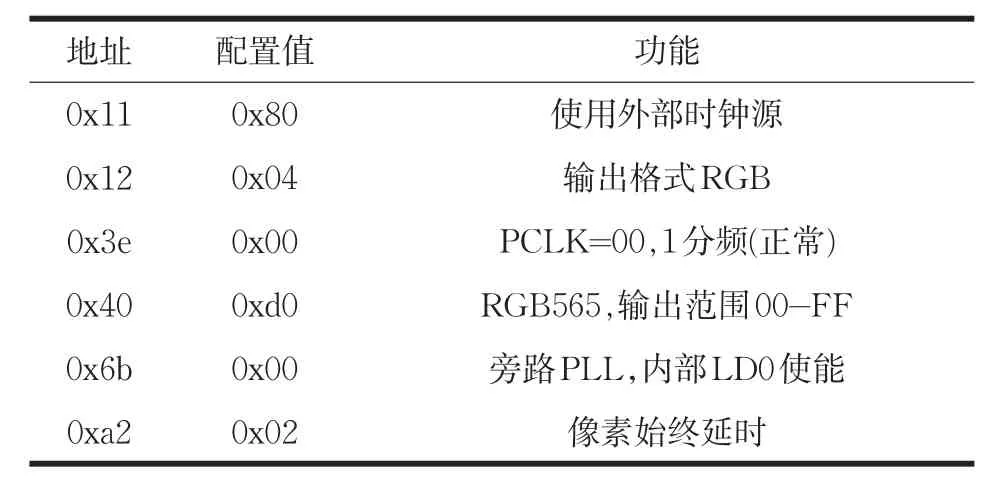

图6是配置OV7670的流程图。系统上电后通过硬件复位使整个芯片处于复位状态。复位结束后,FPGA根据SCCB的通信协议设置OV7670的物理地址、寄存器地址,然后再对相关寄存器配置,在对所有寄存器配置完成后,接下来就可以驱动OV7670。因为每次发送时的物理地址是固定的0x42,所以寄存器LUT_DATA只需存储寄存器地址和需配置的数据即可。本设计为了提高系统的灵活性,采用索引的方式,程序设计中只需让索引值LUT_INDEX小于寄存器数n即可。当需配置的寄存器数改变时,只需改变寄存器数n。部分寄存器的配置如表1所示。

图6 SCCB流程图

表1 部分寄存器的配置

1.2.3 SCCB波形仿真

为了验证程序通信的正确性,需要利用Modelsim仿真工具对其进行波形仿真。图7是对寄存器配置的仿真波形图。从仿真波形可以看到,此时的开始条件保持时间为0.1ms,开始条件建立时间远大于600ns,建立时间是0.05ms,保持时间为0,仿真结果和通信协议很好的符合一致。

图7 Write寄存器仿真波形

2 视频数据采集

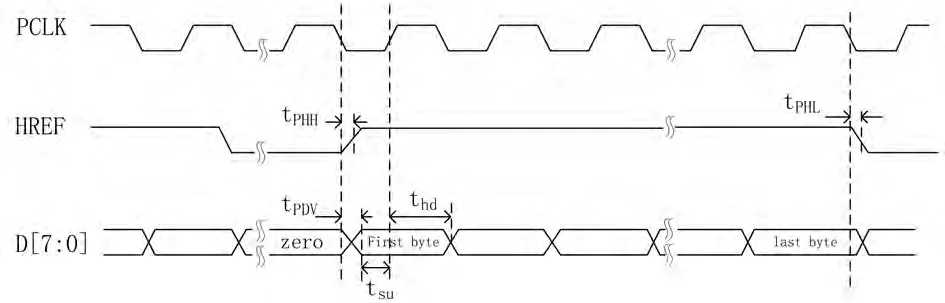

配置完OV7670寄存器后,可进行视频数据采集。数据采集的信号线有像素时钟PCLK,行同步HREF和帧同步VSYNC[6],分辨率为640*480。帧同步VSYNC低有效,行同步HREF为高时进行数据采集,且每次HREF维持高电平的时间为640个像素时钟,在此期间不断采集数据送至FPGA内部WRFIFO进行缓存。当VSYNC低电平持续507个像素时钟后被拉高,至此一帧数据采集完成[7]。图8是其时序图,tsu为建立时间,≥15ns,thd是保持时间,≥8ns;下降沿到数据输出有效时间tPDV≤5ns。tPHH和tPHL分别是像素时钟下降沿到HREF上升沿和下降沿的时间,最大为5ns,最小可以为0。

图8 数据采集时序图

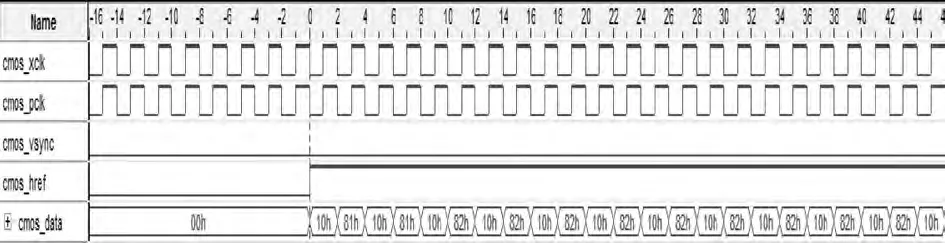

图9是利用SignalTap II采集的波形图。从波形图中可知,系统时钟和像素时钟同步,在cmos_vsync为低且cmos_href为高时数据开始采集,之前数据都为0。在每次时钟的上升沿到来之前数据已经稳定约20ns,大于数据建立时间要求的至少15ns。保持时间同样约为20ns,大于数据保持时间要求的至少8ns。波形很好的满足了建立时间和保持时间等各项时间系数,符合设计要求。

图9 SignalTap II信号波形图

3 视频采集实时显示

视频采集显示部分采用通用的工业VGA标准接口,在FPGA和VGA接口之间加入ADV7123数模转换芯片,将FPGA内部缓存在RDFIFO中的16位数据读出经过ADV7123转换[8]成3位模拟量输出。对于VGA的场同步信号VSYNC和行同步信号HSYNC,是由FPGA同步控制的。需要注意的是,和CMOS采集信号的帧行信号不同,当VSYNC和HSYNC都为高电平时,数据有效输出。

对于要求显示的静态字体,利用FPGA的ROM来配置,将显示的字体以.mif文件加载到ROM中,视频实时显示如图10所示。

图10 视频实时显示

4 结论

本设计是针对视频采集系统设计的方案,以并行、快速的FPGA为主控芯片,采用了OmniVision公司的OV7670传感器来采集视频信息。根据SCCB通信协议对OV7670相关寄存器进行了控制,使其采集信号格式为RGB565。而后利用SignalTap II对视频采集信号进行了时序分析,最后VGA视频实时显示很好的证明了该设计的可行性。该设计除具有电路简单,低功耗、低成本等一系列优点外,只要将外部电路稍加改动就可以应用于其他视频采集系统中,能够为以后设计出更高级的视频监控系统奠定基础。

[1]CMOS传感器_百度百科[EB/OL]http://baike.baidu.com/view/356089.2015-02.

[2]刁晓静.无线多传感器网络中图像传输系统的实现[D].南京:南京理工大学,2006.

[3]杨侃,孙尧,詹艳艳.基于S3C44B0嵌入式系统的SCCB 设计与实现[J].现代电子技术,2008,31(22):183-186.

[4]苑玮琦,汤永华.OmniVision图像传感器的SCCB总线协议在DSP中的实现[J].仪器仪表学报,2006,27(6):1687-1688.

[5]褚红娟,隋国荣.基于SCCB通信的FPGA视频采集模块[J].自动化仪表,2010,31(11):68-70,74.

[6]刘鑫.基于ARM的图像采集系统的设计[D].武汉:武汉理工大学,2007.

[7]薛敏彪,吴广伟,王健,等.嵌入式机载视频输出接口设计[J].现代电子技术,2011,34(2):9-11,14.

[8]高强,王炜,刘建,等.SCCB总线配置的FPGA视频采集与显示系统设计[J].单片机与嵌入式系统应用,2014,14(1):73-75.