6英寸高均匀性P型硅外延片的工艺研究

2015-12-05李明达

吕 婷,李明达,陈 涛

(中国电子科技集团公司第46研究所,天津 300220)

1 引言

目前P型硅外延材料是制备微波功率MOS器件和光电探测器件的关键基础材料,外延层的质量与器件性能密切相关[1~3]。近年来,随着微波功率MOS器件和光电探测器件使用量的快速增加,以及对器件性能的要求不断提高,对高质量硅外延片的需求也愈发迫切。但目前国内外延厂商研制6英寸(152.4 mm)P型硅外延片还处于起步阶段,在缺陷密度、均匀性、过渡区宽度等外延材料的性能控制上与国外材料存在较大差距,尚不能满足器件需求,而国外外延厂商在6英寸P型硅外延片上已实现低缺陷、高均匀性等关键技术的突破,进入量产阶段,但价格昂贵,时刻面临国内禁运的风险,已不能满足国内微波功率MOS器件和光电探测器件厂商的需求。外延片表面积的增大决定着厚度/电阻率均匀性的控制技术尤为关键。厚度的一致性直接影响器件工艺的光刻聚焦精度;电阻率的一致性直接影响器件输出电压幅度和导通电阻的稳定性,都影响器件的性能和可靠性[4]。

采用CVD(化学气相沉积)技术在6英寸重掺B的硅衬底上制备高均匀性的P型外延层较为困难,这里包含两个原因:(1)外延片的外延层掺杂浓度(~l015cm-3)与衬底的掺杂浓度(~l018cm-3)相差3个数量级,在掺杂浓度较低的中高阻外延片的生长过程中,轻微的自掺杂都会严重影响外延层的电阻率均匀性,硼原子作为掺杂剂,半径小、质量轻,同P、As、Sb等元素比较,在流动气体中相对扩散距离较大,更容易到达反应腔器壁、石墨基座等的表面,并被大量吸附。所以自掺杂效应严重,电阻率均匀性极难控制[5~6]。(2)硅片直径的扩大,造成衬底表面、背面及边缘处的杂质在高温下更易挥发,自掺杂效应增强,严重影响电阻率均匀性。本文通过流场调节工艺、基座包硅工艺、变流量解吸、两步生长工艺等关键工艺的改进,有效改善了厚度和电阻率分布的均匀性,最终使6英寸P型外延层满足器件使用要求。

2 工艺试验

2.1 外延设备

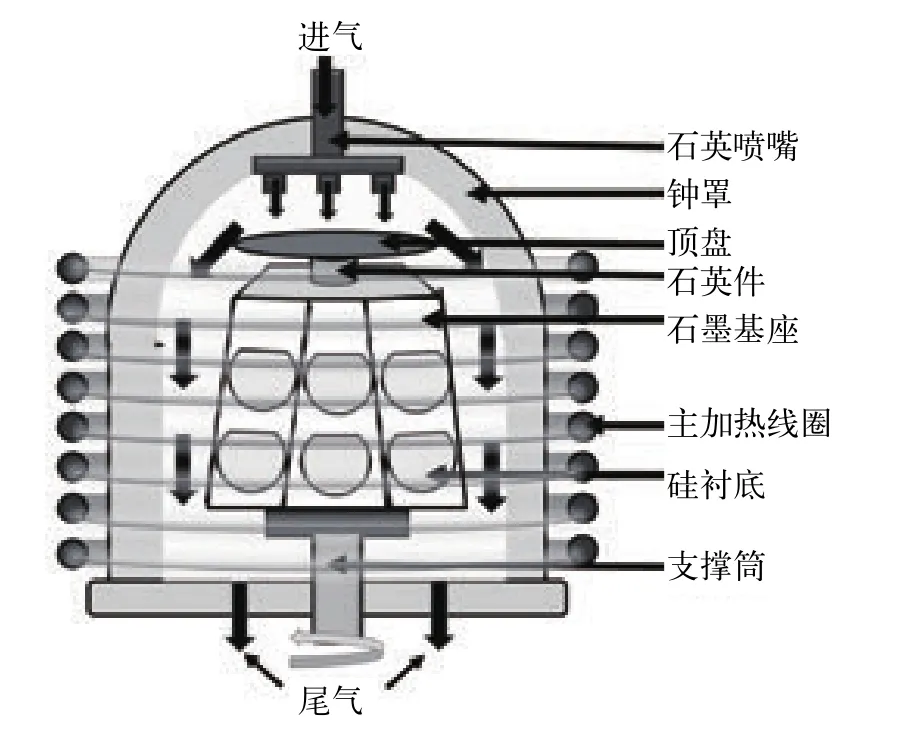

本文中硅外延层沉积的设备为意大利LPE公司PE-2061S型常压桶式外延炉,基本结构如图1所示。该外延炉采用高频感应的加热方式,以高纯桶式石墨基座作为加热感应体,由7个中心对称的正梯形侧面组成,每次实验可放置两排共14片6英寸硅单晶抛光片。反应气体从钟罩顶部气体入口处进入反应室,从排成一圈的六个石英喷嘴喷出,经石英顶盘阻挡,沿基座与钟罩之间向下,在高温下反应,在硅片表面沉积生长外延层,反应尾气在下部排出。实验中基座的旋转速度设定为4 r/min。

2.2 衬底材料与外延结构

为了满足器件对所需外延片提出的指标要求,本文选用高质量的硅单晶衬底进行外延生长。衬底材料选用重掺B的P型单晶硅抛光片,其直径为150 mm,晶向为 <100>±0.5°,厚度为 675±15 μm,电阻率 0.01~0.02 Ω·cm,平整度≤ 5 μm,总厚度偏差≤10 μm,局部平整度<1.5 μm(3 cm×3 cm),翘曲度<20 μm,弯曲度<20 μm。同时,衬底背面依次包覆有800 nm的多晶硅背封层和500 nm的SiO2背封层,以抑制高温状态下重掺硼衬底背面的杂质挥发,降低自掺杂效应。本工艺制备的外延层导电类型为P型,直径为150 mm,厚度设计为20±1.0 μm,厚度不均匀性<1%,电阻率设计为13±1.0 Ω·cm,电阻率不均匀性<1.5%,表面光亮,无滑移线、雾、划道、凹坑、橘皮、沾污等缺陷。

图1 PE-2061S外延炉结构示意图

2.3 外延生长

外延生长中采用的反应气体为SiHCl3和H2,H2经纯化后的纯度为99.999 99%,既是参与反应的气体,还起到了携带气体的作用。作为硅外延生长原料的SiHCl3硅源纯度为99.95%,其本征电阻率高于1 000 Ω·cm。由于SiHCl3常温下为液态,实验采用H2鼓泡的形式将液态转变为气态进入反应室。衬底表面发生的主要化学反应为[10]:

此外,硼烷气体作为掺杂源,纯度为50×10-6,流量为79.5 sccm。

3 实验结果及分析

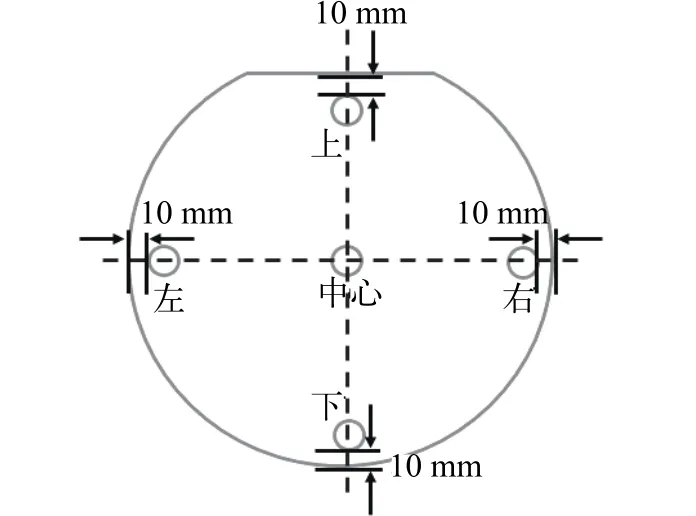

为保证测试过程的可靠性和稳定性,每次实验后选取基座固定片坑位置的外延片进行表面质量和电学参数的测试。外延层的导电类型采用NC6800型晶片分选机测量,表面质量采用强光灯目检,层错和位错缺陷采用CMM-70E金相显微镜观测。外延层厚度利用Nicolet 6700傅里叶变换红外光谱仪(FTIR)测量,分辨率为0.001 µm。测试方法为5点法(选择硅片的中心点及4个距边缘10 mm的测试位置),如图2所示。外延层的表面电阻率利用SSM 495汞探针电阻率测试仪(C-V),分辨率为0.000 1 Ω·cm,同样采用5点法测试。

P型外延样片在进行电阻率测试前的准备为:

(1)样片放入HF水溶液浸泡2 min,腐蚀掉表面的氧化层;(2)用电阻率大于15 mΩ·cm的去离子水冲洗5 min;(3)在N2下吹10 min。

图2 外延片的5点测试位置分布图

外延层的导电类型经晶片分选机测量显示为P型。采用强光灯观测到本实验制备的硅外延片的表面质量,当生长温度为1 150 ℃时,表面光亮,其表面无雾、划道、沾污、崩边、桔皮及滑移线等缺陷。而当采用1 120 ℃的较低生长温度时,表面出现红雾状的缺陷,这是由于温度较低时掺杂剂容易发生聚集,进而在外延层表面形成小的S坑缺陷;而当采用1 180 ℃的生长温度时,表面遍布垂直于主参方向的滑移线,其长度大于半径,数量>20条,这是由于温度过高,热应力不断积累,当超过引起晶体滑移线的应力临界值时,便产生了滑移线。由于雾缺陷和滑移线都属于载流子复合中心,使器件噪声增加,漏电流增大,容易引起软击穿和低击穿等,进而影响器件的高性能和成品率,因此本实验选用1 150 ℃作为合适的生长温度。同时采用金相显微镜观察该生长温度制备的外延片无层错和位错缺陷。

鉴于厚度均匀性主要与外延炉内的气流分布相关,本实验首先采用3种不同的主工艺气流量,观察对厚度均匀性的影响,分别命名为1#、2#和3#,结果如表1所示。

表1表明,随着主工艺气流量的增加,显著改变了外延片的纵向厚度分布,厚度不均匀性随气流量增加呈现先减小后增大的趋势,由结果可知320 slm的主H2流量可作为本文最为理想的制备工艺条件,获得的最优外延片厚度不均匀性为0.47%。

在厚度均匀性改善之后,接下来要改善电阻率的均匀性,为有效抑制自掺杂效应,首先采用基座包硅工艺,即在每次外延生长之前用高纯度HCl在1 160 ℃的高温下首先对石墨基座进行腐蚀处理,以去除基座表面残余的沉积物。为了进一步抑制基座片坑内的杂质向外挥发。实验采用高纯度三氯氢硅(SiHCl3)作为硅源,在石墨基座表面淀积一层无掺杂多晶硅。采用包硅厚度0、2 μm、4 μm,分别命名为4#、5#、6#,对电阻率均匀性的影响效果如表2所示。当包硅厚度超过2 μm时,虽然电阻率均匀性可以达到进一步改善,但因外延片背面吸硅形成颗粒,造成几何参数变差,将严重影响器件工艺的光刻聚焦,因此包硅厚度为2 μm为最为理想的工艺条件。

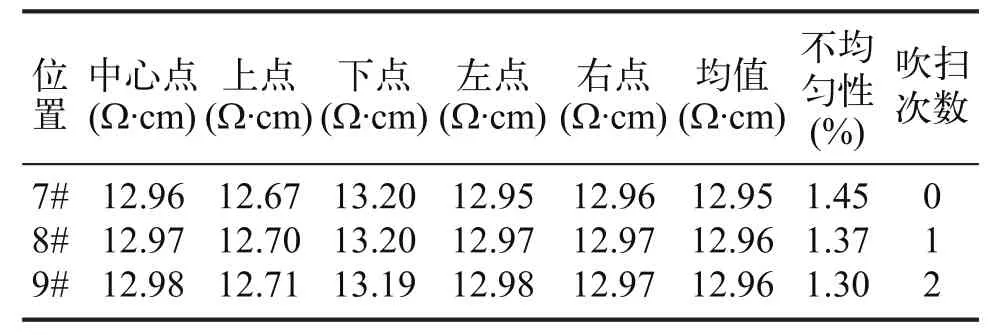

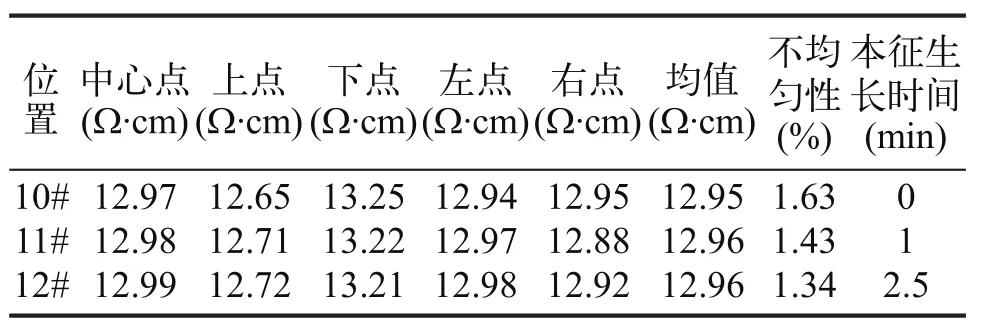

表1 采用不同工艺气流量测试片的厚度分布

现有研究表明,在外延工艺中增加变流量吹扫工艺,能够不断改变外延滞留层的厚度,将“静态”的滞留层变为“动态”,将滞留层内的杂质不断减少,可以有效抑制自掺杂效应,进而提高外延层的电阻率均匀性[7]。实验中在外延生长前通过变流量吹扫工艺,将主工艺气体H2在300 slm到350 slm 之间做周期性快速变换,变化次数分别为0次、1次、2次时,分别命名为7#、8#、9#,对外延层的电阻率均匀性的影响如表3所示。实验结果表明采用2次变流量吹扫工艺可以起到显著改善电阻率的作用。

为进一步有效抑制自掺杂效应,本实验还采用两步外延法,即第一步先生长一层无掺杂本征外延层,对衬底片表面及边缘进行包封处理,阻止衬底杂质的进一步向外挥发,同时在外延层/衬底界面处的杂质纵向浓度分布就会变得陡峭,使过渡区宽度变窄。但如果本征层生长时间过长, 也会导致本征层表面电阻率因急剧爬高而超过外延层电阻率, 形成高阻夹层, 因电阻率过高的位置会造成器件导通电阻过高,正向电压过大,由此极易引发器件失效,需要尽量避免此类风险。因此实验中分别采用本征生长时间为0、1 min以及2.5 min,命名为10#、11#和12#,观察对电阻率均匀性的影响,结果如表4所示。结果表明采用2.5 min的本征生长时间对改善外延层电阻率效果最佳。

以上结果表明采用合适的基座包硅厚度、本征生长时间以及变流量解吸次数,电阻率的不均匀性将得到很大改善,当基座包硅厚度为2 μm、本征生长时间为2.5 min、变流量解吸次数为2次时的组合,结果如表5所示,电阻率不均匀性为1.28%,可实现低于1.5%的目标。

表2 采用不同基座包硅工艺条件测试片的电阻率分布

表3 采用不同变流量解吸工艺条件测试片的电阻率分布

表4 采用不同本征生长时间测试片的电阻率分布

根据表1和表5所示的参数结果,采用最优化工艺获得的6英寸P型测试片的厚度不均匀性小于1%,电阻率不均匀性小于1.5%,从性能参数上满足微波功率器件和光电探测器件的研制要求。

表5 采用最优化条件获得的测试片的电阻率分布

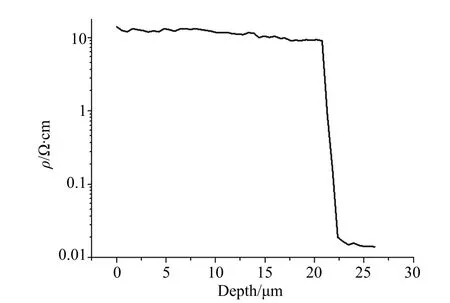

利用SRP 2000型扩展电阻测试仪检测该条件下制备的外延片的过渡区形貌,测量精确度为0.2。根据国际半导体设备和材料协会(SEMI)标准,对过渡区宽度W的定义为:W=DT-DB,其中DT为外延层电阻率达到目标电阻率90%深度,DB为外延层电阻率达到目标电阻率10%的深度。图3所示为外延层/衬底的过渡区形貌曲线。过渡区宽度经测试为2.0 µm,由于过渡区宽度≤外延层宽度的10%,因此可以满足器件对外延片的技术要求。

图3 外延层/衬底过渡区形貌曲线

4 结论

本文主要研究了微波功率MOS器件及光电探测器件用6英寸高均匀性P型硅外延片的制备方法,主要通过流场调节工艺、基座包硅工艺、变流量解吸工艺、两步生长工艺等关键工艺的改进,有效降低了自掺杂效应,改善了厚度和电阻率分布的不均匀性,成功研制出满足器件所需的硅外延材料,其外延层晶体结构完整,厚度不均匀性<1%,电阻率不均匀性<1.5%。

[1] 封慧峰,常素珍. P型衬底浓度对外延电阻率一致性的影响 [J]. 电子制作 , 2014, 11∶ 076-077.

[2] 安静. P 型硅外延片工艺技术的研究[D]. 天津:河北工业大学,2011.

[3] 李杨,王文林,薛兵,等. CCD成像器件用P型外延材料的工艺研究[J]. 电子制作, 2014, 13∶ 038-039.

[4] 王文林,闫锋,李杨,等. CVD法制备高质量硅外廷片的工艺研究[J]. 科技信息,2013∶ 435-437.

[5] 傅雄强. p型硅外延层电阻率的控制[J]. 微电子学,1994, 24(4)∶ 49-52.

[6] 刘玉岭, 金杰, 徐晓辉,等. 硅CVD外延自掺杂效应的分析研究[J]. 电子科学学刊,1996, 18(3)∶ 332-336.

[7] 索开南. 重掺衬底硅外延层杂质来源及控制方法分析[J]. 电子工业专用设备,2011, 201∶ 1-3.