一种应用于流水线ADC的采样保持电路设计

2015-12-05朱晓宇居水荣石乔林

朱晓宇 ,居水荣,石乔林,李 华

(1. 江南大学物联网工程学院,江苏 无锡214122;2. 中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

流水线ADC以其精度、速度、功耗等性能的良好折衷[1],成为奈奎斯特型模数转换器中的研究热门。采样保持电路作为流水线ADC的第一级,其性能直接制约了ADC整体性能的提高。

本文设计的采样保持电路通过全差分结构及底极板采样技术,有效地抑制了电荷注入效应,时钟馈通及偶次谐波失真。采用改进的栅压自举开关减小了开关面积,有效地减小了开关的导通电阻,减小信号的非线性失真[2]。设计了折叠式共源共栅两级运算放大器,采用共源共栅密勒补偿,保证系统稳定性的同时减少了有限增益引起的误差[3]。选取的电容翻转型结构,其近于1的反馈系数降低了对运放单位增益带宽的要求,降低了系统功耗[4]。

2 采样保持电路结构

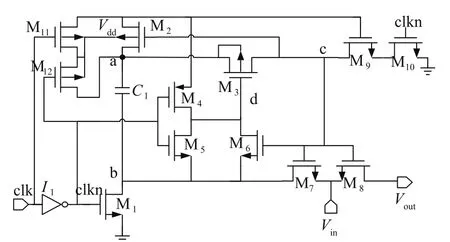

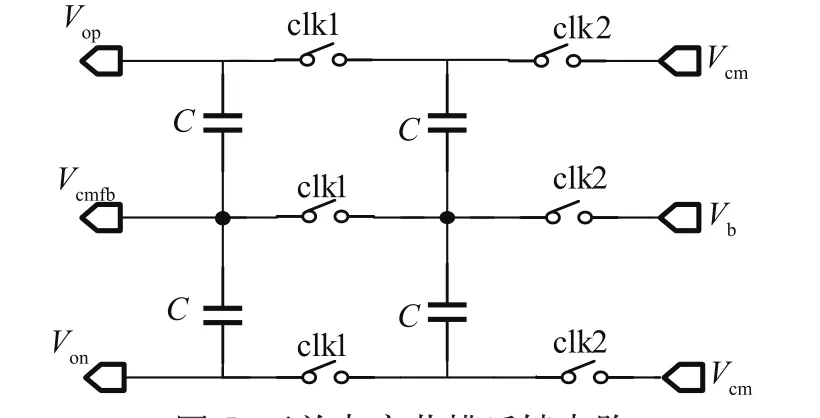

本文所采用的电容翻转采样保持电路结构如图1所示。

图1 电容翻转采样保持电路

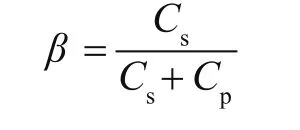

其中clk1和clk2为两相不交叠时钟。在clk1为高电平时,电路工作在采样相,Cs底极板通过栅压自举开关跟随输入信号,顶极板与输入共模信号相连,顶极板远离衬底,因而其较小的寄生电容提高了采样精度。clk1’与clk同相,在clk1断开之前,clk1’提前关断,此时Cs无信号回路,电荷不再变化,因而开关断开时的电荷注入效应不再影响采样电容上的电荷。当clk2为高电平时,电路工作在保持相,采样电容下级板直接连接至输出端,根据运放虚短及电荷守恒,差模输出电压等于输入差模电压。电容翻转采样保持电路的反馈系数为:

由于顶级板及运放输入端的寄生电容Cp较小,因而其反馈系数β较大,较大反馈系数减小了运放的建立时间,降低了对运放增益带宽积的要求,从而减少了对功耗的限制。

3 栅压自举采样开关及其改进

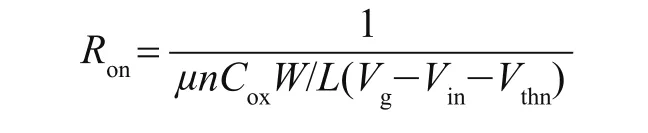

工作在线性区的MOS采样开关其导通电阻为:

式中Vg为电源电压,Vthn为MOS管阈值电压,其导通电阻与输入电压Vin相关,采样电容将不能线性跟踪输入信号,因而将引起谐波失真。栅压自举采样开关原理为:通过电路使式中Vg-Vin在采样相恒保持不变,则其导通电阻可以与输入信号无关,得到与信号无关的导通电阻,减少了采样保持电路的非线性失真。

传统栅压自举开关如图2所示,在clk为低电平时,节点b变为Vdd,节点a升为Vdd+Vclk,此时M3、M4导通,M8截止,节点d拉到电源地,节点c充到Vdd,电容C3两极板间电压保持在Vdd,M8因节点f为高电平截止,电源地通过M11、M10使得节点e为低电平,M12、M13截止,电路处于保持阶段;clk为高电平时,节点c电压通过M8使得节点e电压升高,M9、M12、M13导通,M8的栅源电压保持为C3两端电压Vdd,因而M8的导通电阻保持不变,节点d跟随Vin,节点c因电容电荷守恒升为Vdd+Vin,此时M8、M12、M13的栅源电压都为Vdd,M13的导通电阻与输入无关且保持不变,使得栅压自举开关具有良好的线性度。其中M9、M10增加了栅压自举开关采样阶段的可靠性,在Vin较大时M6栅源电压不够开启的情况下,M9仍能导通使得节点f等于Vin,而M10可减小M11的栅漏,源漏电压保证可靠。因节点c电压采样阶段大于Vdd,为保证M8的衬底与源极的PN结始终反偏,M8衬底需要接源端。

图2 传统栅压自举采样开关

传统栅压自举采样开关的3个电容占据了很大面积。分析传统开关,因为NMOS管传递高电平会有一个阈值电压的损失,因而要使得M3传递高电平,M3需要获得大于Vdd+Vthn的栅压,通过电容C1、C2充满电后的电荷守恒原理可以实现。

通过如图3的改进可使用一个电容实现栅压自举开关功能,clk为高电平时,改进式栅压自举开关充分利用节点c的低电平使得M2导通,Vdd无损加在C1上极板,下级板跟随地,其他工作状态与传统栅压自举开关相同,而其对面积的节省是显而易见的。节点a在采样阶段超过电源电压Vdd,为了保证M2衬底始终反偏,M2衬底不能接在Vdd上而需要接在最高电平上,可增加M11、M12管实现。在保持阶段clk为低电平,M11打开,M2的衬底通过M11接到Vdd,而采样阶段clk为高电平,M12打开使得M2衬底与节点a相连,如此则保证了M2衬底始终反偏。

4 全差分运算放大器的设计

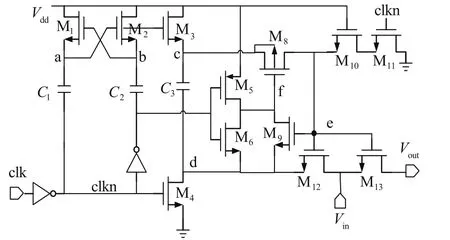

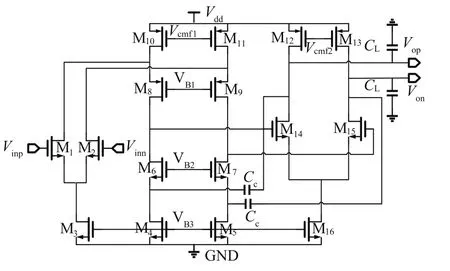

高速、高精度流水线型ADC采样保持电路的运算放大器需要有高开环增益,大单位增益带宽、高共模抑制比,宽输入输出摆幅以及足够的相位裕度保持稳定。本文采用如图4所示的两级结构提高运放增益,获得较大的输出摆幅,采用共源共栅密勒补偿,使用较小的电容即可获得较为理想的补偿效果,并采用开关共模反馈稳定共模工作点。

图3 改进式栅压自举采样开关

图4 带共源共栅密勒补偿的两级运放

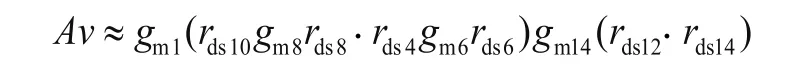

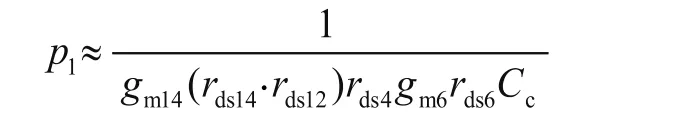

运算放大器的第一级为折叠式共源共栅放大,提高了输入摆幅,由于同等条件下NMOS管具有更大的迁移率,即可获得更大的跨导,因而采用了NMOS差分对作为输入级。第二级采用共源放大,增益提高了一个本征增益大小。对运放做小信号分析,可得的低频增益大小为:

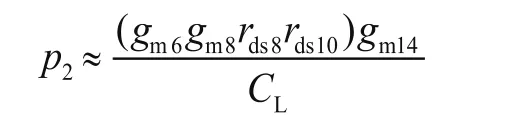

运放主极点为:

次主极点为:

与传统密勒补偿相比,共源共栅密勒补偿具有相同的低频增益及主极点,但其次主极点更远离主极点,因而增益带宽积较大。同时可获得的相位裕度更大,共源共栅密勒补偿不需要零点补偿,没有直接的高频馈通通路,改善了运放的电源抑制比。

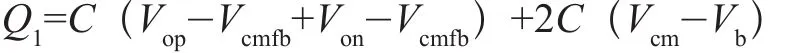

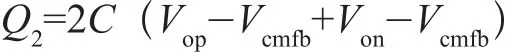

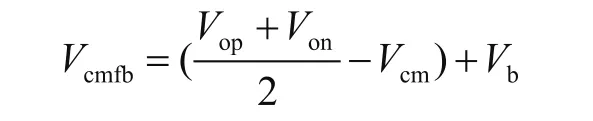

全差分运放两输出端都是高阻态,其共模电平不容易稳定,可采用共模反馈电路确定共模输出电平,稳定输出端信号。图5为本文采用的离散时间开关电容反馈电路,避免了阻性负载对运放增益的影响,减小了对运放输出摆幅的限制,且不消耗静态直流功耗。其工作原理为:

clk2为高电平时共模电荷

clk1为高电平时共模电荷

根据电荷守恒定律Q1=Q2,最终可得共模反馈电压:

图5 开关电容共模反馈电路

5 仿真分析

本文采用CSMC 0.18 μm工艺,1.8 V电源工作电压,使用Spectre仿真并结合Matlab分析采样保持电路的动态特性。

采样保持电路中运算放大器的频率响应如图6所示,可以看出在负载为1 pF时,其低频增益为92.21 dB,单位增益带宽为648.6 M,相位裕度57.3°,满足8位100 MSPS的要求。

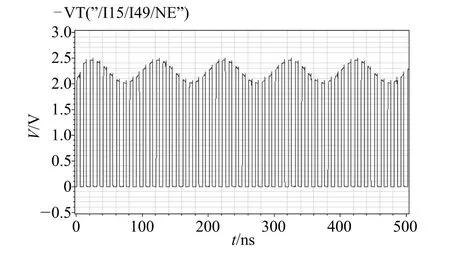

改进后的栅压自举开关的瞬态仿真如图7所示,栅压随着输入的变化而变化,而栅源电压差值近乎不变,因而其导通电阻相对保持不变,降低了非线性失真。

图8所示为正常工作时整体采样保持电路对频率为1M正弦波的零阶保持波形,可以看出输出信号能较好地跟随输入,运放较大摆率使得输出信号建立较好,运放57.3°的相位裕度使得输出过冲较小,可达到1 V的电压摆幅。

图6 全差分运放频率响应

图7 栅压自举开关瞬态仿真波形

图8 采样保持电路零阶保持波形

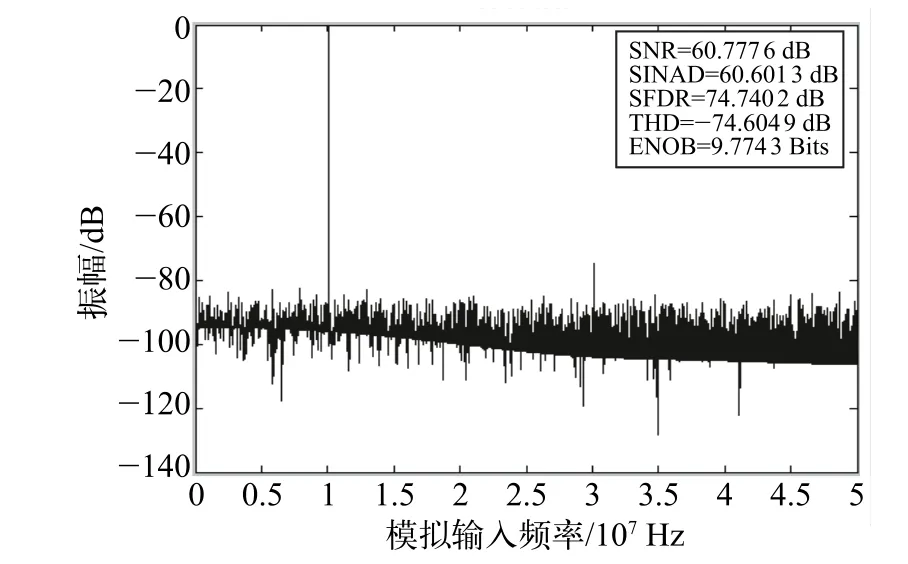

为了获得采样保持电路的动态特性,需要对输出信号进行快速傅里叶变换(FFT),然而为了防止频谱泄漏,需要信号频率与采样频率相干,输入10.034 179 687 5 M在100 M的采样频率下做4096点的快速傅里叶变换,如图9所示,可见其信噪纳比达60.6 dB,有效位数达9.7位,且总谐波失真低至-74.6 dB。

6 总结

本文基于CSMC 0.18 μm、1.8 V电源电压设计了一种应用于流水线ADC的采样保持电路,使用共源共栅密勒补偿运放及改进型栅压自举采样开关,实现了74.74 dB的SFDR,满足8位100 M采样频率流水线ADC的要求。

图9 采样保持电路的FFT频谱图

[1] 李锋,黄世震,林伟. 一种用于流水线ADC采样保持电路的设计[J]. 电子器件,2010, 33(2)∶ 170-173.

[2] 彭云峰,严伟,陈华,等. 一种新型高线性度MOS 采样开关[J]. 微电子学,2006, 36(6)∶ 774-778.

[3] 尹浩,陈必江,李靖,等. 适用于全差分运算放大器的两级共模反馈结构[J]. 微电子学,2011, 41(2)∶ 172-175.

[4] 毕查德·拉扎维. 模拟CMOS集成电路设计[M]. 西安:西安电子科技大学出版社,2002.

[5] Hasan-Sagha M, Jalali M. Very high speed and low voltage open-loop dual edge triggered sample and hold circuit in 0.18 μm CMOS technology [C]. IEEE International Conference on Semiconductor Electronics(ICSE).Kuala, Lumpur∶ IEEE, 2012∶ 645-648.

[6] Mohammed M, Kawar S, Abugharbieh K. Methodology for designing and verifying switched capacitor sample and hold circuitsused in data converters [J]. IET Circuits,Devices and Systems, 2014, 8(4)∶ 252-262.

[7] Dinc H, Allen P E. A 1.2 GS/s double-switching CMOS THA with 62 dB THD [J]. IEEE Journal of Solid-State Circuits, 2009, 44(3)∶ 848-861.