晶圆级传输线脉冲测试方法

2015-12-05邹巧云姜汝栋

邹巧云,姜汝栋

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 前言

1985年由Maloney T J等提出了传输线脉冲(TLP:Transmission Line Pulse)的测试方法,并在随后几年中得到了不断的发展。由于TLP测试方法可以准确地测量失效发生时的脉冲电压、脉冲电流,目前其作为ESD测试法的替代方法,已经成为电路设计工程师研究ESD保护结构的特性、进行ESD设计的重要依据。随着集成电路晶圆级测试技术的发展,早些年基于封装级的测试也逐渐向晶圆级转移。而对于ESD设计的工程师来说,如果能从晶圆级获得ESD保护结构的TLP测试结果,不仅降低了设计成本,同时也缩短了设计周期。

本文从测试原理以及测试流程出发,针对测试线路的搭建、设备的校核、被测结构的处置等方面探究晶圆级TLP的测试方法。作者结合实际案例,介绍晶圆级TLP测试过程中应力条件设置的主要环节。

2 基本原理

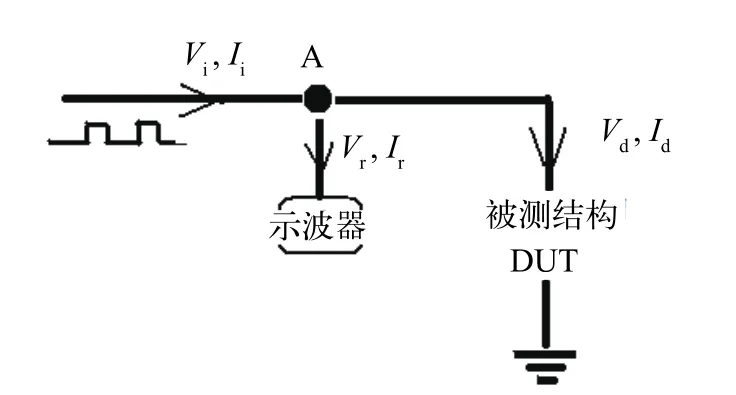

TLP测试是把方波测试脉冲加到待测ESD保护结构两端,通过示波器电压探棒、电流探棒采集传输线上反射回来的电压和电流,经过电路结构的节点分析法以及回路分析法推算得到每个方波脉冲应力下被测结构两端的电压以及流过其中的电流。

经简化的测试线路图如图1所示,图中A点为分析节点。设施加的输入脉冲电压、脉冲电流分别为Vi、Ii,示波器采集到反射电压、反射电流分别为Vr、Ir,被测结构两端电压及流过的电流分别为Vd、Id。

图1 测试线路图

当某个方波脉冲电压通过传输线施加到被测结构两端时,入射网络阻抗,反射网络阻抗,被测结构的等效阻抗。

由于入射网络与反射网络的结构不变仅信号传输方向发生变化,可得:

再从分析点A处电压,由基尔霍夫电压定律、基尔霍夫电流定律[1]分别可得:

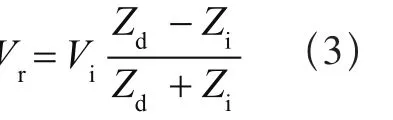

示波器采集到的反射电压值

由式(3)代入式(2)可得:

被测节后两端电压:

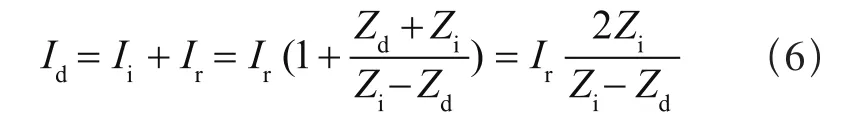

同理由式(4)代入式(1)可得:

由式(2)等效可得

由于方波脉冲电压幅度Vi应为测试时已知量值,示波器采集的反射电压值Vr、电流值Ir为可读值,测试系统的输入阻抗也是系统设计保证的固定值,因此分别结合式(7)、式(6)、式(5)可知:在某个方波脉冲测试信号输入后,通过对反射脉冲的电压、电流进行计算,被测结构的等效电阻Zd、流过被测结构的电流Id、被测结构两端电压Vd均为可得量值。如果连续以固定步进方式递增方波脉冲信号的幅值,相应地可以得到被测结构的电流-电压曲线(I-V曲线),即被测结构的动态特性分析曲线。

3 设备要求

3.1 必备硬件要求

由于晶圆级测试的被测结构存在不可随意移动、测试接触点相对固定的特点,因此晶圆级TLP测试系统除了具备封装级测试系统所涵盖的脉冲信号产生与控制系统、反射波测量示波器、TLP控制盒、传输线等仪器外,还需具备晶圆固定探针台、三坐标可调节探针座、信号接触针、地针等必备设施。

从本文第二部分的推导过程得知,当TLP测试系统的等效输入阻抗(Zi)作为已知量,通过反射脉冲的电压、电流推算被测结构(DUT)两端电压及流过其电流时,Zi决定着最终描绘的I-V特性曲线是否准确、有效。而作为TLP测试系统的用户,可能改变Zi的两大因素是改变传输线的长度,或者损害传输线的屏蔽性致使引入外界的干扰信号。因此,在一般测试情况下,应准确选用不同测试模式匹配的传输线,同时应在使用前检查传输线是否完好无损。

3.2 测试线路搭建要求

晶圆级TLP测试线路搭建的关键点是同轴传输线与信号接触针、地针的连接工作。图2是标准的时域延时反射交叠测试模式(TDRO)的连接示意图,从图中可以发现通过信号针将方波脉冲信号施加到晶圆上的某一个被测结构(DUT)的测试端,而DUT的另一端则是由地针经过同轴传输线的外层金属连接至地。

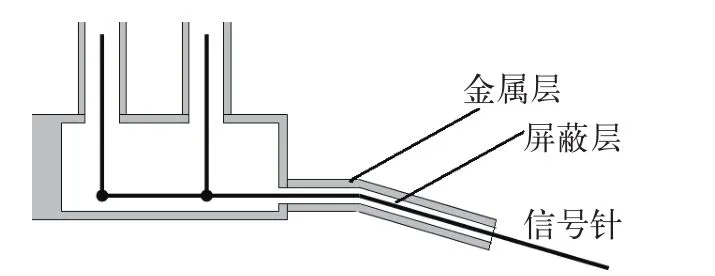

信号针、地针仅从外观上不易区分,实际测试工作中应注意观察两者的内在结构。地针为实心金属针,直接与同轴传输线端口处的金属相连至地;而信号针的结构相对复杂(如图3所示),其通过屏蔽层与传输线外层金属即地隔离,确保方波脉冲信号有效地施加至DUT端。

由于晶圆级TLP测试过程中,信号针、地针需要根据DUT在晶圆上的分布情况作精微调整,因此在开始测试前,两针的位置需要移动,所以连接两针的金属传输线是具有一定柔韧度的固定长度的软线。当然,长度固定的前提下,在连接软金属传输线时还应考虑探针调节方向不具备任意性,此操作关键点需在实际测试工作中积累经验。

图2 时域延时反射交叠测试模式连接示意图

图3 信号针结构

4 测试流程

4.1 测试系统校准

结合本文第二部分的推导过程以及本文3.1节的阐述,我们清楚地知道TLP测试系统的状态决定了最终获得的被测结构的I-V特性曲线准确与否。当完成测试线路的连接工作后,是否已经具备测试状态,需要通过7个校准步骤进行验证:晶圆级后端线路不连接情况下开路校准(Zi=∞)、短路校准(Zi=0)、线性电阻校准(Zi=R)、齐纳二极管校准、晶圆级后端线路连接情况下的开短路校准等。当7个校准步骤全部完成并且系统显示校准通过后,则开始进行下一步处置DUT的工作。

如果示波器、电压探棒、电流探棒、衰减器与TLP脉冲发生控制系统、TLP控制盒的连接并没有发生改变,并且测试系统长期处于工作状态,周围温湿度坏境也未发生变化时,第1~5步的校准步骤无需每次进行。

4.2 被测结构(DUT)处置

进行测试前,首先需确保晶圆被无损伤地固定在一个水平面上,根据信号针、地针所在位置对晶圆的水平位置进行适当调整。其次在放大20~50倍的条件下,对晶圆表面进行检查,防止碎屑、尘埃、颗粒物等沾污以及表面划伤、金属裸露等情况对TLP测试结果造成影响。根据晶圆上被测结构(DUT)的位置分布,调整晶圆的水平位置或者信号、地两针的三轴位置,使得两针准确接触到DUT两端。为了防止误扎针、扎深针给测试结果带来影响,扎针时应尽可能在5倍以上显微镜下进行。测试结束后,应分别抬起两针或者降低晶圆的高度,防止切换下一个DUT时造成晶圆划伤。

4.3 测试程序或条件设置

描绘被测结构的特性曲线通常是一个探索的过程,即设计师在不清楚其开启电压、二次击穿电压的情况下需要通过TLP测试手段获得这些关键参数甚至是全动态的I-V特性曲线。这种情况下,如果方波脉冲之间的步距过疏会造成关键参数遗漏或者不精确;而步距过密则带来TLP测试时间无限制延长、增加测试成本。在实际测试工作中,合理地设置方波脉冲的步距,不仅能给设计工作提供指导性帮助,同时也能减少不必要的时间浪费。下面以具有snapback特性的齐纳二极管为例,主要介绍测试工程师在实际工作中兼顾效率与结果两个因素的前提下设置测试条件。

首先,通过经验的积累以及对各种结构的研究,测试工程师应掌握被测结构(DUT)的大致特性曲线,了解其主要变化趋势。

其次,对于测试条件的设置,基本可分为“取样摸底”和“测、设同步”两种方法。

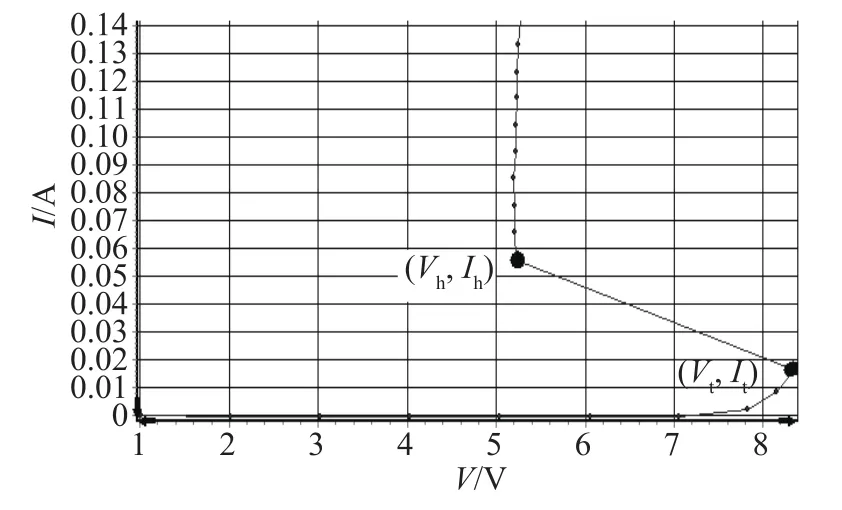

如果相同结构的DUT不止一个时,可以选择其中一个作为摸底样品,试探性地放大测试的步距,只需观察到开启电压、二次击穿电压大致范围即可。图4可见通过方波脉冲幅值电压设置:1~7 V,step=1 V;7~8.6 V,step=0.8 V;当方波脉冲幅值递增至8.6 V左右,DUT开启(Vt,It),随后便维持在5.3 V左右。图5是在得知图4中开启、维持特性的大致范围后,重新选取相同结构的一个DUT进行TLP测试的结果。从该图中可以发现,在未接近开启电压点,step由1 V变成2 V(缩短前期无关紧要的时间),而在开启电压附近,step从0.8 V变成0.1 V(更加精准地获得开启电压值)。

如果DUT独一无二,则采用边测边设置的方法。测试时不应一次性设置好所有步进(step)电压,工程师应仔细观察I-V曲线的变化趋势,当I-V略呈“抬头趋势”时,应逐步降低step,直至DUT完全开启后维持在“保持状态”;根据保持状态的相对稳定性,再适当增加step;工程师继续观察I-V曲线,当维持电压增大趋势明显时,应再次降低step直至DUT发生二次击穿后失效。

图4 样品测试结果

图5 样品TLP测试结果

4.4 测试结果的判断分析

由于误操作或系统性故障等偶然因素造成TLP测试数据偏差时,测试工程师可从所描绘的曲线中观察到偏差程度并根据理论分析对测试数据予以校正。作者举下例示范。

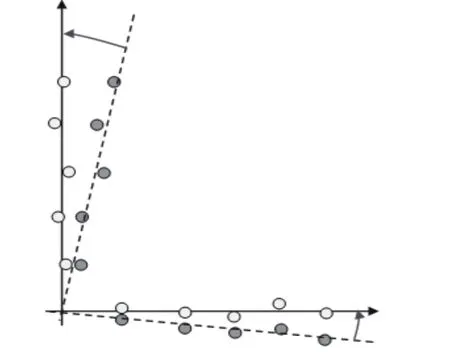

齐纳二极管结构的I-V曲线呈现出开启前有“等效负电阻”特性,终止试验后重新校准测试线路的开路状态和短路状态,并分别在两种状态下连续递增方波脉冲幅值,绘制出如图6的两条曲线。从理论角度分析,当线路处于开路状态下时,流过DUT的电流及其两端电压应遵循Id=0,Vd=Vi;相应地,线路处于短路状态时, Id=Ii,Vd=0。而图6中呈现出的曲线显然表现出测试过程异常,但是异常情况又呈现出一定的规律性。再将理论值与实测值对比,不难发现实际测得的异常数据与理论数据存在相位偏差,通过旋转坐标轴便可纠偏,如图7所示。

5 小结

本文通过推导TLP测试的基本原理,结合系统校准、线路搭建、结果判断关键步骤总结了晶圆级TLP测试的基本方法和测试流程。通过实际案例,介绍了如何在未知开启电压参数或二次击穿电压参数的条件下,通过合理地设置测试条件,以达到快而精准地描绘器件I-V曲线的方法,对于实际测试工作具有一定参考价值。

图6 开路与短路状态下连续递增方波脉冲幅值

图7 旋转坐标轴

实际测试工作中,除了掌握本文介绍的基本方法和流程外,实践经验的积累以及数据分析更加重要。另外,关于测试环境(如温度、光照等)因素对测试结果是否有影响及影响程度,仍需要进一步的分析与研究。

[1] 周守昌. 电路原理(上册)[M]. 北京:高等教育出版社,2004.

[2] 罗宏伟,师谦. 集成电路抗ESD设计中的TLP测试技术[J].电子产品可靠性与环境试验,2003.4.

[3] Maloney T J, Khurana N. Transmission Line Pulsing Techniques for Circuit Modeling of ESD Phenomena [A].7th EOS/ESD Symposium [C]. 1985. 49-54.