基于AMBA总线的3DES算法IP核的设计与实现

2015-12-05屈凌翔

王 澧,张 玲,屈凌翔

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

互联网技术蓬勃发展,给人们的工作生活带来了极大方便。但大量敏感信息通过公共网络进行传递和交换的同时也产生了越来越大的信息安全隐患。采用加密技术可以对传输的信息进行加密,使信息以密文的形式进行传输,防止信息泄漏,加强了信息的安全性和完整性。加密技术可以分成软件加密和硬件加密。软件加密通过运行加密软件的形式实现数据加密,硬件加密则是通过专门的硬件设备来实现的。使用软件加密会占用大量系统资源,通常速度比较慢,同时明文和密钥必须预存在磁盘中,因此并不安全;而采用硬件加密就可以避免这些问题。特别是随着半导体制造工艺进入超深亚微米时代,采用硬件形式实现加密算法逐渐成为主流。本文设计的3DES模块就是我们开发的SoC设计平台中的一个IP核。

AMBA总线是ARM公司提出的一种开放性片上总线标准,具有高速、低功耗的特点,广泛地应用于系统芯片设计中,实际上已经逐渐成为业界公认的总线标准。目前使用最多的是AHB-APB架构,AHB总线负责连接CPU、DMA控制器、片上存储器、高速接口或其他高带宽组件,而APB总线则用来连接系统低速外设。AHB与APB之间通过总线桥相连,以减少系统总线的负载。

2 加密算法原理

2.1 DES算法

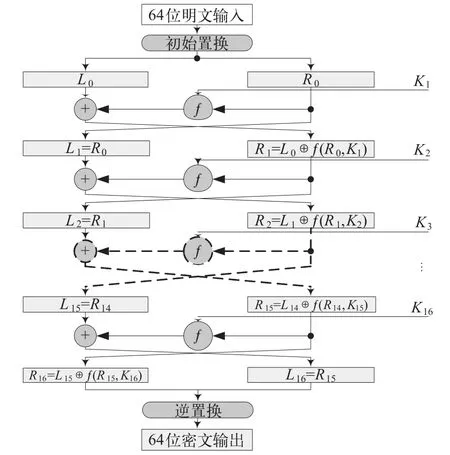

DES算法从1977年公布至今已有30多年的历史,但目前还没有实用的破解DES的方法,因此在信息安全领域仍有广泛的应用。DES算法是一种典型的分组加密算法,64位明文从算法的一端输入,64位密文从另外一端输出;加、解密过程中使用同一种算法;使用的密钥长度为56位;进行16轮的重复迭代与置换操作,最终获得64位的输出。

图1 DES算法框图

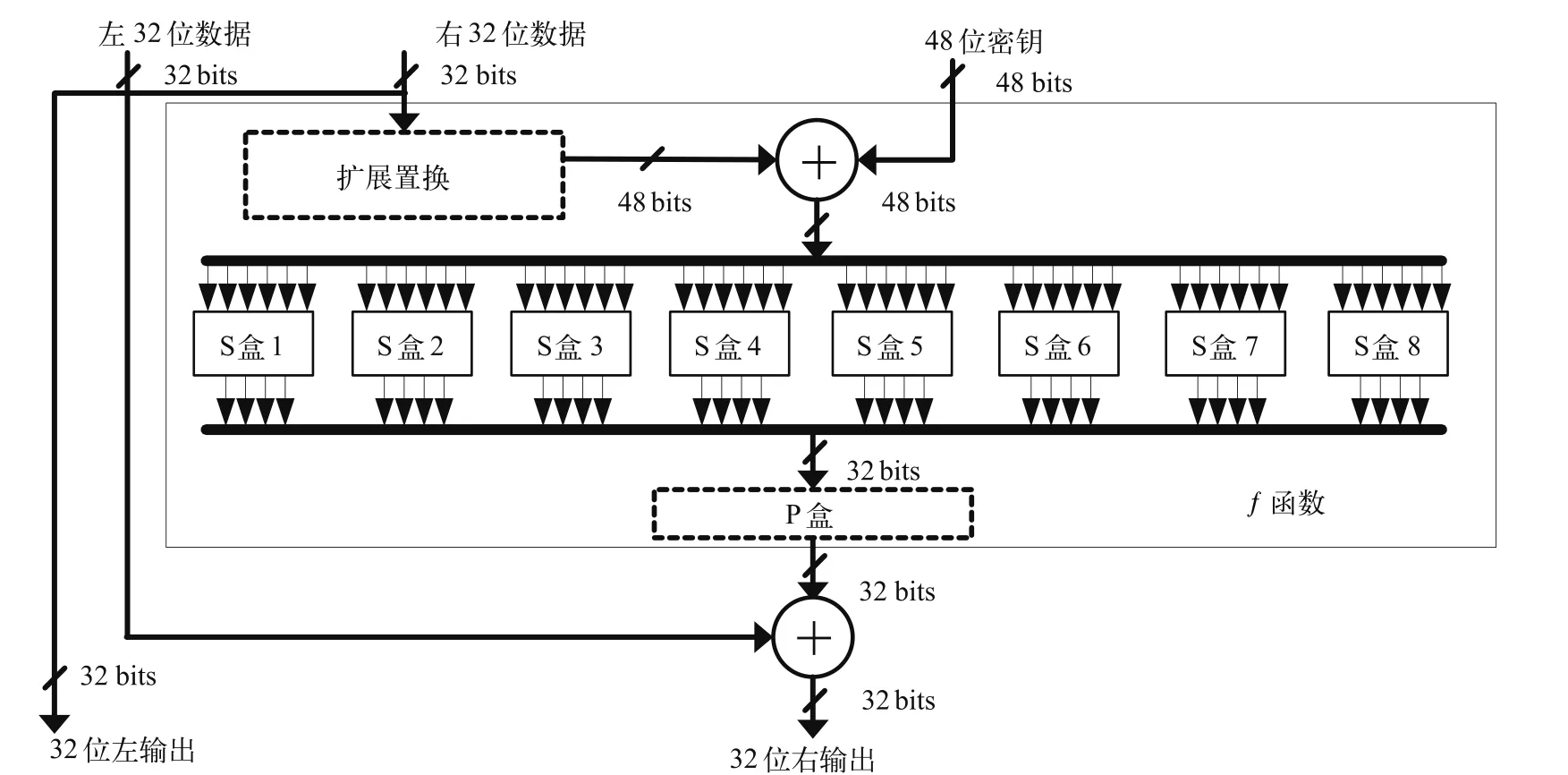

DES算法如图1所示,每次输入64位明文,首先经过一个初始置换操作,通过16轮的加密运算,再通过初始置换的逆变换得到64位密文。在每一轮运算中,右边32位数据和KEY一起传送给函数f,运算的结果再和左边32位数据进行异或操作。在f函数中进行以下运算:将32位的输入数据经过扩展置换为48位,接着和本轮循环对应的密钥进行异或运算,得到的结果再经过S盒运算产生32位输出,最后通过P盒置换产生最后的输出。其中S盒运算是整个DES算法中唯一的非线性部分,是实现混乱和扩散的关键步骤。

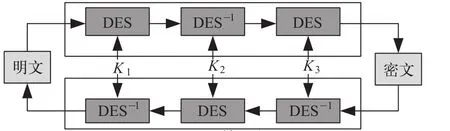

2.2 3DES算法

DES算法由于密钥长度太短,不能抵抗穷举搜索攻击。人们认识到随着计算能力的增强,必须相应地增加密钥长度。3DES即三重DES算法,是DES算法的一个更加安全的变形。3DES算法是在普通DES模块的基础上,进行三次循环加密。3DES算法的运算框图如图2所示。

3DES采用加密-解密-加密序列对明文进行三次加密操作产生密文,使用K1、K2、K33个56位的密钥。为了更高的安全性,3个密钥应该互不相同,相当于168位的密钥,可以有效地对抗穷举法破解。另外,由于使用DES算法的软硬件在各个领域已经获得广泛的使用,因而升级到3DES比更换新算法的代价更小,风险更低。3DES算法虽然作为一种过渡的数据加密标准,但还是在各行业获得了广泛的应用。

图2 3DES算法框图

3 电路设计

3DES密码算法需要对64位明文或密文依次进行三次DES加密或解密,得到64位密文或明文。它可以由3个DES模块级联,形成流水线结构;也可以采用单个DES模块,控制DES模块顺序进行三次加密或解密。第一种结构占用资源较多,但3个DES模块并行工作,速度快;第二种结构占用较少的逻辑资源,但速度较慢。本文采用的是第二种结构,可以通过用时间换空间,大大缩小芯片面积,同时还可以保证IP核的可读性与通用性。

3.1 总体方案

3DES算法IP核的设计框图如图3所示。考虑到整个项目中数据位宽、传输特点的实际情况,定义模块数据和地址总线为32位,利用2个32位数据寄存器完成64位数据的组合并进行加、解密。因为仅使用一个AHB主机,接口采用AMBA3 AHB Lite协议。

图3 IP核顶层信号图

电路主要分为4个模块,包括AHB总线接口模块、寄存器模块、状态机控制模块和数据处理模块。

3.2 总线接口设计

本文所设计的IP核在系统中是作为AHB总线的从机模块。为了保证该IP核与AHB总线之间信号传输正确,专门设计了AHB总线接口模块来实现AHB总线从机接口时序。使得AHB主机信号可以控制模块运行,并在模块与AHB总线之间正确地传输数据。

最终CPU可以通过AHB总线接口模块访问控制寄存器,配置3DES模块的加密或解密模式;完成加密或解密任务后发出中断请求信号;通过读状态寄存器获得状态信息。

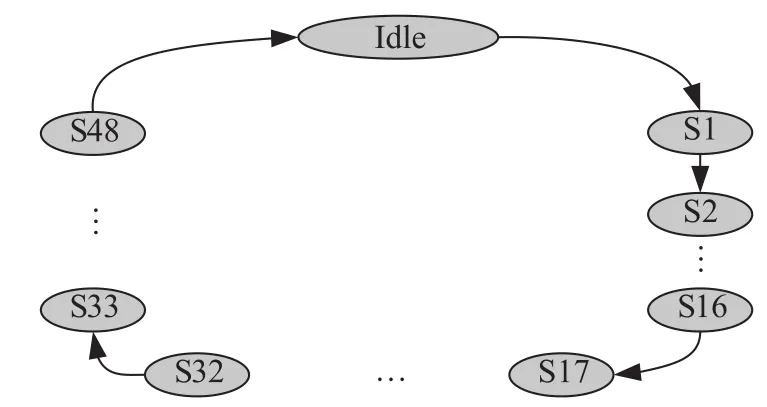

3.3 状态机设计

状态机是整个IP核设计的控制核心,负责组合逻辑的判断,控制数据通路的传输。单次DES算法需要运算16轮,因而3DES算法需要运算48轮,每一轮的结果将会输入到下一轮的运算中,所以算法的运算过程中存在着48个状态。设置一个6位的计数器,对3DES算法下的48轮迭代进行统计,根据计数器的当前数值进行状态的跳转,从而对运算过程进行控制。当3DES算法进入第l轮迭代时,选择Key1作为密钥输入,对64位输入数据进行初始置换,进入DES加密流程;当3DES算法进入到第l6轮迭代时,对64位结果进行32位左右互换并进行逆置换,得到64位输出数据;第l7轮迭代时,选择Key2作为密钥输入,将64位输入进行初始置换,再次进入DES加密流程;第32轮迭代时,对64位数据进行32位左右互换并进行逆置换,得到64位输出数据;第33轮迭代时,选择Key3作为密钥生成模块的输入,对64位输入进行初始置换,第三次进入DES加密流程;最后一轮迭代时,将64位结果进行32位左右交换,最后通过逆置换输出最终结果,同时产生完成信号输出到模块外部。

图4 状态转移图

3.4 单轮运算模块设计

单轮运算模块就是执行单次DES加/解密操作的运算部件。如图5所示,输入的右32位数据经过扩展置换后变为48位;并与压缩置换生成的48位密钥进行异或运算。结果分别输入到8个S盒中。每个S盒6位输入,4位输出。32位S盒输出再经过P盒置换后输出32位的f函数运算结果,该结果与32位的左明文输入进行异或运算就可以得到单轮DES的结果。

3.5 S盒的实现

3DES算法的安全保密性主要体现在16轮的迭代运算中,主要依靠非线性的、不可逆的S盒(Substitution Box)替换实现运算过程中的混乱(Confusion)操作,所以S盒操作是3DES算法成败的关键,S盒设计的优劣将影响整个算法性能。

在硬件实现时,S盒设计的好坏是影响算法速度的关键因素。设计时存在优先考虑运算速度还是占用资源的问题,要根据设计需求来选择。使用Verilog硬件描述语言建立S盒的电路模型,通常有两种方法:一种是采用Verilog中的CASE语句,用纯组合逻辑来实现;另外一种是利用ROM进行查表的方式来实现。

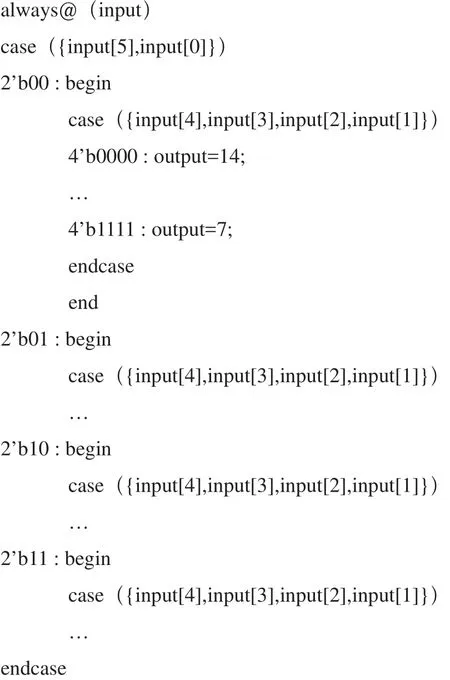

我们在实现S盒时采用的是第一种方法,即采用双层嵌套的CASE选择语句对电路进行描述。S盒电路共有8个,每一个都有6位的输入、4位的输出,且这8个S盒的功能各不相同。设计时,每一个S盒的输入为input[5:0],输出为output[3:0]。为了降低资源占用,通过双层嵌套,使用4输入选择器而不是6输入选择器。设计时外层使用输入数据的input[0]与input[5]作为外层case的控制变量,input[1]、input[2]、input[3]、input[4]作为内层 case的控制变量,该设计方法可以在保证数据运算能力的前提下大大降低占用资源,相对于6个变量的CASE语句可以减少占用资源约50%。

下面列出了S盒1的部分Verilog代码:

其余7个S盒的设计与S盒1的设计类似。

图5 单轮运算示意图

4 功能验证与设计实现

4.1 功能验证

使用Synopsys公司的仿真工具VCS建立环境,对设计的IP核进行功能验证。将仿真结果与按照3DES标准计算的结果相比较,从而验证3DES算法IP核加、解密功能操作的正确性。

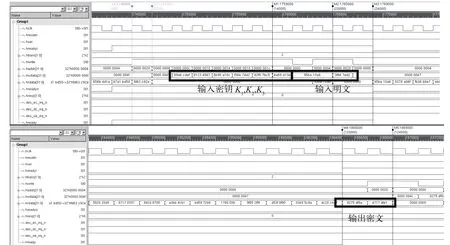

图6为3DES算法下进行的加密操作。上电复位后,向寄存器写入控制信号,然后依次写入密钥K1、K2、K3,最后写入明文。启动加密操作,读出加密后的密文。

图6 3DES算法加密操作仿真图

输入密钥为:K1:64’h0123456789abcdef

K2:64’hf36e74d28b95a10c

K3:64’h4a69d13e82f07bc5

输入明文为:64’h3f847ed295ba10a6

输出密文为:64’h4717dfe18275df9a

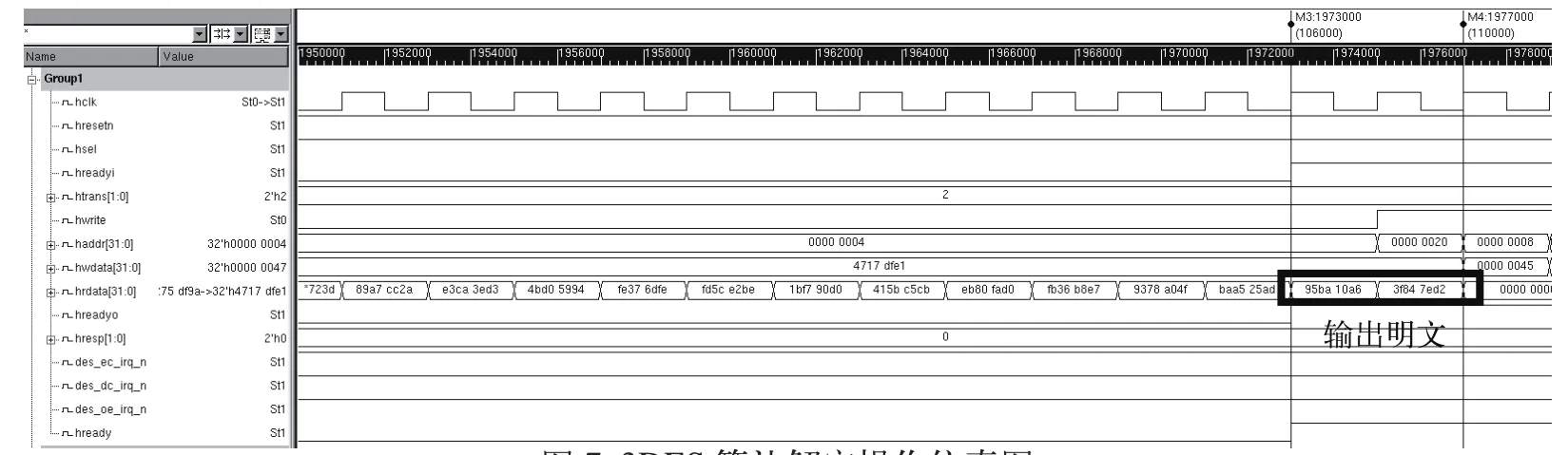

图7为3DES算法下进行的解密操作。复位后,配置寄存器控制信号,对上述之前的密文进行解密,依次写入解密密钥K3、K2、K1。启动解密操作,然后读出解密后的明文。

输入密钥为:K1:64’h0123456789abcdef

K2:64’hf36e74d28b95a10c

K3:64’h4a69d13e82f07bc5

输入密文为:64’h4717dfe18275df9a

输出明文为:64’h3f847ed295ba10a6

以上的仿真结果证明了3DES算法下模块加/解密功能的正确性。根据3DES加密测试标准数据可知,以上仿真数据与测试数据完全一致,从而证明了3DES算法IP核设计的正确性。

图7 3DES算法解密操作仿真图

4.2 设计综合与时序仿真

在通过功能验证后,使用TSMC(台积电)的65 nm工艺库进行逻辑综合,生成门级网表。综合后面积为22 661 μm2。接着使用Formality工具对综合结果进行形式验证,检查综合后网表与RTL代码的一致性。然后使用Prime Time工具对网表进行时序验证,结果表明在500 MHz频率下建立时间及保持时间均能满足时序要求。通过这些验证之后,对网表进行布局布线,生成电路版图,并提取寄生参数,生成SDF延时文件,进行后仿真。

5 结束语

对比现有的设计,该IP核在主频、面积、功耗方面都有一定的优势,目前已成功运用于一款DSP内。流片后最终芯片测试结果显示,模块可以稳定工作在500 MHz,加、解密转换速率可以达到615 Mbits/s,达到了预期的设计要求,可以实现对片上系统通信数据的实时加密解密。

[1] 戴紫彬,孙万忠,张永福. DES算法IP核设计[J]. 半导体技术,2003,28(5):58-59.

[2] 晏福平,盛利元,简远鸣. 基于DSP的3DES加密系统的设计与实现[J]. 计算机测量与控制,2009, 17(7):1390-1392.