轮对磨耗检测中多通道DSP数据接口设计

2015-12-02

(杭州电子科技大学生命信息与仪器工程学院,浙江 杭州310018)

0 引 言

轮对是铁路车辆中的重要走行部件,其状态是影响运行安全的重要因素之一[1]。随着列车运行速度的提高,研究高效率的轮对磨耗在线检测方法具有重要的应用价值[2]。基于电荷耦合器件(Chargecoupled Device,CCD)成像技术的轮对磨耗在线检测是国内外研究的重点,目前国内的轮对磨耗在线检测技术只能适应低速的检测需求,如何提高图像处理速度以适应在线检测需求是亟待解决的关键问题之一[2-3]。DSP技术在图像处理领域的发展为基于DSP的磨耗在线检测的实现提供了基础。近些年,国内一些研究机构在矿山绞车轮对检测中提出了DSP方案,也有在轨道表面磨耗检测系统中应用了DSP方案[3]。本文提出一种基于多通道DSP的轮对磨耗在线检测硬件系统的实现方案,对高速数据接口缓存进行详细分析和设计,并通过实验验证了设计系统的有效性。

1 基于FPGA+DSP的多通道轮对图像处理系统

多通道DSP 轮对磨耗检测系统示意图如图1所示,包括4通道图像采集单元、采集控制中心、以太网传输和图像处理单元4部分。采集控制中心在线获得4组采集单元的图像数据,通过以太网传输至图像处理单元进行预处理和参数计算[4]。

设计基于FPGA+DSP的4通道图像处理系统,每个通道对应一组图像采集单元的数据。采用FPGA实现图像数据的传输和分配,DSP 执行图像处理算法。系统包括1 片FPGA和4 片DSP。采集控制中心4组图像数据经以太网传入FPGA,FPGA实现和DSP 之间进行高速数据交互。每个DSP 自身外扩FLASH和DDR,用于存放各自的程序和数据,图像数据在DSP 中进行处理,处理后的数据经过FPGA和以太网输出到PC 存储以便进一步分析。

图1 多通道轮对磨耗检测图像处理系统示意图

2 系统硬件实现

多DSP 图像处理硬件系统设计中FPGA与DSP的数据通信是设计的关键,其中双向FIFO和EMIF接口的设计是难点,同时硬件电路如何设计制作也是需要解决的重要问题。

2.1 双向FIFO的实现

基于FPGA的传输模块需要完成基于以太网的图像数据收发,并实现与DSP的异步数据交互。异步FIFO 实现缓冲存储FPGA与DSP 之间的图像数据传输。系统通过设计一组由两个互为反向的FIFO组成单个通道来实现图像数据的双向传输,数据宽度为8位。采用FPGA的Block RAM 模块设计实现。

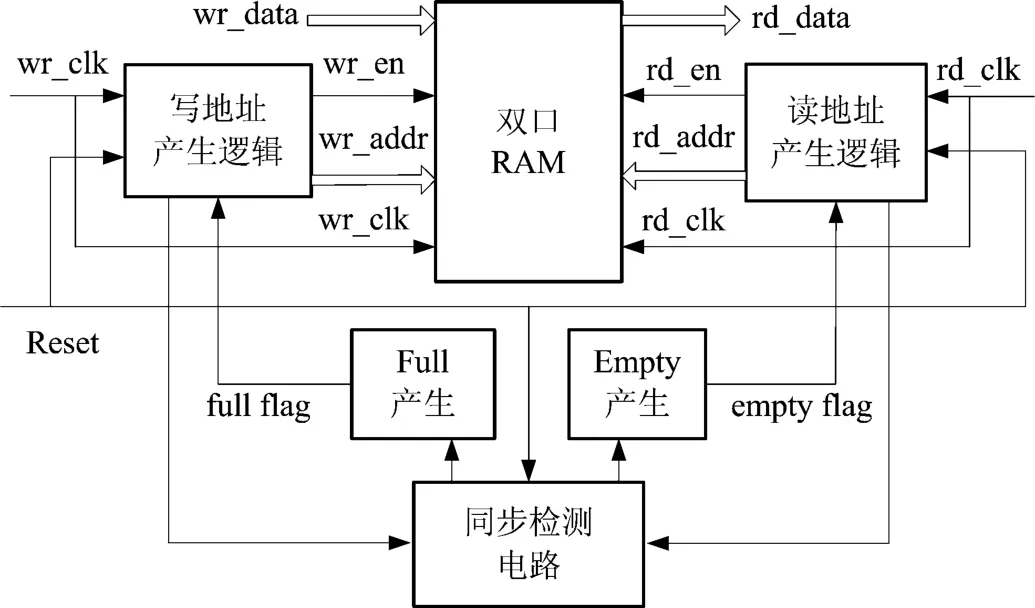

软FIFO 设计实现如图2所示,异步FIFO 由双口RAM、读/写地址产生逻辑、Full/Empty 标志产生模块组成。当写时钟脉冲(wr_clk)上升沿到来时,产生写逻辑地址(wr_addr),判断写信号有效,wr_en信号控制写数据到RAM中,当RAM 中数据写满时产生Full 标志;当读时钟脉冲(rd_clk)上升沿到来时,产生读逻辑地址(rd_addr),判断读信号有效,rd_en 信号控制从RAM 读数据,当RAM 中数据读空时产生Empty 标志。FIFO 读写控制逻辑都是在FPGA 内部实现。

图2 软FIFO 设计实现图

2.2 基于EMIF的轮对图像数据接口

为实现图像数据从FPGA 传输到DSP中,DSP 需要设计接口与FPGA的FIFO 相连,本文采用EMIF接口实现该功能。FPGA与DSP 采用异步方式连接,数据宽度设计为8位传输,在硬件设计时预留3位地址线和8位数据线。EMIF与FIFO 硬件连接如图3所示,EMIF 分别连接一个读FIFO和一个写FIFO,采用同一时钟信号(rd_clk=wd_clk=AECLKOUT),其中读写的使能信号分别为rd_en =!(/CE+/ARE),wd_en=!(/CE+/AWE)。

图3 EMIF与FIFO 硬件连接示意图

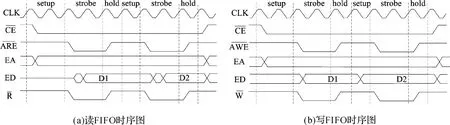

实现FPGA和DSP数据交互最核心的是EMIF 接口的时序设计。EMIF 异步接口的每个读/写周期分为SETUP(建立)、STROBE(触发)、HOLD(保持)3个阶段[5]。DSP 读/写FIFO时序如图4(a)、图4(b)所示,DSP 读写FIFO控制信号由FPGA 产生。

图4 异步EMIF 读/写FIFO时序图

在建立时间,CE 片选信号拉低,地址线EA 给出读/写数据的地址;触发时间,ARE/AWE 信号拉低,同时FPGA/DSP 在ED 信号线上传输数据;保持时间中ARE/AWE 信号将拉高,并在保持时间结束后,CE 信号拉高[6]。当读/写操作不能在外部器件的一个访问周期内完成时,EMIF 就会进行多个周期的操作,直到完成整个申请。

2.3 硬件电路的设计

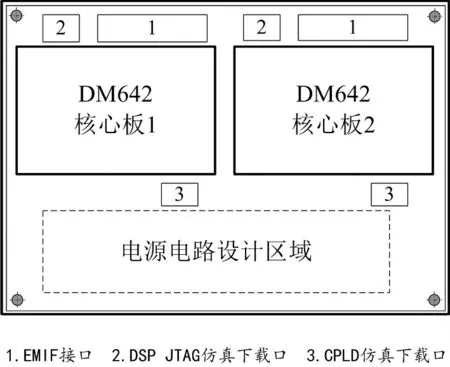

多通道系统的电路组成包括FPGA和DSP 两部分。其中FPGA 硬件采用了开发板;4通道的DSP 图像处理电路需要4片DM642 作为主芯片,各搭载DDR和FLASH 等外设电路,设计中采用DM642 最小系统核心板进行二次开发,自行设计和制作底板电路。每块底板上设计两块DM642 核心板,由两组构成4通道处理平台,底板结构如图5所示。DSP 硬件电路通过引出的EMIF 接口和FPGA 相连,组成完整的多通道轮对图像处理硬件系统。

图5 底板设计结构图

3 硬件系统测试

3.1 硬件系统仿真测试

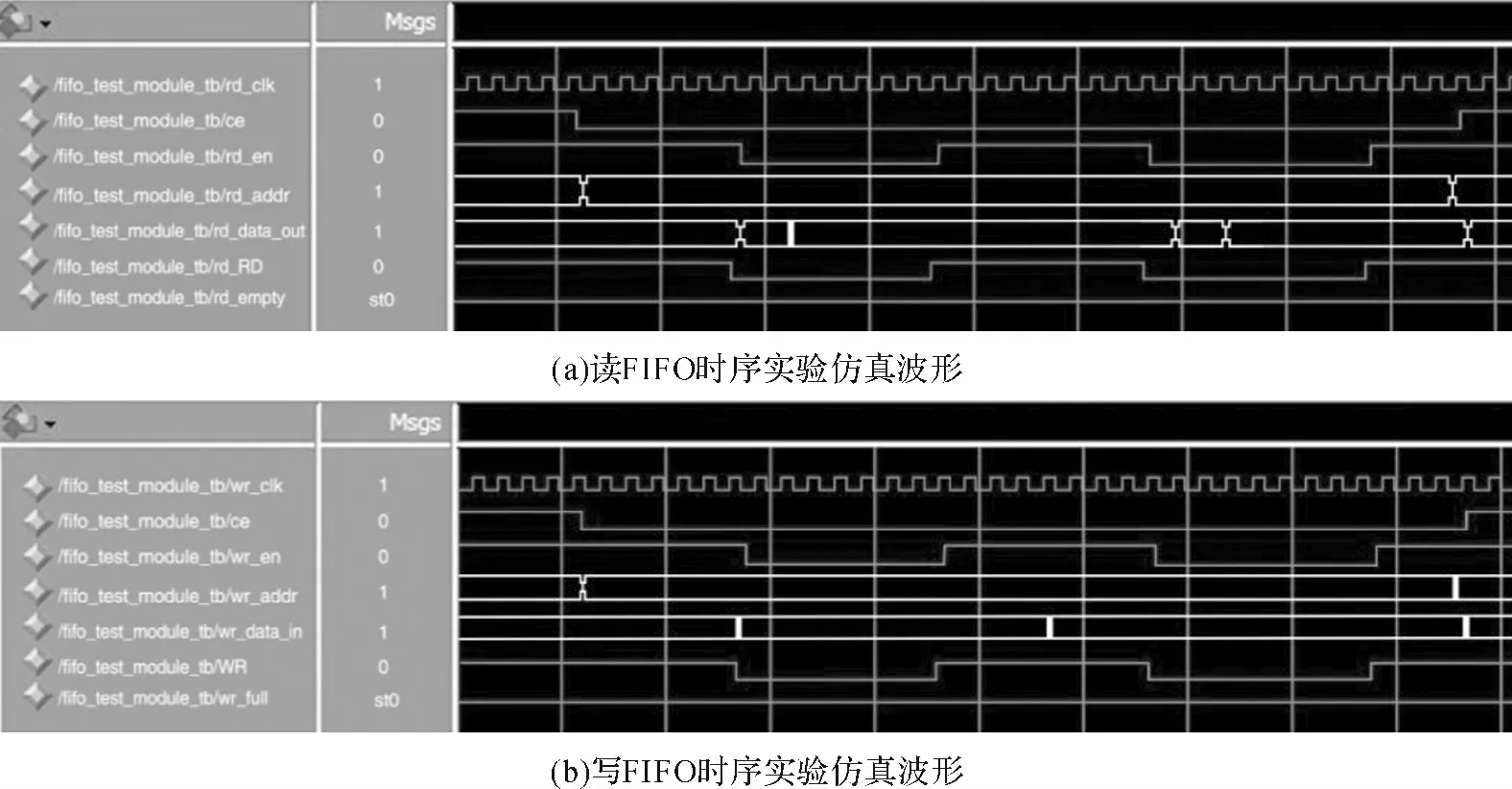

DSP与FPGA的数据交互接口是硬件系统设计中的重点,在设计过程中对该部分接口电路进行仿真测试。实验中使用Modelsim 软件进行仿真,图6(a)、图6(b)分别为对FIFO 进行读操作和写操作时的各引脚时序波形。从图6可以看出,CE 片选信号拉低时,地址信号给出读/写数据的地址;当ARE/AWE 信号拉低时,在ED 信号线上有数据传输。仿真结果与2.2 节中图4相符,结果表明硬件设计正确。

图6 读写FIFO时序仿真结果

3.2 系统图像数据传输测试

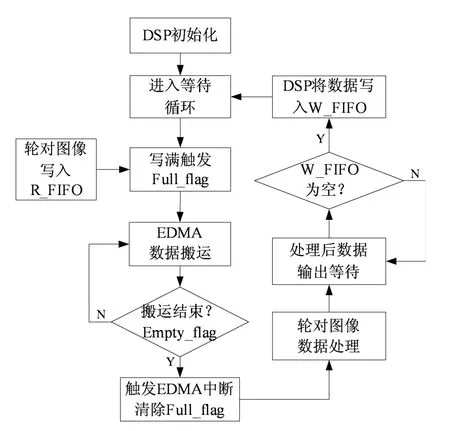

数据传输测试软件流程如图7所示。针对轮对图像数据能否在设计的硬件平台上正确传输进行验证。图7中R_FIFO为DSP 侧读取数据的缓存,W_FIFO为写数据缓存。轮对图像数据的传输以中断方式进行。

当图像数据完整写入R_FIFO中,产生Full_flag 触发中断;如果EDMA通道忙碌,则屏蔽中断,FPGA 通过定时器,以一定的时间间隔连续的向DSP 发送该触发信号,直到中断被响应;DSP 响应Full_flag 中断后便开始数据的搬运。当图像数据被完整的搬运出缓存,R_FIFO 已被读空,会产生Empty_flag标志触发EDMA;图像数据被传入CPU 后在数据通道中等待被传出,监测W_FIFO为空闲,DSP 将数据写入其中,同时退出本次循环,系统重新回到等待循环状态,等待继续下一幅图像数据的处理。

图7 数据传输测试软件流程图

实验将图像数据传入FPGA和DSP,设计中使用CCS 调试工具查看DSP 内存地址下的实际数据。测试使用了16组图像每组16幅图,结果显示均可以在DSP 内存段中得到正确的图像数据。实验结果表明轮对图像数据在本文所设计的硬件系统上得到正确的传输。

4 结束语

本文基于解决轮对磨耗在线检测的问题提出了FPGA+DSP的多通道图像处理的硬件实现方案。重点研究并完成了基于FPGA的双向FIFO 缓存和基于DSP EMIF的数据交互接口的设计,完成了硬件实物制作,并对关键设计进行了实验验证。实验结果表明轮对图像数据在设计系统上正确传输,为后期高效率处理轮对磨耗在线检测图像提供了硬件平台和实现基础。

[1]李剑.轮对动态检测系统应用[J].铁道车辆,2012,50(4):39-42.

[2]张渝.图像测量技术在轮对外形检测中的应用[D].成都:西南交通大学,2003:13-16.

[3]郭静涛,戴立新,王泽勇.轮对状态动态检测系统应用综述[J].铁道技术监督,2009,37(7):10-12.

[4]班韬.基于结构光成像的机车轮对磨耗参数在线检测技术研究[D].杭州:杭州电子科技大学,2010:17-19.

[5]宋宜良.基于FPGA和DSP的实时图像处理系统设计[D].大连:大连理工大学,2009:33-46.

[6]Texas Instruments.TMS320C6000 DSP External Memory Interface ReferenceGuide[EB/OL].[2008-04-01].http://www.ti.com/lit/ug/spru266e/spru266e.pdf.