重离子治癌加速器高速数据传输系统设计与实现

2015-12-01李桂花杨桂芹张志婧

杨 帆 李桂花 杨桂芹 张志婧

重离子治癌加速器高速数据传输系统设计与实现

杨 帆1,2李桂花2杨桂芹1张志婧1,2

1(兰州交通大学 兰州 730070)

2(中国科学院近代物理研究所 兰州 730000)

根据重离子治癌加速器的特点提出了新的一种数据传输方法,在FPGA上实现了DPSK (Differential Phase Shift Keying)调制解调,加入了奇偶校验、BCH编解码、扰码与帧同步系统来提高系统的可靠性,传输信道采用SFP光纤传输,提高了传输的速率,降低了设计成本。本文主要描述系统软硬件的设计和实现细节,重点分析了在传输过程中如何使用FPGA编程方法提高系统的可靠性和稳定性。该系统经过严格压力测试,做到百万次传输无误差,已在重离子治癌加速器现场实际使用,在加速器控制领域首次实现了FPGA结合光纤的DPSK调制解调高速数据传输,对同类系统有较好的借鉴参考作用。

重离子治癌加速器,数据传输,DPSK调制解调,相变点,FPGA

重离子治癌加速器是在兰州重离子加速器冷却存储环(Heavy Ion Research Facility in Lanzhou-Cooling Storage Ring, HIRFL-CSR)的基础上重建的一台专门用于医疗的同步加速器。重离子治癌同步加速器设计运行周期3.2−13.2 s,加速时间1.6 s。一个加速器装置的控制系统必须使束流加速过程完成。一般来说,它必须激发所有参与这个束流加速过程的设备,在正确的时间做正确的事情。加速器的动态参数决定了这些机器的时序要求。控制系统不但要完成非实时信息的通信,而且还要支持时间要求严格的实时信息的通信,在重离子治癌加速器设计中,时序系统的精度一般要求在微秒级,而且要求同步的设备多,输出到设备的波形数据时间间隔也在微秒级,另外为了监测电源波形及与同步时钟之间的相对时间关系,还要同步采集电源的波形信号,因此高速以太网(千兆以太网)是不能保证加速器控制的实时性。加速器运行数据组织软件将所有计算好的设备波形数据装载到执行部件,执行部件接收到来自加速器运行数据组织软件发出的同步触发事例后,经过要求的延时,将数据输出到设备,执行部件通常是自主研发的集成电路板,主要器件是FPGA和DSP,执行部件及其FPGA和DSP上的内置程序完成了响应同步事例后延时输出波形数据到设备的功能,为了保证输出数据的速度、精度和实时性,数据传输的速度必须在亚微秒级,并且数据传输中要严格保证数据的正确性。

目前,HIRFL-CSR的同步事例传输采用了400kHz光纤传输的基带信号,其带宽和可靠性都需要提升。因此,我们自主研发了基于PCI接口,以FPGA为核心器件的重离子治癌加速器高速数据传输控制板卡。如图1所示,系统采用通用SFP接口,该接口的传输速率最高可到125 MHz,并且为了使传输协议更加有针对性,整个系统更具灵活性,在板载FPGA中实现了全部传输协议及信号调制解调。根据实际需求与器件性能,采用100 MHz载波,10 MHz基带信号的DPSK (Differential Phase Shift Keying)调制解调。该系统已经用于加速器系统调试,经测试,百万次数据传输无误。

图1 重离子治癌加速器高速数据传输控制器及测试平台Fig.1 Controller and test platform of high-speed data transmission of the heavy ion therapy accelerator.

1 重离子治癌加速器高速数据传输系统硬件平台

图2 重离子治癌加速器高速数据传输系统硬件平台Fig.2 Hardware platform of the system of high-speed data transmission of the heavy ion therapy accelerator.

数据传输系统的平台为PCI+FPGA+光纤的结构,如图2所示。PCI接口用于实现服务器与数据传输系统间数据的下载与上传[1]。FPGA将收到的数据进行处理后进行DPSK调制输出,通过光纤传输到信号接收设备,信号接收设备载板的FPGA对收到的数据解调,针对不同的设备,对数据进一步分析并实现控制逻辑。款芯片成本合理,资源适中,同时它支持多路LVDS信号,提高了信号传输的带宽和可靠性[2]。利用编程语言来实现数据传输,其收发速率和帧格式很容易改动,而不需要更换任何设备和器件,便于系统的改进。传输信道采用Firecomms(爱尔兰)公司的EDL300T,它的传输带宽最高为125 Mbps,通用SFP接口的使用使系统更加稳定,并且该接口非常容易使用,光纤无需制作特别的接头,根据所需长度随时裁剪,即插即用,使用非常方便[3]。

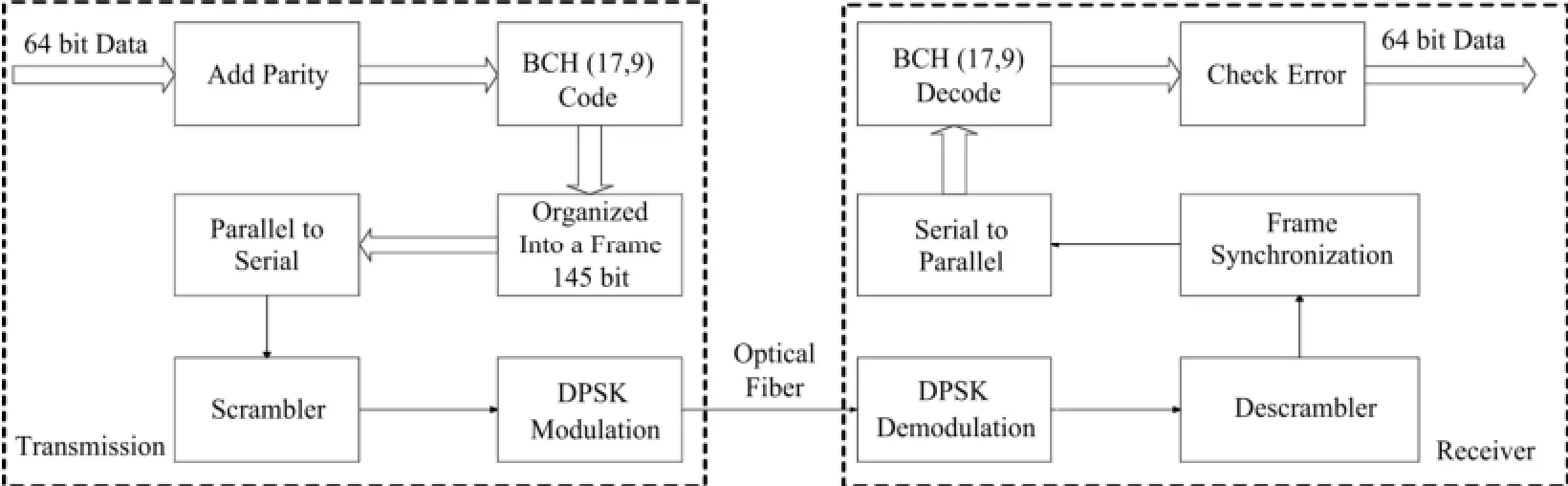

2 重离子治癌加速器高速数据传输系统的软件实现

数据传输的总体结构如图3所示。从PCI系统获得64位有效数据,将其分为8组,分别加入奇偶检验位,进行非本原BCH (17,9)编码,组织成一帧数据后加入扰码,经过DPSK调制后,通过光纤发送出去。在接收端将收到的信号进行解调解扰码后,通过帧同步系统找到帧头,再进行BCH译码与纠错,得到了64位有效数据,完成了一次数据传输[4]。

图3 数据传输的总体设计框图Fig.3 Overall scheme design diagram of data transmission.

2.1 发送端数据的处理

为使此系统可靠性更强,对发送的数据进行了奇偶校验和编码,采用并行处理方式以提高编码效率。将64 bit有效数据分为8组,对每组数据进行逐比特异或计算,将结果添加在每组数据的MSB前作为奇偶校验位。对这8组数据同时进行非本原BCH(17,9)编码。它是一类能纠正多个随即错误的循环码和分组码,可以在给定纠错能力要求的条件下寻找到码的生成多项式,有了生成多项式,编码的基本问题就随之解决了。BCH(17,9)编码能够在每组数据中纠正任意最多两位随机错误[5],一帧数据最多能同时纠正16位随机错误。生成多项式为g(x)=x8+x7+x6+x4+x3+x+1。经过编码后8组数据每组长度是17 bit,高9位是原码,低8位是监督位,监督位将作为数据译码的一个参数。

为了使接收端能够正确识别帧信息中的有效数据,必须给编码后的数据加入帧头,选择了7位巴克码(1110010)作为帧头。巴克码是一组符合特殊规律的码元,它出现在信息码元序列中的可能性非常小。接收端一旦检测到这个特定的码组就立刻知道这种信息码元的“头”[6]。帧头确定后,加上一定冗余位便可以和8组编码后的数据组织成帧。

对数据进行扰码和调制后,就可以完成发送端对数据的处理工作。采用伪随机序列(m序列)来起到“扰码”的作用,本设计采用的本原多项式为F(x)=x5+x3+1。在FPGA设计中,根据所选序列的本原多项式来设置m级寄存器以实现m序列[7]。为了避免解调时出现相位的倒“π”现象,采用DPSK调制方式。它是利用前后相邻码元载波相位的相对变化来传递数字信息的。调制时先对二进制数字基带信号进行差分处理,即把表示数字信息序列的绝对码变为相对码,然后再根据相对码进行调相,从而产生2DPSK信号[8]。其中,差分码的编码规则为b(n)=a(n)⊕b(n−1)。

2.2 接收端数据的处理

在接收端,首先要将收到的数据进行解调和解扰码。先对信号进行解调,由于该系统的基带和载波信号频率很高,利用传统的解调难以实现,因为这些方法要求本地系统时钟频率至少是载波信号频率的几倍甚至数十倍,频率越高解调效果往往越好。但是工作频率高的FPGA价格都非常昂贵,会增加成本,因此我们从信号本身的特征和PSK调制系统的特性出发,运用采样和VHDL语言自身的特点实现了对高频DPSK信号的解调过程。在200 MHz的时钟下寻找相变点(相变点处即基带信号的电平变换点),找到了相变点就知道了前后相邻码元载波相位的相对变化,再经过差分译码和解扰码变化后,得到了10 MHz的基带串行帧。其中,解差分公式为b(n)=a(n)⊕a(n−1),解扰电路采用与发送端同样的寄存器组设置模式。

要得到有效数据,首先要经过帧头识别系统寻找帧头(1110010),确定数据的起始。帧头识别后,为了得到可靠的数据,还要对数据进行译码和检错,运用错误图样查找的方法,既计算校正子S,查看校正子和错码位置关系的表格,找出错码将其纠正,并且通过报错机制把错误信息输出。这样,就得到了服务器发出的64位有效数据。

3 系统测试

测试机箱用NI的机箱,用Labview程序驱动两个控制器,一个发送,一个接收,由PCI提供发送数据,观察接收到的数据与发送的是否相同。

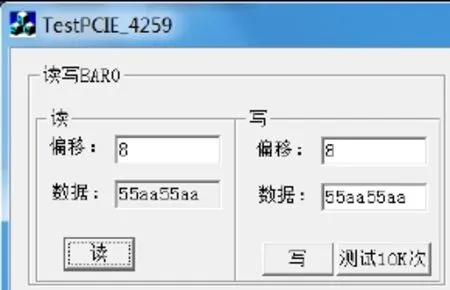

3.1 同板收发测试

因为此设计收发是双向的,用同板自行收发时,测试结果如图4所示。右边“写”是发送端的数据,左边“读”是接收端的数据,可见传输过程中没有出现错误。

3.2 异板收发测试

用两个控制器测试时,数据有可能出错,如图5所示,左边“4259”为发射端,发射的数据为“55aa55aa”,而右边“4258”为接收端,接收到的数据却是“2d920b95”,经过统计,出错率达到百分之十几。

图4 同板收发的实验结果Fig.4 Result of transmitter and receiver on the same board.

图5 异板收发的实验结果Fig.5 Result of transmitter and receiver on the different board.

4 出错原因分析与改进

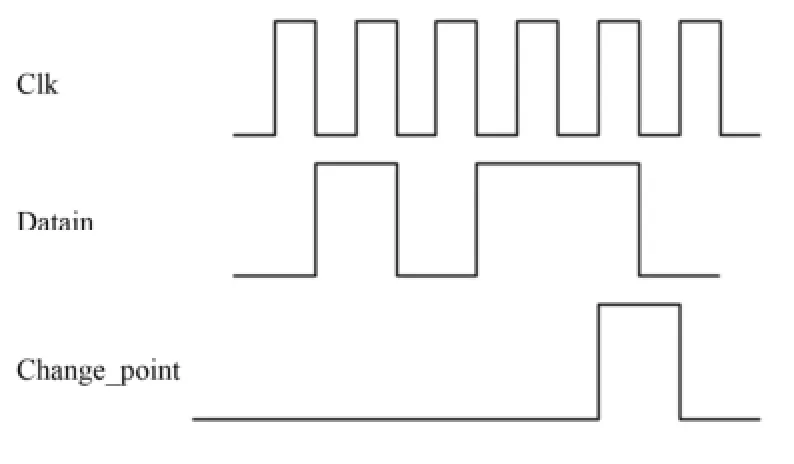

经过反复的实验与观察,发现出错的原因是相变点丢失或者是多出了相变点。在研究过程中,用200 MHz的临界时钟来进行研究。如图6所示,加入200 MHz时钟,若输入数据为1,计数器在时钟上升沿时计数。若不在相变点处,计数器只能计到1,若在相变点处,则计数器会计到2,这就找到了相变点。若是同板收发,发送端和接收端使用同一个时钟源,时钟上升沿到来时,数据已经稳定,能够准确地采样,不会出现错误。

图6 同板收发采用200 MHz采样时钟原理图Fig.6 Schematic diagram of transmitter and receiver on same board with 200 MHz sampling clock.

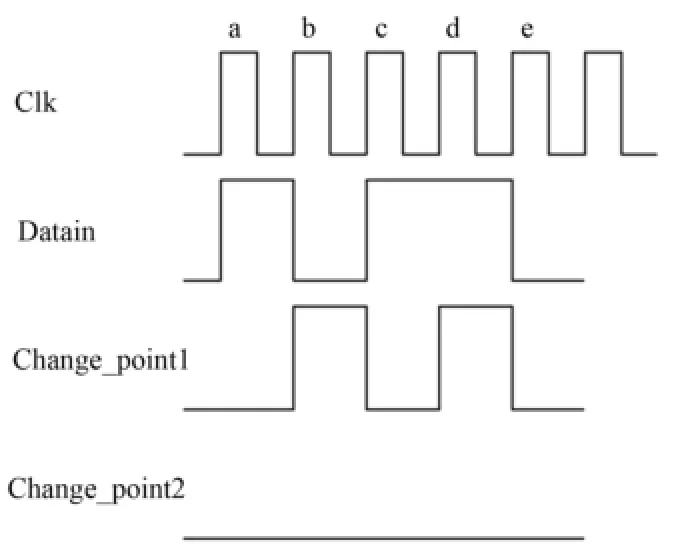

若是异板收发,发送端和接收端的时钟不是同一个时钟源,若时钟上升沿正好在输入数据的中间来临,则数据不会出错。若是如图7所示情况,则会有可能出错,错误有两种可能,若认为a和b处都是1,则计数器会计到2,就会认为此处为相变点,因而多出相变点,如图7中Change_point1所示;若认为c和e处都是0,则计数器在d处计数,只会计到1,就会认为此处不是相变点,因而丢失相变点,如图7中 Change_point2所示。

图7 异板收发采用200 MHz采样时钟原理图Fig.7 Schematic diagram of transmitter and receiver on different board with 200 MHz sampling clock.

若要得到准确无误的数据,计数时要避开数据不稳定的情况,必须要升高时钟频率,又因为EP3C25F256的工作频率不是太高,所以找出可以准确找到相变点的最低时钟频率成为本系统成功与否的关键。

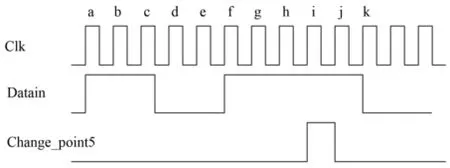

经过分析与研究,选定了500 MHz的时钟频率。加入500 MHz时钟,若输入数据为1,计数器在时钟上升沿时计数。若不在相变点处,计数器只能计到2,若在相变点处,则计数器会计到3、4和5,为了避免在数据不稳定时出现多出相变点或相变点的丢失情况,选定计数器计到4时为相变点。如图8所示,若认为a、b、c处都是1,计数器只会计到3,不会计到4,因而不会多出相变点;若认为f、k处都是0,计数器会在g、h、i、j处计数,完全可以计到4,相变点也不会丢失。因此在500 MHz时钟下,可以准确找出相变点,不会出现任何错误。

图8 异板收发采用500 MHz采样时钟原理图Fig.8 Schematic diagram of transmitter and receiver on different board with 500 MHz sampling clock.

其实,若不一定非要是信号的整数倍,不一定要这么高的时钟频率,但是要在同一个PLL里面同时产生所需的时钟,就必须为整数倍,因此,本文只讨论可以在此程序中实现的情况。综上所述,在解调过程中,在此系统可以实现的寻找相变点的最佳时钟频率为500 MHz。

5 改进后测试

测试方法与§3相同,由图9可以看到,传输过程中没有出现错误。

图9 异板收发的最终实验结果Fig.9 Ultimate result of transmitter and receiver on the different board.

为确保出错率为零,需要发送多组数据来统计出错率,发送端每次发一万帧数据,第一帧为55aa55aa,每发一帧就加1再发下一帧,直到发送一万帧就停止发送,对比发送端和接收端,统计出出错次数,将出错情况和错误率通过.txt文件输出。统计结果出错率为零。连续测试100次,即百万帧数据,出错率为零。

经过大量数据的反复验证,该系统传输数据正确有效,与理论相符。

6 结语

以往的加速器数据传输系统采用的是传统的基带信号直接传输模式,传输速率很低,而且帧头仅为简单的“11”,可靠性也很差。重离子治癌加速器高速数据传输系统在以往加速器数据传输系统的基础上进行了提升,自主研发了基于PCI+FPGA+光纤的传输控制器,在数据传输过程中采用了DPSK调制解调的方式,并且加入了奇偶校验,BCH编解码,扰码与帧同步系统来提高系统的可靠性,所有传输协议解析与调制解调在FPGA上采用VHDL编程实现,降低了设计成本,提高了系统可靠性和灵活性。对设计中出现的问题进行改进,保证该系统可以准确无误地实现数据的传输过程,使重离子治癌加速器高速数据传输系统能够稳定可靠运行。该系统保证了输出数据的速度、精度和实时性,以及数据传输中的正确性。该系统经过反复测试,已经运用于重离子治癌加速器的现场,工作情况良好。

1 毛文宇, 乔卫民, 敬岚, 等. 重离子治癌加速器高速实时数据传输系统研制[J]. 原子能科学技术, 2012, 46(12): 1502−1507

MAO Wenyu, QIAO Weimin, JING Lan, et al. Design of high-speed data transmission system for Lanzhou heavy ion therapy accelerator[J]. Atomic Energy Science and Technology, 2012, 46(12): 1502−1507

2 Altera Corporation. Cyclone3 handbook[OL]. http://www. Altera.com/support/devices/cyclone3/dev-cyclone3.html, 2010

3 Firecomms. EDL300T datasheet[OL]. http://www. firecomms.com/downloads/datasheets/2012/EDL300T_D ata_Sheet.pdf, 2007

4 毛文宇. 重离子治癌加速器控制系统中多功能控制组件的研究[D]. 兰州: 中国科学院近代物理研究所, 2013: 97−101

MAO Wenyu. Study on multifunction control component in the heavy ion therapy accelerator control system[D]. Lanzhou: Institute of Modern Physics, Chinese Academy of Sciences, 2013: 97−101

5 Cho J, Sung W. Efficient software base encoding and decoding of BCH codes[J]. IEEE Transactions on Computers, 2009, 58(7): 878−889

6 樊昌信, 曹丽娜. 通信原理[M]. 北京: 国防工业出版社, 2006: 188−194

FAN Changxin, CAO Lina. Principle of communication[M]. Beijing: National Defense Industry Press, 2006: 188−194

7 李欢. 伪随机序列的FPGA设计与应用[J]. 科技信息, 2011, (17): 508

LI Huan. FPGA design and application of a pseudo-random sequence[J]. Science & Technology Information, 2011, (17): 508

8 赵叶星, 韦志棉. 基于FPGA的DPSK调制解调器的全数字实现[J]. 无线电工程, 2007, 37(10): 21−22

ZHAO Yexing, WEI Zhimian. Digital realization of DPSK modem based on FPGA[J]. Radio Engineering, 2007, 37(10): 21−22

CLC TL56

Design and implementation of high-speed data transmission system for the heavy ion therapy accelerator

YANG Fan1,2LI Guihua2YANG Guiqin1ZHANG Zhijing1,2

1(Lanzhou Jiaotong University, Lanzhou 730070, China)

2(Institute of Modern Physics, Chinese Academy of Sciences, Lanzhou 730000, China)

Background: Heavy ion therapy accelerator is introduced to reconstruct a dedicated synchrotron for medical treatment based on HIRFL-CSR (Heavy Ion Research Facility in Lanzhou-Cooling Storage Ring). Synchronous transmission of HIRFL-CSR uses the 400 kHz baseband signal with optical fiber. Purpose: The bandwidth and reliability of heavy ion therapy accelerator need to be improved for practical application. Methods: Differential phase shift keying (DPSK) modulation and demodulation method has been adopted, combined with the parity check, BCH codec, scrambling and frame synchronization system, to improve the reliability of system. Further improvement on both hardware and software implementation is taken to avoid any error in transmission process. Results: Experimental results show that the error times reduced to zero by using two boards to send and receive data. It is proved that the system can transmit data correctly and effectively. Conclusion: The system can accurately finish the data transmission with high reliability for the high-speed data transmission system of the heavy ion therapy accelerator. It has been directly applied to the scene of the heavy ion therapy accelerator.

Heavy ion therapy accelerator, Data transmission, DPSK (Differential Phase Shift Keying) modulation and demodulation, Phase change point, FPGA

TL56

10.11889/j.0253-3219.2015.hjs.38.010403

重离子治癌束流的精确位置控制研究(No.Y207150GJ0)资助

杨帆,女,1990年出生,2012年毕业于兰州交通大学,现兰州交通大学在读硕士研究生,研究方向为通信与信息系统

2014-09-10,

2014-11-05