基于IPM 的静止无功发生器硬件电路设计

2015-11-25崔玮玮陈宇晨刘昱彤

□崔玮玮 韦 钰 陈宇晨 王 凯 刘昱彤

一、引言

静止无功发生器(SVG)是经过电抗器将自换相桥式电路并联接入电网,通过对桥式电路交流侧输出电压的相位与幅值的改变来满足无功补偿的要求,以达到无功补偿的目的。

图1 SVG 系统构成框图

二、静止无功发生器的工作原理与基本结构

静止无功发生器系统构成框图如图1 所示,硬件电路主要包括:整流电路、逆变电路、智能功率模块IPM 的驱动电路、过零检测电路,电流调理电路,锁相环电路。逆变电路采用了IPM,该芯片内含驱动电路,报警电路等独特结构,一方面提高了系统的可靠性;另一方面也避免了保护电路的另外设计,简化了硬件装置的设计。

主电路主要由整流部分和逆变部分组成。整流部分通过三相不可控整流桥将三相交流电压转换为三相直流电压,在经过电容滤波后得到稳定的直流电压。逆变部分采用SPWM 控制技术来控制IPM 内部IGBT 的开断从而获得所需的补偿电流。将整流输出的直流电逆变转化为交流电回馈到电网。IPM 内含保护电路,当发生故障时,IPM 的自保能力使得IGBT 的损坏率较低,提高了系统的可靠性。

三、SVG 各硬件电路组成

(一)整流电路。整流电路采用三相不可控整流桥,输出的三相直流电通过电容稳压、滤波获得稳定的直流电压。根据以往的经验,直流侧电容取用4 个2200μF/450V 的电解电容,两并两串接进电路。电路组成如图2 所示。为了避免大电流烧坏整流装置,电容需要通过一个充电电阻对不可控整流桥的输出端进行充电,直到充满在直接接到不可控整流桥的输出端。另外,为避免故障发生,在不使用整流电路时要对滤波电容进行放电。根据计算的电压、电流,选用二极管整流模块6RI30G-160G-120 即(30A,1200V)。

(二)IPM 及其外围驱动电路。通过计算智能功率模块(IPM)参数,选用型号为PM25CLA120 的IPM(25A,1200V),内部有IGBT,内含驱动电路。通过资料得知IPM 驱动电路的控制电源电压范围为13.5V~16.5V,本文选用4 路隔离的l5V 直流电源。利用DSP 发出PWM 信号经光耦器件隔离后作为驱动信号对IPM 进行控制。

(三)电流调理电路。该电路可将18A 的电网电流相量转换成0~3Vpp 的电压信号并实现过零点检测功能。该电路与电压调理电路的组成基本一致,不同之处在于互感器TVA1421-01 用作电流互感器,采样电阻取59Ω。若一次侧电流为18A,二次侧输出(-0.5~+0.5)V 的正弦波;经放大电路,输出电压(-1.5~+1.5)V 的正弦波;最后经过加法电路输出(0V~3.00V)的电压信号。同时大于50Hz 的正弦信号被滤除。过零比较电路在正弦波的过零时刻输出下降沿跳变。

图2 主电路整流部分原理图

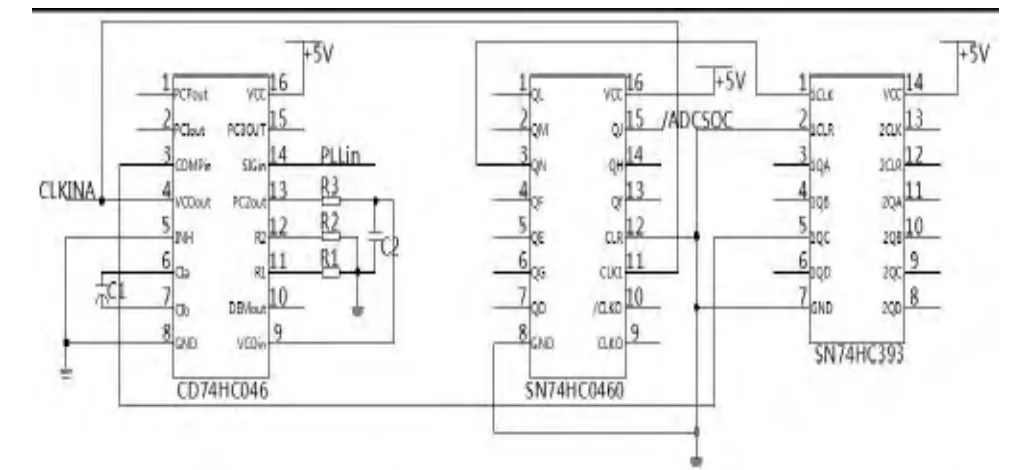

(四)锁相环电路。本文采用了由TI 公司生产的CD7H4C4046 型锁相环芯片对电网频率进行跟踪,避免了利用固定频率采样时产生的误差。本系统中,锁相环的输出信号有两大作用:一是作为ADC 模块的转换触发信号;二是作为事件管理器A(EVA)的时钟输入信号。通过锁相环电路使其产生跟随电网频率变化的SPWM 波,从而精确控制后级逆变器。

图3 锁相环电路原理图

四、实验结果分析

对各个部分硬件电路进行实验,经过实验,各部分均能达到其功能要求,部分输出波形如图4~7 所示。其中,图4 为输入电压为50V 时的整流模块电路输出波形,得到平均值为67.13V 的直流信号。图5 为电流调理电路输出波形,为得到0~3V 的电压信号以供DSP 采样。图6 为锁相环电路输出波形,以实现跟踪电网频率的变化的作用。图7 为DSP 发出的带死区时间的PWM波,用来控制IGBT 的开断。

图4 整流输出波形

图5 电流调理电路输出波形

图6 锁相环电路输出波形

图7 带死区时间的PWM 波

五、结语

本文论述了静止无功发生器的基本原理,实现了SVG 的硬件电路设计,主要包括:逆变电路、整流电路的设计及储能电容的选择、电流调理电路、锁相环电路、IPM 及其外围驱动电路,并通过实验验证,各级电路的输出符合实验要求。

[1]邹鑫.基于DSP 的静止无功发生器的设计[D].大连海事大学,2011

[2]周俊.基于IGBT 的静止无功发生器的研究[D].江苏大学,2006

[3]佟艳.基于DSP 的静止无功发生器的研究[D].天津大学,2007

[4]鲍晓娟.基于TMS320F2812 的静止无功发生器控制系统研究[D].北京交通大学,2012

[5]陈敏.静止无功发生器-SVG-控制器[D].广西大学,2006

[6]陈新苗.基于DSP 控制的静止无功发生器的研究与试验[D].广西大学,2012