机载计算机高速数字电路系统的硬件抗干扰设计

2015-11-22李成文

杨 涛 李成文 陈 国 范 超

(中国航空计算技术研究所,陕西 西安 710065)

机载计算机高速数字电路系统的硬件抗干扰设计

杨 涛 李成文 陈 国 范 超

(中国航空计算技术研究所,陕西 西安 710065)

文章首先分析了机载计算机高速数字电路系统干扰噪声产生的原因,然后分析了干扰噪声耦合途径,最后重点阐述了硬件抗干扰设计,其中硬件抗干扰设计内容包括:元器件选择、电源地设计、几种典型电路设计、总线设计等。

信号;噪声;干扰;耦合

随着航空技术的快速发展,飞机对航空电子设备提出了越来越高的要求,它不仅要求航空电子设备有很高的性能价格比,更要求航空电子设备有很高的可靠性。机载计算机在众多的航空电子设备里处于核心位置,对整个飞机状态起控制作用。因此机载计算机既要很高的处理速度又要具有非常高的可靠性。但高速度的机载计算机会有很多不可靠因素,一方面由于机载计算机所处的环境十分的恶劣,表现在温度、振动、冲击、温热、盐雾、霉菌等。另一方面机载计算机数字系统的速度不断提高,也会带来许多低速数字系统所没有的噪声干扰。本文针对机载计算机高速数字系统的特点,分析干扰噪声产生的原因及传播途径,从硬件角度提出抗干扰设计的方法。

1 干扰噪声产生的原因

噪声是任何不希望有的对系统产生负作用的信号。噪声分内部噪声、人为噪声和自然噪声。人为噪声是由其他电子设备或系统产生的噪声,自然噪声是天文气象中大自然产生的噪声。人为噪声和自然噪声是系统外部的,通过隔离和屏蔽措施可以避免。内部噪声是系统内部或器件本身产生的噪声。下面着重分析机载计算机高速数字系统内部干扰噪声产生的原因。

1.1过渡干扰

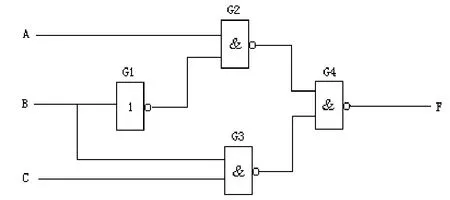

过渡干扰是由于逻辑信号传输时间的影响而引起的干扰。它与电路内部竞争、险象以及可能出现的中间状态有关。例如,在图1的逻辑电路中,信号B发生变化时,该变化经G1和G2到达G4的时间与经G3到达G4的时间有先有后,使得电路出现竞争现象。

图1 竞争电路

过渡干扰可以导致系统产生错误的逻辑动作,使逻辑关系混乱,控制失灵,甚至破坏电路正常工作。

1.2尖峰噪声

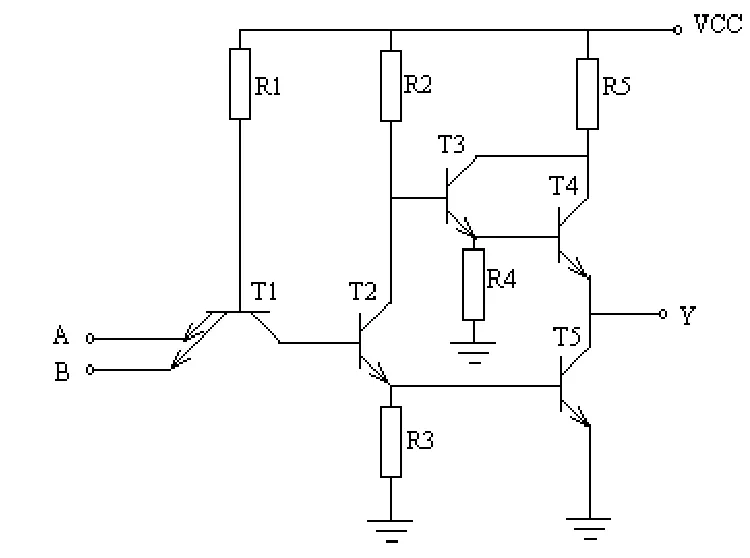

尖峰噪声是由器件的开关门动作引起的。器件在开关时会产生很大的冲击电流,并在传输线和供电电源内阻上产生较大压降形成尖峰噪声干扰。在如图2所示的TTL与非门中,当输出端开关时,引起晶体管T4和T5在截止和饱和状态之间转换,由于这种转换需要一定的时间,因此T4和T5有一短时间处在导通状态,使得输出负载增大。这种增大的负载在电源VCC上引起一个负尖峰信号,在电源地VSS上引起一个正尖峰信号。高速电路系统中,许多门同时快速开关,在电源和地线上将引起严重噪声。

图2 TTL与非门

1.3电磁干扰

电磁干扰(EMI)是由于任何载流导体周围存在磁场而引起的,来自一个导体的磁通量在另一个导体可以感应电流而产生瞬时电压。根据Fourier信号分析理论,快速跳变信号在产生和传输过程中,必然伴随着丰富的高次谐波的产生和传输,这些信号放大之后会产生电磁能量辐射,因此在高速数字电路系统中,电磁噪声是很严重的干扰源。

1.4静电干扰

静电干扰(ESI)是由两个邻近的导体通过电容耦合而引起的。由于任意两条导线之间均存在分布电容,相邻两导线之间分布电容比较大。这样两根邻近的导线就象电容器的两个极板那样起作用;在一个导体上建立的电荷在另一个导体上感应出相反的电荷。

1.5反射干扰

信号反射是由于终端负载不匹配造成的。在高速数字电路中,信号线的负载电容对信号传输影响很大。由于负载电容的存在,随着信号线的增加,信号在传输线上的延时会增加。这使得信号在未经终端匹配的信号线上传输过程中发生多次反射,导致振铃现象。振铃会产生非法电压过渡,甚至损坏元器件。

2 干扰噪声耦合途径

干扰噪声产生后,要经过传输途径耦合的其他电路中,对被干扰对象产生干扰。下面分析干扰噪声几个主要的耦合途径。

2.1信号线耦合

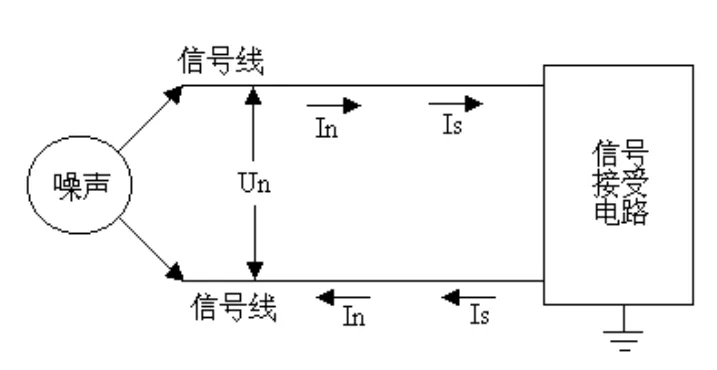

信号线耦合是干扰噪声经过信号导线直接传导到信号接受电路中而造成对接受电路的干扰。信号线耦合最常见的传导模式是差模传导和共模传导。

差模传导方式如图 3所示。噪声往返与两信号线间,噪声电流和信号电流的往返路径是一致的。

图3 差模传导噪声

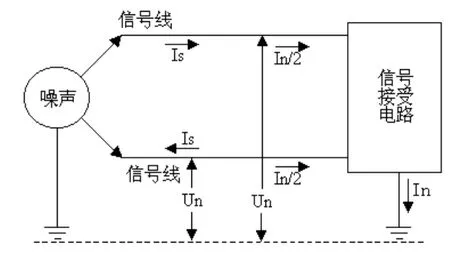

共模传导方式如图 4所示。噪声电流在两信号线上各流一部分,以地为公共回路。信号电流只在往返信号线上流过。

图4 共模传导噪声

2.2电源地耦合

电源地耦合是一个器件产生的干扰噪声经过电源线和地线耦合到系统各器件中。在高速数字电路系统中,器件快速开关产生的尖峰噪声大部分是通过电源地耦合到其他电路。

2.3公共阻抗耦合

公共阻抗耦合是干扰噪声通过噪声源和信号源的公共阻抗传导耦合。因为两电路的电流流经一个公共阻抗时一个电路在该电阻上的电压降将会影响到另一个电路。常见的公共阻抗耦合有公共地和电源阻抗两种。

2.4电容耦合

电容耦合是干扰噪声通过电路中的分布电容耦合到被干扰对象。由于元件之间、导线之间、导线与元件之间存在着分布电容,若在一导体上发生电位变化通过分布电容使其他导体的电位受到影响。

2.5电磁辐射耦合

电磁辐射耦合是高频干扰噪声通过电磁场辐射耦合到被干扰对象。在高速数字电路中,由于信号脉冲快速变化产生高频电流。当高频电流流过导体时,该导体周围产生电力线和磁力线,并发生高频变化,从而形成一种在空中传播的电磁场。处于电磁波中的导体便会感应出相应频率的电动势。

3 硬件抗干扰设计

由于机载计算机高速数字系统的高速特性,使得系统噪声产生很复杂而且噪声也更为严重。这需要硬件电路设计者全面权衡、精心设计,采用有效措施来消除干扰噪声源,阻断干扰噪声的传输通道,以提高系统抗干扰能力。

3.1元器件选择

元器件是构成系统的基础。设计者在进行电路设计时,要根据系统(或模块)的功能特性精心选择器件。为提高机载计算机的速度和抗干扰性能,建议设计者选择那些速度快、集成度高、抗干扰能力强、功耗小的元器件。使用集成度高的器件,可以使减少印制板连线,从而可以减少线间串扰。使用功耗小的器件可以降低器件的发热量,这样可以减少因器件温飘引起的噪声。

3.2电源地设计

很多干扰噪声是通过电源引入机载计算机系统,并由电源线和地线传导耦合到各电路中。因此对引入系统的电源先要经过滤波器滤波,其作用可以抑制供电电源尖峰,同时也可以防止电磁干扰侵入系统。然后经过电源模块的变换、整流和稳压等处理得到系统工作电压。为阻止电源噪声侵入系统各功能模块中,需要对各功模块的输入电源实施去耦滤波。其方法是在印制板入口处的电源线和地线间放置一个大容量的钽电解电容和一个小容量的非电解电容。大电容滤除电源的低频干扰成分,小电容滤除电源的高频干扰成分。另外在IC器件的电源线和地线间接入0.1μF的去耦电容,其作用可提供和吸收IC器件开关瞬间的充放电能量,同时可以旁路掉器件的高频噪声。在器件的电源和地线间放置去耦电容来消除尖峰噪声,因为去耦电容可以提供器件开关过程中所需的额外电流。

3.3电路设计

3.3.1复位电路设计

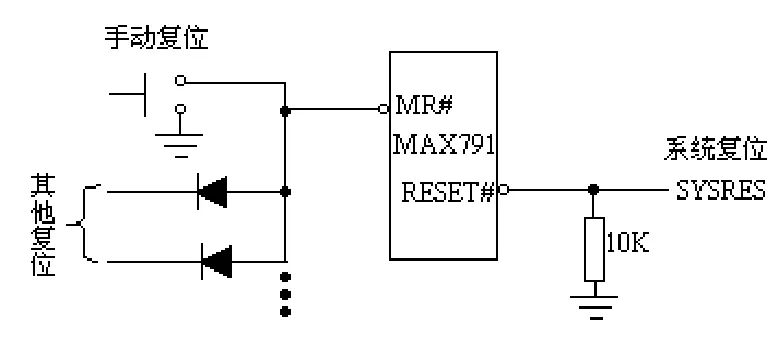

复位信号对噪声很敏感。 设计可靠的复位电路能够有效地提高数字系统的抗干扰性能。复位电路要求具有快速上电复位和掉电复位功能。如图5,用MAX791芯片可构成良好的复位电路。MAX791能监控电源电压,复位产生时间足够长可保证系统完成复位。MAX791产生复位输出的条件如下:

(1)电源VCC<4.65V;

(2)复位输入MR#<1.25V;

(3)复位输出保持200ms。

图5 复位电路

3.3.2时钟电路设计

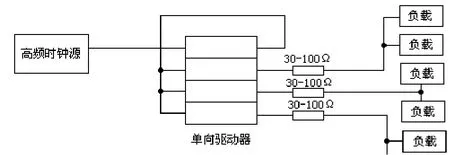

在高速数字系统中,高频时钟信号是严重的干扰源,同时也易受到噪声的干扰。时钟是系统的同步基准信号,必须避免受噪声干扰。高频时钟电路设计如图 6所示,高频时钟信号经单向驱动器驱动,再用串联电阻端接时钟输出以获得完整规则的时钟信号。端接电阻用具有低电感的磁膜电阻。在一条时钟线上不可放置多余两个以上的负载一避免时钟信号产生反射。为避免高频时钟干扰信号,时钟线应用地线包起来。

图6 高频时钟电路

3.3.3处理器电路设计

中央处理器CPU是高速数字系统核心器件,易受到噪声的干扰。处理器电路设计如图7所示,CPU的数据、地址和输出控制信号经驱动器驱动送到局部总线,局部总线的数据、地址和输入控制信号经驱动器隔离送中央处理器。这样设计处理器是基于如下两个因素:

(1)由于 CPU是大规处理芯片,集成度高,发热比较大。为尽可能降低 CPU的功耗,其驱动能力很低,一般为2~5mA。因此驱动器可提高CPU的负载能力;

(2)外部的干扰噪声是通过总线传导耦合到 CPU。当CPU受到噪声干扰后,会造成程序计数器PC值改变。PC值被干扰后是随机的,CPU在PC值的错误引导下,引起程序混乱,破坏程序正常运行,从而使系统失去控制。因此CPU受到的干扰会对系统引起很坏的影响,为了减少噪声对CPU的干扰,采用驱动器的隔离措施阻止噪声侵入CPU。

图7 处理器电路

3.3.4看门狗电路设计

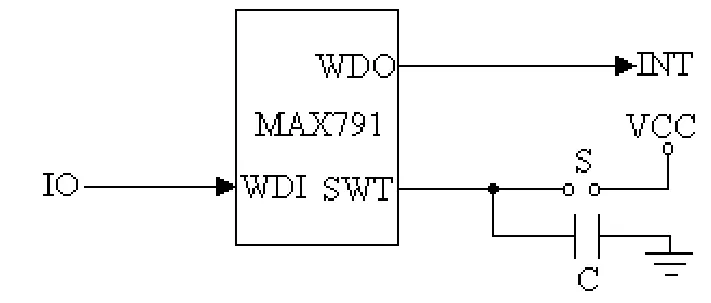

看门狗电路主要用于监控程序运行周期,防止程序“跑飞”或陷入“死循环”。看门狗电路不断监视程序循环运行时间,若发现时间超过定时的时间,则认为程序“跑飞”或陷入“死循环”。这时看门狗电路产生中断,引导中断处理程序处理看门狗超时故障。看门狗用电路MAX791实现,电路设计如图8所示。看门狗输入WDI来自IO口离散量,看门狗输出WDO送给中断INT处理。SWT用于设置看门狗定时时间,当SWT通过跨线S接电源VCC时,看门狗报警周期为1.6秒。如果在1.6秒内WDI的输入电平没有变化,即没有定时“喂狗”,则WDO会产生报警输出给中断INT。

看门狗定时周期可以由用户自行配置。用户在不跨接 S的情况下,改变电容C的值,可改变看门狗定时周期。定时周期preriod按公式1计算:

图8 看门狗电路

3.3.5控制电路设计

控制电路一般由可编程器件实现,控制逻辑由设计者自己编写。控制电路要根据系统时序要求产生各种控制信号以控制系统各电路有条不紊的工作。在逻辑电路设计中增加冗余项或在信号输出端增加滤波电路可以消除过渡干扰。

3.4总线设计

在高速数字电路系统中,信号在总线上传输所造成的延迟、总线的负载、总线上由于分布参数造成的交叉串扰、由于负载不匹配造成的反射等问题变得不可忽略。总线设计要注意以下几个问题。

3.4.1总线分级

为了使故障隔离,阻止外部噪声入侵,可将总线分级,每级总线总线设计接口电路并由驱动器隔离。一般可将总线分成局部总线、系统总线和IO总线。

局部总线用于处理机程序和数据存储器。因为CPU访问ROM和RAM的频率远高于访问其他资源,这样可保证处理机快速访问存储器。

系统总线用于处理机模块和系统其他模块间的连接,其总线宽度小于局部总线。IO总线用于处理机访问 IO设备,速度要求很低。

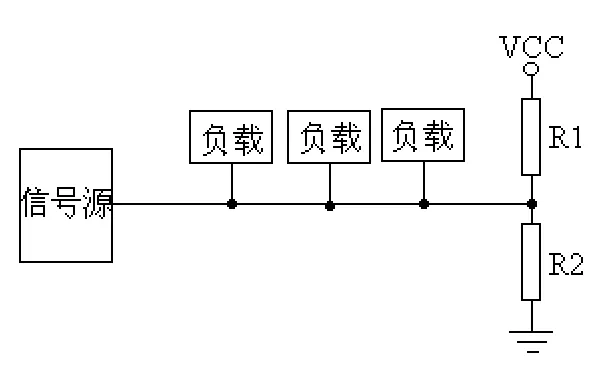

3.4.2总线上拉

为了是总线稳定,要求用电阻上拉总线。数据总线上拉有利于消除三态状态;地址总线上拉可增加地址变化惰性;控制总线上拉可降低毛刺的干扰。

3.4.3线路端接

在高速数字电路中,由于负载不匹配造成的反射变得很严重。反射可引起假信号跃变、数据错误和对输入电压电平的干扰。对信号线进行端接可以使信号反射减至最小并且能抑制输入电平的上冲和下冲。线路端接有串联端接和分岔端接两种。

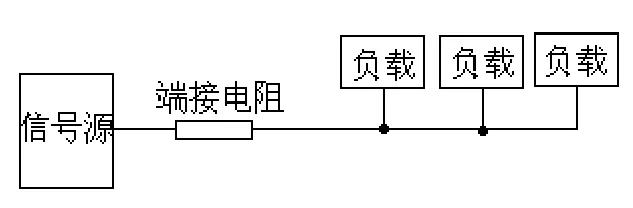

串联端接如图 9所示。串联端接方法补偿信号沿线路运动以前所产生的过流。因为端接电阻增加了信号的上升和下降时间,从而使线路在较长时间内发生电流变化。

图9 串联端接

分岔端接如图 10所示。分岔端接调整线路终端电流。因为当线路电压开始上升超过VCC时R2电阻吸收多余的电流,当线路电压开始上降到地以下时R1电阻向电路提供电流。

图10 串联端接

4 结束语

机载计算机高速数字电路系统的干扰噪声很复杂。对于具体的系统,要提高系统的可靠性和看干扰性能需要设计者的精心设计。本文介绍了机载计算机高速数字电路系统的硬件抗干扰设计方面的内容,可以为大家提供有益的参考和借鉴。总之,机载计算机需要很高的可靠性,希望设计者重视系统的抗干扰设计。

[1] 刘川.测试技术研究[J].电子科学,2009,18(1):50-53.

[2] 王建晓,初伟先,于宏波.单片机系统硬件抗干扰的方法[J].山东科学,2006,(5):59-61.

[3] 路宏敏.工程电磁兼容[M].西安:西安电子科技大学出版社,2003.

[4] 吴良斌.现代电子系统的电磁兼容性设计[M].北京:国防工业出版社,2004.

[5] 石波涌,邓湘平,陈乐.数字电路设计中的抗干扰技术[J].科技创新导报,2008,(9):69-70.

Airborne computer hardware anti-interference of high-speed digital circuit system design

This paper first analyzes the onboard computer cause of high-speed digital circuit system interference noise, and then analyzes the interference noise coupling way, finally expounds the hardware anti-interference design. Hardware anti-interference design content includes: several typical circuit components selection, power supply design, design, and bus design.

Signal; noise; interference; coupling

V271.4

A

1008-1151(2015)06-0001-04

2015-04-11

杨涛(1981-),男,陕西武功人,中国航空计算技术研究所工程师,硕士,研究方向为机载计算机硬件设计与调试。