多通道数据采集系统硬件设计

2015-11-01张军权姚舜才

张军权 姚舜才

多通道数据采集系统硬件设计

张军权 姚舜才

本设计介绍了数据采集系统的特点、功能、原理和发展趋势,并分析了系统的基本组成部分,以及系统设计时应考虑的因素。

本设计通过查阅采集系统相关的资料,提出了多通道数据采集系统的硬件电路设计方案。该电路实现了数据的采集和存储,并且存储器还带有掉电保护功能;在读信号有效时,能把存储器内的数据输出,经过并口线传输到计算机上,通过数据处理复现其输入模拟信号的波形。

数据采集与数据采集系统

在微型计算机应用于智能仪器仪表、信号处理和工业自动化等的过程中,都存在着模拟量的测量与控制问题。即将温度、压力、流量、位移及角度等模拟量转变为数字信号,在收集到微型机进一步予以显示、处理、记录和传输这个过程称为“数据采集”。相应的系统即为数据采集系统。

数据采集系统的任务

数据采集的任务,具体地说,就是采集传感器输出的模拟信号并转换成计算机能识别的数字信号,然后送入计算机或相应的信号处理系统,根据不同需要进行相应的计算和处理,得出所需的数据。与此同时,将计算机得到的数据进行显示或打印,以便实现对某些物理量的监视。数据采集几乎无孔不入,它已渗透到了地质、医药器械、雷达、通讯、遥感遥测等各个领域,为我们更好的获取信息提供了良好的基础。

数据采集系统基本组成部分

1.测量系统:由计算机、控制器、标准接口、仪器仪表、开关等组成。主要功能是对器件和系统的电压、电流、频率、电阻进行精密测试。精度较高。

2.测试系统:由计算机控制器、标准借口、测量设备和多路扫描开关、传感器等组成。主要功能是将温度、压力、流量、速度等物理量转换为电量进行测试。速度较快。

3.控制系统:由计算机、控制器、标准接口、传感器输入和控制输出电路组成。主要功能是进行过程控制。

4.存储系统:由计算机、传感器阵列、系统能源、位置指示器存储测试电路系统、环境保护器等构成。它的主要功能是在高温、高压、强冲击震动、高过载等恶劣环境和紧凑设计条件下,自动完成被测信息的实时采集与存储记忆。

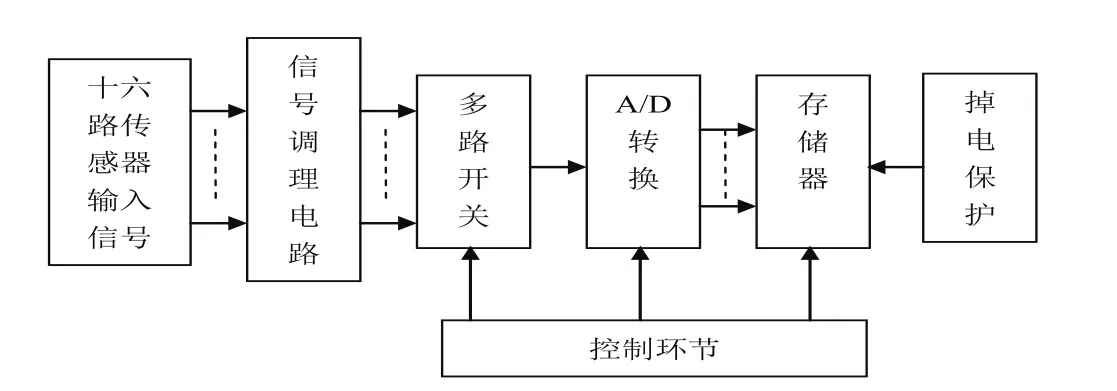

硬件电路设计方案

硬件电路设计

本课题完成对16路模拟信号的采集和存储,存储数据具有掉电保护功能,可通过并行口将存储数据上传到计算机,通过对存储数据的处理复现输入模拟信号的波形,并且每个通道均可采用25K/12.5K两种频率来进行采样。其原理图如图1。

数据采集系统硬件的逻辑结构

数据采集系统的硬件部分,从其功能上主要分为以下四个部分。

1.电平转换部分:对前端电路进行阻抗匹配和信号电平的变换。

2.AD转换部分:对信号进行模拟信号到数字信号的转换。

3.数据缓冲部分:对转换后还没有传入内存的数据进行缓冲存储。

图1 系统原理图

控制逻辑部分:控制与协调各模块之间的工作

主要组成部分设计

信号调理电路

信号调理电路的主要功能有以下三点。

(1)滤波

数据采集系统所工作的现场,往往有很多干扰信号,有时幅度很大,甚至比有用信号还大,这些干扰信号影响到测量精度和测量的可靠性,必须将它滤除,滤波器的作用就是滤除这些干扰,确保测量的精度。

(2)激励信号及辅助装置

传感器的作用是将物理信号转换为电压信号,转换过程中,有些传感器需要激励电源,如RTD、应变片等。激励信号的稳定性将直接影响到测量结果。

(3)消除静态信号的影响

在一些测量中,有时除有用信号外,还有一些恒定的电压信号,两者叠加在一起,虽然可以通过软件在所采集的数据中,将它们分离出来,但由于加到A/D转换器的信号是两者叠加的,有用信号仅是其中一部分,从而降低了A/D实际的分辨率,影响到测量精度,应予消除。

AD9221转换器

本系统采用的是美国ANALOG DEVICE公司的12位高速单片A/D转换芯片AD9221。AD9221具有片内采样保持电路以及低温度漂移系数的基准电源,仅以单一的+5V电源工作。它的无杂散动态范围可达80dB,比较适合本系统要求;同时高速A/D电路的模拟信号输入采用单电源的缓冲运算放大器,避免了毁灭性的ADC过激励。转换速率为1.5MSPS。其原理如图2所示。

各部分原理图说明

以下是用Protel99SE画出的16通道数据采集系统设计的各部分原理图。

计数电路

图2 AD9221原理图

晶振EX03产生的晶振频率随着A0、A1、A2接的电平不同,产生不同的频率,当A0、A1、A2同时接地时,晶振EX03产生的频率为16MHz。74HC160计数器是同步十进制分频器,兼有异步置零和预置数功能。晶振EX03,分频器74HC160,计数器CD4040如下图连接在一起构成了把频率为16MHz的晶振,通过十分频器74HC160把原本16MHz的频率变成1.6MHz,然后再在计数器CD4040的输出端表现出相应的频率。QA、QB、QC、QD、QE、QF对应的频率分别为800KHz、400KHz、200KHz、100KHz、50KHz、25KHz。本设计选择是400KHz和200KHz的频率,当接入400KHz时,就使得每个通道按25KHz的频率进行采样;而当接入200KHz的频率时,每个通道就是按照12.5KHz的频率进行采样。计数电路原理图如图4。

图3 计数电路

图4 写信号控制电路

图5 读信号控制电路

写/读信号控制电路

当写信号为低电平,读信号为高电平时,写信号有效,采集的数据通过数据缓冲器存储到存储器中;当读信号为低电平,写信号为高电平时,读信号有效,原存储的数据从存储器628512中输出,经过缓冲器74HC245传输到并口,再经并口传输到计算机。其写/读控制图如图4与图5所示。

10.3969/j.issn.1001-8972.2015.09.012