汉明码在试飞测试中的应用

2015-11-01邢达波

艾 波 邢达波

汉明码在试飞测试中的应用

艾 波 邢达波

针对试飞测试数据传输中的误码问题,提出了基于纠错码和交织技术的试飞测试数据抗误码方法。介绍了汉明码和交织技术原理,在ISE中设计实现了采用(7,4)汉明码和7行7列交织器的16比特纠错系统,并在ModelSim中进行功能仿真,仿真结果表明能并行对4组连续7比特误码进行纠错。

试飞测试是在真实飞行条件下获取航空设备性能参数的关键环节。正确有效的测试数据不仅有利于分析航空设备的性能状态,缩短研发周期,也为飞行监控提供客观依据,有利于确保飞行安全。随着通信技术的发展,数字化、编码及FPGA技术在试飞测试中得到广泛地应用。然而,实际飞行环境复杂多变,量化、编码后的测试数据在传输时会受到随机噪声、瞬变交流电、多径效应、强电磁干扰影响等而产生误码。若误码出现在数据的高位上,会造成极大的数据误差,不利于试飞研究和飞行安全。

为解决试飞测试中的误码问题,先分析试飞测试数据错误类型,提出基于纠错码和交织技术的数据抗误码方法,然后介绍汉明码及交织技术原理。最后,在ISE中设计实现了采用(7,4)汉明码和7行7列交织器的16比特纠错系统,并在ModelSim中进行功能仿真。

试飞数据错误类型与解决方案

数据在传输时有三种错误类型,即随机错误、突发错误和混合错误。随机错误即数据误码零散随机出现,并不是连续的。突发错误即数据误码是连续出现的,通常一个突发错误表现为首尾码元错误、且中间码元误码较多。混合错误即是随机错误和突发错误的组合。在飞行试验中,数据传输环境比较复杂,测试数据在遥测传输时会受到多径效应、码间干扰等影响而产生随机错误。飞机交流发电机产生的电磁场及遥测天线的辐射场也会影响FPGA器件逻辑状态,产生突发错误,造成数据连续误码。通常纠错码用于对随机误码进行检错与纠错,而对连续多个误码的检错与纠错性能极差。为解决连续误码纠错问题,采用纠错码和交织技术相结合的方案进行数据抗误码设计,通过交织、解交织将成串误码分散化为随机误码,再采用纠错码进行纠错。

纠错技术原理

汉明码纠错原理简介

设原信息序列长度为K bit,冗余码元长度为R bit,则纠错码码字长度为N=K+R bit。若该纠错码能够纠正1个误码码元,则N、K和R应满足下式(1):

这是因为信息序列和冗余码元都可能发生误码,而R bit的冗余码元必须要能辨别哪一位出错,且还要能识别没有出错的状态。当(1)式中不等式取等号时,该纠错码就是汉明码,它是能纠正单个误码码元的线性分组码,亦称为(N,K)线性分组码。汉明码编码和译码比较简单、硬件实现容易,且具有抗干扰能力强、资源消耗少等特点,在通信领域和数据存储中应用十分广泛。

(N,K)线性分组码编码的本质就是在n维线性空间中找出K个长度为N的线性无关的矢量g0,g1,…gK-1,使得每个编码码字C都能表示成这K个矢量的线性组合,如下式(2)矩阵形式所示。

其中,M=[mK-1,mK-2,…,m0]是原信息序列,mi∈{0,1},i=0,1…k-1。G称为生成矩阵,它是由线性无关的矢量g0,g1,…gK-1组成的K×N矩阵。生成矩阵确定后,通过(2)式可求出汉明码字C,实现汉明编码。汉明码字C中的信息序列和冗余码元构成了一种校验关系。

每一个生成矩阵G都对应一个校验矩阵H,使得G×HT=0。在二进制数域中,若生成矩阵G=[IK,P],则校验矩阵H满足下式(3):

其中,P为K×R矩阵,PT为P转置矩阵,IK为K阶单位矩阵,IR为R阶单位矩阵。

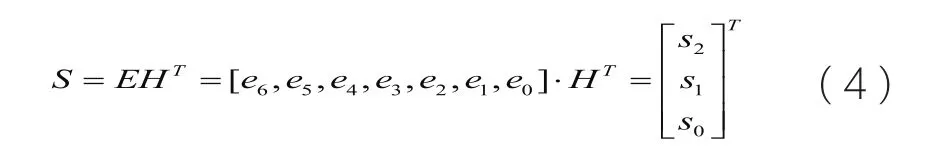

若接收码字和发送码字分别为R、C,其差为E=R-C=[e6,e5,e4,e3,e2,e1,e0],由伴随式定义有:

若发送码字C在传输过程中有误码,则接收码字R的信息序列与冗余码元不再满足原校验关系。可以根据S是否为0来判断C在传输过程中是否有误码:若S为0,C在传输过程中没有误码;若S不为0,C在传输过程中有误码。当C中只有一个码元出现误码时,S在H中的位置与C中出现误码的位置一一对应,从而能确定误码位置、实现检错,再通过取反操作实现纠错;当C中有多个码元出现误码时,不能正确地检错。

交织技术原理简介

交织器与解交织器是成对出现的,交织器的作用是将数据序列按一定规律重新排列输出,解交织器的作用是将接收数据恢复为交织前的顺序,它是交织的逆操作。常见的交织器有随机交织器、规则交织器、伪随机交织器这三种类型。随机交织器和伪随机交织器性能较好,但硬件实现复杂度高,而规则交织器硬件实现容易,在工程应用中比较广泛。

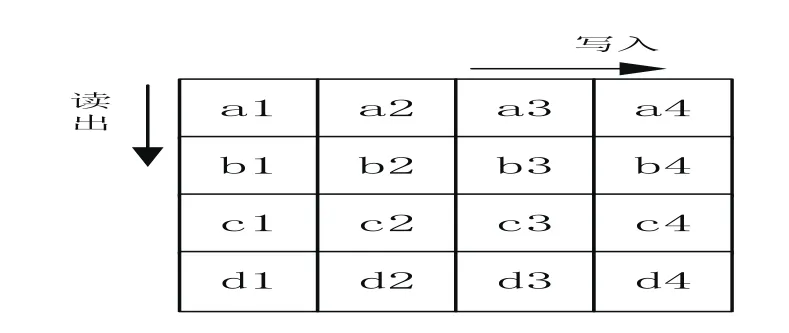

行列交织器是规则交织器中比较常见的一种,也最容易实现。以一个4行4列的行列交织器为例,其数据存取结构如下图1所示。

该交织过程可概括为两种操作:按行写入和按列读出。交织器输入数据的顺序为:{a1,a2,a3,a4,b1,b2,b3,b4, c1,c2,c3,c4,d1,d2,d3,d4},交织器输出数据的顺序为:{a1,b1,c1,d1,a2,b2,c2,d2,a3,b3,c3,d3,a4,b4,c4,d4}。从而实现数据顺序重新排列。解交织器的功能与交织器相反,它是交织的逆操作。

图1 4行4列交织器数据存取结构

在信道纠错系统中,采用交织器和解交织器的目的是将突发错误造成的成串误码分散开,化为随机误码,以便信道译码器进行纠错。假设上述交织器的输出数据中a2,b2,c2,d2连续4个码元都出错,经过解交织器后,这4个误码码元被分散到{a1,a2,a3,a4},{b1,b2,b3,b4},{c1,c2,c3,c4},{d1,d2,d3,d4}四组数据中,且误码码元a2,b2,c2,d2两两之间至少隔3个码元。若信道译码器的输入数据宽度为4比特,且能纠正1个误码码元,则a2,b2,c2,d2将在4次译码中被纠正,从而保证数据的正确性。

从交织和解交织原理可知,若信道纠错系统采用m行n列的行列交织器和输入数据宽度为Win的信道译码器,则能完全纠错的必要条件是Win≤n,且最大连续误码数Lmaxe≤m。因此,设计交织器和解交织器时,m和n的选择需要考虑信道译码器的输入格式和数据传输信道的实际情况。

功能实现与仿真结果

在Xilinx公司ISE软件中采用Verilog编程语言设计实现了一种最大输入数据位宽为16比特的纠错系统。考虑试飞数据的多样性,该系统支持的输入数据位宽为1到16比特,它由四个相同的处理单元组成,各处理单元分别读取输入数据的不同4位并行处理。

各处理单元工作情况与输入数据位宽有关。设输入数据为Data_I,其位宽为Win,若Win取1、2、3、4,仅第一个处理单元工作,其输入数据为Data_I[Win:1];若Win取5、6、7、8,第一和第二个处理单元工作,其输入数据分别为Data_I[4:1]和Data_I[Win:5];若Win取9、10、11、12,第一、第二和第三个处理单元工作,其输入数据分别为Data_I[4:1]、Data_I[8:5]和Data_I[Win:9];若Win取13、14、15、16,四个处理单元都工作,其输入数据分别为Data_I[4:1]、Data_I[8:5]、Data_I[12:9]和Data_I[Win:13]。若Win不是4的倍数,则对当前工作的最后一个处理单元输入数据高位补0,使其输入数据为4比特,最后进行数据还原时,再剔除掉填充的0。

(7,4)汉明码编译码简单,输入位宽为4比特,输出位宽为7比特,对应行列交织器和解交织器容易实现。因此,每个处理单元都采用(7,4)汉明码和7行7列的交织器与解交织器。每个处理单元的结构见下图2。

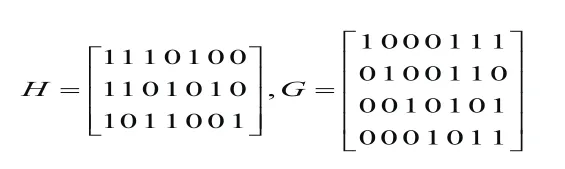

对于(7,4)汉明码而言,冗余码元长度R=3,编码码长N=7,信息序列长度K=4。校验因子S与误码位置关系见下表1。

表1 校验因子S与误码位置关系

从而校验矩阵H和生成矩阵G分别为:

图2 采用(7,4)汉明码和交织技术的数据处理单元

图3 系统功能仿真结果

按照(2)式则可得该(7,4)汉明码的全部编码码字C。

在发送端,根据输入数据位宽值提取其不同位数据,分别输入至各处理单元。在各处理单元中,测试数据以4比特(不足4比特的高位补0)格式输入到汉明编码器,输出的7比特汉明码字经过7行7列交织器后,以7比特格式在信道中传输。在接收端,接收的7比特数据先进行7行7列解交织,再进行汉明译码,输出为4比特的测试数据。再对当前工作的最后一个处理单元的输出数据进行剔0操作,然后按序合并各处理单元的输出数据,即得到正确完整的发送数据。

交织器和解交织器均为7行7列存取结构,数据缓存均采用内部存储器实现,在同一时钟下用计数器控制数据缓存的读写操作。此外,由于试飞数据的数据量并不固定,当数据个数不是7倍数时,为防止交织/解交织过程出现数据遗漏,必须进行边界处理。若发送数据的个数不是7倍数时,在试飞数据后以0补够为7的倍数;在接收端同样进行剔0操作。

在Mentor公司ModelSim软件中对该纠错系统进行功能仿真,以第一个处理单元为例,其仿真结果见图3。

由图3可知,Valid_D_I高电平有效后,汉明编码器依次输入(c)16,(f)16,(0)16,(5)16…,输出汉明码字依次为(97)10,(127)10,(0)10,(45)10…,再经过交织器后,依次输出(0b)16,(32)16,(6a)16,(6a)16,(32)16…。交织器每读取7个数据后对其存储器mem_jzout进行一次写操作,将交织后的数据缓存。再从写操作的下一时钟开始,依次输出该缓存数据,即为信道中传输的数据D_enout。

为验证系统的纠错性能,对D_enout的第一个数(0b)16和第九个数(1c)16都制造连续7位误码,分别成为(74)16和(63)16。接收端接收数据de_data的第一个数为误码数据(74)16,第九个数为误码数据(63)16,经过解交织及汉明译码后,该处理单元的输出数据为(c)16,(f)16,(0)16,(5)16…,与原输入数据一致。

可见,该纠错系统的单个处理单元对连续7位误码具有一定的纠错能力。因此,整个纠错系统对16比特以内数据的最多连续7位误码具有一定纠错能力。

结束语

试飞测试数据的正确性对航空设备研发与飞行安全至关重要。本文结合试飞测试数据传输的实际情况,提出了基于纠错码和交织技术的试飞测试数据抗误码方法。在ISE中设计实现了采用(7,4)汉明码和7行7列交织器的16比特纠错系统,并在ModelSim中进行功能仿真。仿真结果表明,对16比特以内数据的最多连续7位误码具有一定纠错能力。这对于设计高可靠性的试飞测试数据通信系统、提高数据传输可靠性具有重要的参考价值。

10.3969/j.issn.1001-8972.2015.09.006