面向MPSoC性能评估的高速缓存建模技术

2015-10-24修思文李彦哲晏荣杰严晓浪

修思文,李彦哲,黄 凯,马 德,晏荣杰,严晓浪

(1.浙江大学超大规模集成电路研究所,浙江杭州310027;2.杭州电子科技大学微电子CAD所,浙江杭州310018;3.中国科学院软件研究所,北京100080)

面向MPSoC性能评估的高速缓存建模技术

修思文1,李彦哲1,黄 凯1,马 德2,晏荣杰3,严晓浪1

(1.浙江大学超大规模集成电路研究所,浙江杭州310027;2.杭州电子科技大学微电子CAD所,浙江杭州310018;3.中国科学院软件研究所,北京100080)

分析现有的面向MPSoC性能评估的高速缓存建模技术的缺点,提出用于本机模拟的静态分析和动态标注相结合的缓存建模技术.该技术采用GCC剖析,避免了命中判断时标签比较,扩展了缓存更新的粒度.建立准确的指令和各类型变量在目标平台的地址映射表,提高了仿真速度和评估的准确性.该技术支持对多级缓存的建模,扩展了对多处理器平台的支持.实验结果表明,该技术的评估速度和准确性均优于现有技术.

MPSoC性能评估;高速缓存建模;本机模拟;GCC剖析;静态分析;动态标注;多级缓存

随着嵌入式领域应用需求的不断提高,多核系统芯片(MPSoC)的体系结构和设计规模变得愈加庞大与复杂,迫切需要高效、准确的性能评估技术,以实现快速的软硬件架构探索[1-2],缩短产品的上市时间.MPSoC性能评估技术已逐渐成为电子系统级设计领域的前沿和热点[3].为了使性能评估足够精准,必须考虑各系统组件的影响.其中,高速缓存(cache,以下简称为缓存)尤为重要,对整个系统性能的影响很大.构建高效、准确的缓存模型是MPSoC性能评估的核心环节之一,可为MPSoC软硬件架构系统级设计提供有效的方法学和技术基础.

近年来,学术界提出了众多的缓存建模技术,主要分为静态分析和动态仿真2类.静态分析首先建立缓存数学模型,然后遍历分析软件代码所有可能的控制路径得到最坏的性能结果[4-6].静态分析的方法常用于实时系统,利用计算代替模拟,具有快速、全面的优点;但评估结果过于悲观,易导致性能冗余,造成硬件资源浪费.与静态分析相比,动态仿真可以获得更加准确的评估结果,按模型层次和仿真方法来区分,主要分为指令集仿真器(instruction set simulator,ISS)和本机模拟(native simulation).基于ISS的评估技术[7-9]以目标处理器仿真模型为基础,对汇编指令逐条解析模拟程序实际执行过程,采用细节的缓存模型,虽然可以反映系统精确的执行过程和时间,但由于其极慢的速度难以胜任早期的性能评估.

为了达到复杂度、仿真速度和精度的最佳折中,学术界提出众多基于本机模拟的缓存建模技术[10-15].本机模拟以应用程序在主机(基于x86架构CPU的服务器或工作站)的执行过程和结果为研究对象,分析推算出目标平台执行结果,避免对目标平台执行过程进行复杂的模拟.与ISS相比,本机模拟具有仿真速率快、平台构建简单、可移植性强、便于调试等诸多优势.目前,基于本机模拟的缓存建模技术存在一些局限:1)常用源代码标注的方法,以基本块(basic block)为单位进行标注,粒度较细,导致仿真过程中与缓存模型频繁交互[10-12],影响仿真的速度;2)缓存模型的命中检查主要基于标签比较(Tag-Search)[13],进一步制约了仿真的速度;3)主机平台与目标平台指令集和地址空间的差异导致本机模拟中变量地址分配与实际地址可能不同,给数据缓存模型引入误差[14];4)主要集中在单处理器架构,且几乎没有基于本机模拟的多级缓存建模技术[16-17].

为了解决以上问题,本文提出静态分析和动态标注相结合的方法来建立基于本机模拟的缓存模型.该方法采用GCC剖析(profiling)技术,避免对源代码的大量修改;与文献[16]相比,完全避免了缓存模型的标签比较,提高了仿真速度;以“段落”为基本单位更新缓存状态,扩展了缓存更新的粒度,降低应用进程与缓存模型的交互频率,进一步提高了仿真速度;以动态仿真结果和目标平台汇编代码为静态分析对象,建立指令和各类型变量在目标平台的地址映射表,提高评估的准确性;采用线上更新和离线分析相结合的方法,支持对多处理器平台多级缓存的建模.

1 GCC剖析技术

为了结合动态仿真和静态分析的优势,采用Ma等[17]提出的GCC剖析技术来收集、分析本机模拟过程中的程序执行情况.图1展示了利用本机模拟的GCC剖析技术来配置、更新缓存模型的三大步骤.

1)根据评估对象的架构信息配置缓存模型;静态分析应用软件源代码的控制语句,进行段落划分并插入控制缓存状态更新的应用程序编程接口函数(以下简称为缓存API).

2)分别采用主机和目标处理器编译工具对待评估源码进行编译,生成主机平台的应用和缓存状态分析可执行代码以及目标平台反汇编代码.编译时,通过开启Gcov[18]参数,生成该应用的.gcno文件,包含了GCC剖析所需要的信息.

3)对可执行代码进行动态仿真,获得代码覆盖率及动态变量相对地址;通过静态分析代码覆盖率文件(.gcov文件)和目标平台反汇编代码,获得应用程序在目标平台的指令执行流程、次数、存储器访问地址等信息;根据这些信息,实时调用缓存API更新各缓存模型的状态,并统计命中缺失情况给出性能结果.

图1 基于GCC剖析技术的缓存建模流程Fig.1 GCC profiling based cache modeling flow

2 缓存模型

传统缓存模型[13]一般采用标签比较的方法进行缓存块索引,如图2所示,以2路组相连缓存为例.当处理器对缓存发起访问时,用低位地址对应的组索引字段(index)找到映射的组(set),然后用高位地址与组内所有缓存行(line)的标签字段(tag)比较判断是否命中.采用该方法可知,缓存的关联度将严重制约仿真速度,组内缓存块的数目越多,仿真速度越慢;当处理器数目增加时,情况更糟.

图2 基于标签比较的缓存模型Fig.2 Tag-search based cache model

为了解决传统缓存模型对仿真速率的限制,避免耗时的标签比较,利用主机内存资源丰富和缓存命中率远高于缺失率的特点进行缓存建模.以采用LRU替换算法的数据缓存为例进行说明.如图3所示,采用以下2组数据结构.

addr_block记录所有数据段的可缓存地址块在缓存中的状态(有效位、脏位等)和缓存中所在的路(way,只用于LRU等基于访问次数的缓存替换算法).其中,将整个数据段可缓存的地址按缓存行的大小进行划分,每一块称为地址块(以下简称为block).

cache_line和传统的缓存模型类似,记录缓存行的标签字段和访问次数(count,只用于基于访问次数的缓存替换算法,如LRU算法).

当某个可缓存地址被访问时,首先查询block_ status[block].如果缓存命中,则根据set和block_ status[block].way指定的路更新line_status[{set, way}].count信息.若缓存缺失,则遍历line_status[{set,*}]中该组的所有路,得到各路的line_status.count和line_status.tag.各路的line_status.tag连上set即为各路的block,然后根据block_status[block]和对应的line_status.count以决定分配到哪路中.最后,更新相应的line_status和block_ status,若存在对下一级存储器的访问(一级缓存缺失),则记录在文件中.

图3 基于地址块索引的缓存模型Fig.3 Tag-search based cache model

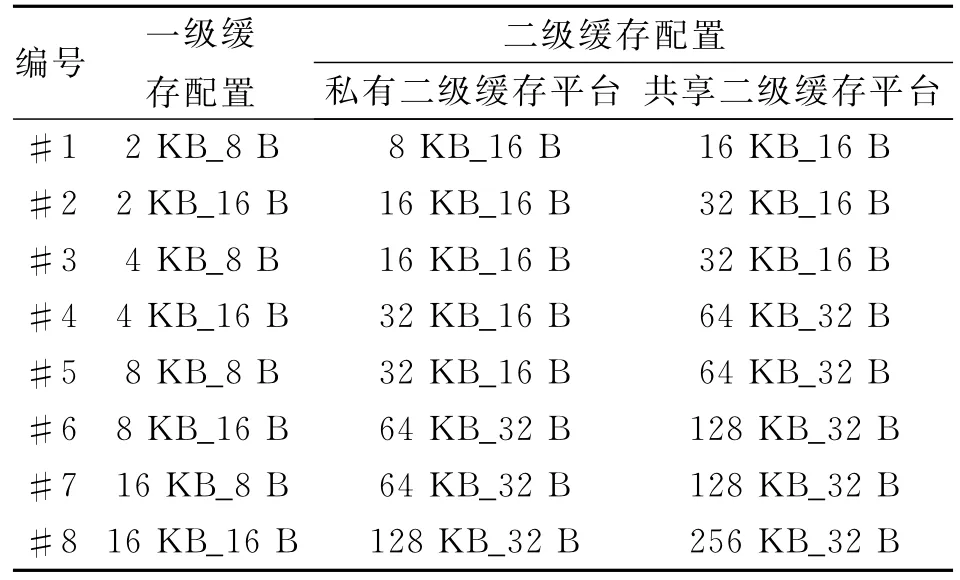

虽然本文提出的模型对内存的消耗有所增加,但对于配备GB级内存的服务器是可以忽略的.由于line_status数组也存在于传统的基于标签比较的缓存模型中(本文省掉了其中的状态位),额外的存储开销即为block_status数组.对于32位处理器,地址的最大范围为232,考虑一个缓存行大小为2xbyte、状态位为y bit的2n路组相连一级数据缓存(对于嵌入式处理器,x一般为5,y和n一般为2),block_status数组的存储开销(单位:MB)为

即使是最极端的情况,所有的地址空间都被覆盖,额外的存储开销远小于现代服务器的一般内存容量.

3 基于段落的缓存更新机制

图4 基本块、控制块与段Fig.4 Basic block,control block and segment

软件代码一般按照顺序、选择和迭代3种结构进行组织[11].在传统评估方法中,以选择或者迭代语句为边界,将代码划分为只含有顺序语句的基本块,如图4所示,在仿真过程中以基本块为单位对缓存状态进行更新.

为了进一步提高仿真效率,将基本块按类型特点和一定规则合并成“段落”,以段落为基本单位进行缓存状态更新.对GCC剖析得到的代码覆盖率文件进行分析,以还原段落内代码执行流程.按照控制语句的特点,可以将控制类型分为2类:显式控制和隐式控制.将能够通过代码覆盖率文件还原代码执行流程的控制块称为显式控制块(如for等循环语句),反之称为隐式控制块(如if-else等选择语句).按照以上原则可知,C/C++控制语句分类结果如表1所示.

表1 显式、隐式控制块分类Tab.1 Divisions of explicit and implicit control blocks

结合本机模拟代码覆盖率文件,显式控制块的执行流程能够通过静态分析还原,可以将显式控制块合并到一个段落内.对于隐式控制块,虽然执行流程不能通过静态分析还原,但如果它的地址空间小于对应的缓存,则可以推断它只会在首次执行过程中发生缓存缺失,随后的执行过程中均会命中缓存.

代码段落划分的基本原则如下:连续的只包含显示控制块的段落大小没有限制;包含隐式控制块的段落不大于缓存的大小.对于一个隐式控制块,它可以被合并到一个已存在的段落,但前提是合并后的段落小于缓存的大小;否则,若该隐式控制块不大于缓存的大小,则将为其创建一个新的段落,否则为其中的每个基本块创建一个段落.

4 指令及变量地址追踪

为了能够准确观察本机模拟过程中的缓存访问情况,分别采用2个编译器对待评估应用软件源代码进行编译:通过主机GCC编译产生用于本机模拟和覆盖率统计的可执行代码;通过交叉编译和反汇编得到用于静态分析的反汇编代码.如图5所示,通过分析目标平台汇编代码获得源代码与指令间的对应关系以及这些指令在目标平台的真正地址(p2_ sw.asm中的PC).

图5 指令地址分析Fig.5 Instruction addresses analyzing

不同于指令地址,数据变量地址与程序动态执行情况紧密相关,很难直接得到.为此,采用静态分析与动态仿真结合方法解决该问题.变量地址追踪的方法和流程如图6所示.根据ELF标准可知,全局变量和静态变量由编译器分配,主要分配在data、rodata和bss段,本文通过静态分析Objdump工具产生的反汇编文件获得;局部变量和动态变量是根据程序执行过程分别从栈(stack)和堆(heap)中动态分配的,不可能直接通过静态分析得到这些变量的绝对地址.由于堆很复杂,几乎没有性能评估工作解决堆的问题.为此,采用在GDB调试器脚本中插入标注函数的方法来跟踪局部变量和动态变量的偏移地址.在GDB调试器脚本定义局部变量的地方或动态数据进行存储器分配的地方设置断点,让调试器把这些变量的地址打印出来,建立堆栈变量的地址表.虽然主机和目标平台的绝对地址不同,它们维护变量的偏移地址是基本相同的,前提是变量尺寸相同.因此,需要直接修改源代码以转换变量的类型,例如,若long类型在主机上是64位,而在目标处理器上是32位,则long类型的变量应该被转换成int类型.基于本机模拟中标注函数的打印结果,根据下面2个公式计算目标平台的地址:

图6 变量地址追踪流程Fig.6 Address tracing flow of variables

式中:LAddrt、DAddrt、SPt和Heapt分别表示目标平台的局部变量地址、动态变量地址、栈指针和堆的基地址;LAddrh、DAddrh、SPh和Heaph分别表示主机上相对应的变量.

除了变量地址表,本文还根据源代码每条语句的存储器访问情况建立一个存储器访问表,如图7所示.在本机模拟之前,静态分析每条语句以找到所有的变量操作,每个这样的操作都指示一个可缓存的读/写访问.写访问发生的条件如下:一个变量出现在常规赋值表达式(=、+=、-=等)左边;自操作符(++或--等);调用函数时压栈.读访问发生的条件如下:变量在赋值表达式的左边;比较表达式(>、< ═══、 等);函数出栈.另外,一些系统变量(诸如fp、ip、lr和pc等)应该在发生函数调用和退出时分别被保留和恢复.

图7 存储器访问表Fig.7 Memory access table

5 多级缓存建模

以二级缓存为例来说明多级缓存建模技术.常用的二级缓存架构主要分为2种:私有二级缓存与共享二级缓存,如图8所示.

图8 私有二级缓存与共享二级缓存建模Fig.8 Private L2 cache and shared L2 cache modeling

5.1 私有二级缓存建模

私有二级缓存和处理器直接相连,且不存在处理器间的缓存共享,本文采用在线(on-line)更新的策略对私有二级缓存进行建模.二级缓存的更新通常是由一级缓存的操作(缺失、写回等)引起的,当进行性能评估时,对于每一条或每一段落指令,只需依次对各级缓存模型进行更新.二级缓存的缓存行有可能大于一级缓存,对于同一地址,各级缓存的地址块索引字段一般不同;因此,各级缓存的地址块状态是分开记录的.

5.2 共享二级缓存建模

共享二级缓存建模的关键是要综合考虑各个处理器对二级缓存访问情况,为此,采用离线(offline)分析的策略对共享二级缓存进行建模.前文提到,在对各处理器进行一级缓存建模时,引发二级缓存访问的操作会被按次序记录到日志文件中,格式为:“访问时刻(cycle),操作类型(type),二级缓存地址块索引字段(block)”.其中,访问时刻可以根据性能评估的累计结果得到;对于访问二级缓存的操作,在本机模拟分析时暂不计算二级缓存及共享存储器的访问延时,最后在离线分析时进行修正.离线分析的优点是避免缓存模型间的通信,对速度影响不大;缺点是对于包含(inclusive)类型的共享二级缓存,替换操作可能会引起对一级缓存的反向无效(backward invalidation)操作,这是目前无法模拟的,会降低准确度.

离线分析算法如下.

本文将各一级缓存建模时生成的日志文件转化为数组.其中,冲突模型模拟共享二级缓存对并发操作的仲裁;反馈模型给仲裁成功者返回二级缓存和主存储器的访问时间,给仲裁失败者返回延迟的时间.经过离线分析,得到各处理器访问共享二级缓存及主存储器的附加延时以及共享二级缓存的访问统计.

结合在线更新和离线分析的建模方法,可以对各种多级缓存架构进行建模.

6 实验与分析

为了验证本文技术的高效性和准确性,采用相同测试基准、针对相同的目标平台进行性能评估,与一些现有的缓存建模技术进行对比.为了进一步分析本文技术的特点,在多种缓存配置模式下对更复杂的应用进行性能评估实验.在实验中,采用的主机平台的配置如下:2颗工作于3.47 GHz的Intel Xeon X5690处理器,工作于1 333 MHz的40 GB内存,采用Cent OS4.8-x64操作系统.

6.1 与现有技术的对比

本文实现了目前最先进的3个基于源代码标注的技术和本文技术进行对比.其中,Schnerr等[13]采用基于标签比较的缓存查找技术;Castillo等[11]在Schnerr等[13]提出的技术基础上减少了标签比较,以基本块的粒度更新指令缓存模型;Posadas等[10]减少了标签比较,以每次存储器访问的粒度更新数据缓存模型.

实验采用小型测试基准Bubble、Hanoi和Factorial作为待评估程序,目标平台处理器为ARM920T[19],配备了16 KB、缓存行大小为32 byte、64路组相连的数据/指令缓存.

比较各种缓存建模技术的准确性,表2列出了ISS仿真、源代码标注技术[10]和本文的技术对数据缓存缺失次数评估的结果.其中,基于ARM920T ISS的仿真结果可以被认为是精准的.

表2 数据缓存缺失次数评估Tab.2 Data cache miss estimation of different techniques

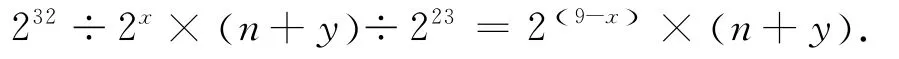

图9显示了源代码标注技术和本文技术相对于ISS仿真的误差比较情况.图中,er为相对误差.可见,对于Bubble系列程序,源代码标注技术的准确度高于本文技术.原因是本文的缓存模型只在一个段落执行后才被更新,且分支的执行流程是静态分析得到的,可能和真实情况不同.对于Posadas等[10]提出的源代码标注技术,每当发生存储器访问时,缓存模型就要和标注程序通信.对于Hanoi和Factorial程序,源代码标注技术的误差高达15.79%和33.33%,而本文技术的误差只有5.26%和5.60%.原因是这2个程序中存在大量的函数调用,因而引起很多对堆栈的操作,而本文很好地考虑到了和函数调用相关的系统变量及局部变量等,这些是Posadas等[10]所忽略的.可见,针对存在大量、复杂函数调用的程序,采用本文技术评估的准确度优势明显.这种类型的程序往往是MPSoC性能评估的重点研究对象.

图9 数据缓存建模相对误差比较Fig.9 Relative error comparison between different techniques for data cache modeling

如图10、11所示为3种技术的建模速度v对比情况.其中,建模速度用MIPS(million instruction per second)来衡量,它表示每秒钟可以模拟的目标平台指令的百万条数.从图11、12可以看出,基于标签比较的技术是最慢的;对于指令缓存建模速度,本文基于段落更新的技术是基于基本块更新的技术的2.0~3.0倍;对于数据缓存建模速度,本文技术是基于逐条指令更新的技术的1.5~3.0倍.实验所用测试基准的特点如下:它们的指令地址范围均小于指令缓存的大小,且变量的地址范围均小于数据缓存的大小.对于本文提出的基于段落的缓存更新技术,整个程序都可以看作是一个段落,指令和数据缓存模型都在程序执行完毕后才被更新,应用程序和缓存模型之间的通信开销远低于现有技术,所以建模速度快于现有技术.

6.2 不同缓存架构的建模分析

选取适合多核多线程评估的EEMBC Multibench[20]中有代表性的3个应用对不同缓存架构进行性能评估.其中,md5程序计算多数据流的MD5校验和,数据并行度较高,核间通信较少,一级缓存命中率较高;rotate程序处理一系列二进制图像,将二进制图像旋转90°、180°和270°,数据缓存命中率较低,核间共享数据较多;x264程序对图像进行编码,程序较复杂,数据量较大,核间通信量较多.程序的核间通信是利用通信邮箱(mailbox),通过消息传递的显示方式实现的.

图10 指令缓存建模速度比较Fig.10 Speed comparison for instruction cache modeling

图11 数据缓存建模速度比较Fig.11 Speed comparison for data cache modeling

图12 数据缓存建模速度比较Fig.12 Speed comparison among different techniques for data cache modeling

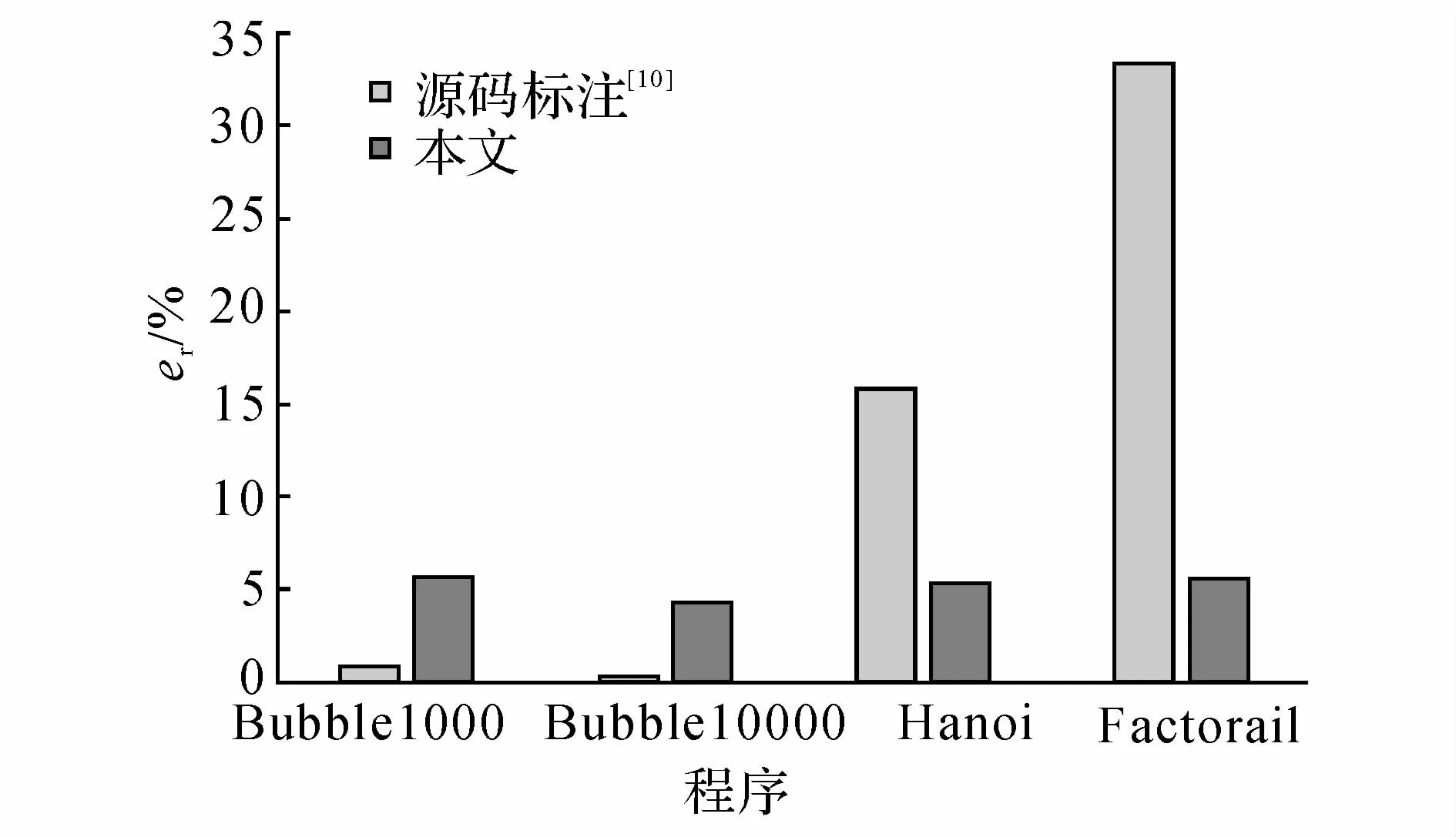

选取的待评估的2个目标平台如图12所示,图12中省略了核间通信邮箱、定时器、中断控制器等一些外设.这2个平台主要由4个CK810处理器[21]、AXI3总线、二级缓存(NI/NE)和1个DDR2类型的共享存储器组成,不同之处只在于二级缓存的位置.实验中缓存架构的配置情况如表3所示,从配置#1到配置#8,一级缓存的大小和缓存块大小交替增加,二级缓存的大小间隔增加.以配置#1的2KB_8B为例,它表示缓存大小为2 KB,缓存行大小为8-byte.其中,各级缓存均采用写回、写分配策略;一级缓存为4路组相连,采用LRU替换算法;二级缓存为8路组相连,采用随机替换算法.在FPGA上分别实现了各种配置,把程序通过线程划分分配到各处理器上运行,利用硬件计数器统计各缓存的访问情况,最后与评估结果对比.

表3 缓存架构配置Tab.3 Cache architecture schemes

图13(a)~(c)显示了在表3配置下,采用本文的建模技术统计各程序的缓存缺失次数与真实情况(FPGA)的相对误差.可见,本文提出的缓存建模技术准确度较高,可以对MPSoC进行快速、准确的性能评估.

指令缓存建模的准确度是最高的,基本接近于真实情况.由于指令的地址是可以准确获得的,指令缓存建模的误差仅由对指令流的分析不准所引入.对于不同程序,相对误差和程序的复杂度(x264>md5>rotate)成正相关;对于同一程序,随着指令缓存大小和缓存行容量的增大(命中率升高),指令流的不准确性被逐渐掩盖,相对误差呈减小的趋势.

数据缓存建模的准确度最低,因为数据缓存建模引入误差的原因不仅有指令流的不准,还有地址分析的不准.对于不同程序,相对误差与程序复杂度、数据量成正相关;对于同一程序,随着数据缓存的增大,开始时相对误差降低,随后趋向稳定,因为此时地址分析误差已占主导.数据缓存建模的相对误差都在6%以内,比较准确.为了进一步研究数据缓存建模的准确度,将数据缓存固定为16 KB_32 B,改变路的数目,相对误差如图13(d)所示.可见,随着路数的增加,相对误差呈上升趋势,但仍在可控的范围内.原因是路数越多,数据缓存更新和实际情况的差异对替换算法执行的影响越大,从而进一步放大误差.

私有二级缓存建模的相对误差变化情况和数据缓存相仿.原因是私有二级缓存较大,掩盖了一部分指令流不准的误差,因此相对误差都低于数据缓存.至于共享二级缓存,相对误差大于私有二级缓存,小于数据缓存,且rotate和x264的相对误差较大.原因是rotate和x264的共享变量较多,从而使冲突/反馈模型的误差占了主导.为了进一步研究共享二级缓存建模的准确度,将一级缓存固定为16 KB_32 B,改变处理器的个数,相应的共享二级缓存配置为(16×2×处理器个数)KB_32 B,相对误差如图13(e)所示.可见,随着处理器个数的增加,共享变量较多的x264和rotate的相对误差的上升趋势较明显,但都在可控的范围内.原因是随着处理器个数的增加,对AXI3总线行为的模拟将愈加困难,即冲突/反馈模型的误差将更大地影响对共享二级缓存的离线分析.

图13 不同缓存配置下相对误差统计Fig.13 Relative error statistics of different cache architectures

7 结 语

本文提出一种高效、准确的面向MPSoC性能评估的高速缓存建模技术,支持对多处理器平台多级缓存的建模.实验结果表明,与现有技术相比,本文提出的技术建模速度更快、对复杂程序的评估更精准;对于多级缓存架构,采用本文技术建模的准确度很高.

今后,笔者将完善对共享二级缓存的建模,重点研究冲突/反馈模型;笔者还将考虑支持高速缓存一致性的建模.

[1]JERRAYA A,WOLF W.Multiprocessor systems-onchips[M].Amsterdam:Elsevier,2004.

[2]Martin G.Overview of the MPSoC design challenge[C]//Design Automation Conference.San Francisco:ACM/IEEE,2006:274- 279.

[3]POSADAS H,HERRERA F,SÁNCHEZ P,et al.System-level performance analysis in SystemC[C]//Design,Automation and Test in Europe Conference and Exhibition.Paris:IEEE,2004:378- 383.

[4]KIRNER R,SCHOEBERL M.Modeling the function cache for worst-case execution time analysis[C]//Design Automation Conference.San Diego:ACM/IEEE, 2007:471- 476.

[5]SONG F,MOORE S,DONGARRA J.L2 cache modeling for scientific applications on chip multi-processors[C]//International Conference on Parallel Processing. Xi’an:IEEE,2007:51.

[6]LI Y T S,MALIK S,WOLFE A.Cache modeling for real-time software:beyond direct mapped instruction caches[C]//Real-Time Systems Symposium.Los Alamitos:IEEE,1996:254- 263.

[7]BENINI L,BERTOZZI D,BOGLIOLO A,et al.Mparm:exploring the multi-processor soc design space with system[J].Journal of VLSISignal Processing Systems for Signal,Image and Video Technology,2005, 41(2):169- 182.

[8]EDLER J,HILL M D.Dinero IV trace-driven uniprocessor cache simulator[EB/OL].[2014-05-23].http://pages.cs.wisc.edu/~markhill/DineroIV.

[9]BINKERT N,BECKMANN B,BLACK G,et al.The gem5 simulator[J].ACM SIGARCH Computer Architecture News,2011,39(2):1- 7.

[10]POSADAS H,DÍAZ L,VILLAR E.Fast data-cache modeling for native co-simulation[C]//ASP-DAC. Yokohama:IEEE,2011:425- 430.

[11]CASTILLO J,POSADAS H,VILLAR E,et al.Fast instruction cache modeling for approximate timed HW/SW co-simulation[C]//Proceedings of the 20th Symposium on Great Lakes Symposium on VLSI.New York:ACM,2010:191- 196.

[12]WANG Z,HENKEL J.Fast and accurate cache modeling in source-level simulation of embedded software[C]//Proceedings of the Conference on Design,Automation and Test in Europe.Grenoble:IEEE,2013:587- 592.

[13]SCHNERR J,BRINGMANN O,VIEHL A,et al.High-performance timing simulation of embedded software[C]//Design Automation Conference.Anaheim:IEEE,2008:290- 295.

[14]KIRCHSTEIGER C M,SCHWEITZER H,TRUMMER C,et al.A software performance simulation methodology for rapid system architecture exploration[C]//15th IEEE International Conference on Electronics,Circuits and Systems.Julien's:IEEE,2008:494- 497.

[15]GERIN P,HAMAYUN M M,PÉTROT F.Native MPSoC co-simulation environment for software performance estimation[C]//Proceedings of the 7th IEEE/ACM International Conference on Hardware/Software Codesign and System Synthesis.New York:ACM,2009:403- 412.

[16]YAN R,MA D,HUANG K,et al.Annotation and analysis combined cache modeling for native simulation[C]//Design Automation Conference(ASP-DAC). Singapore:IEEE,2014:406- 411.

[17]MA D,YAN R,HUANG K,et al.Performance estimation techniques with MPSoC transaction-accurate models[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2013,32(12):1920- 1933.

[18]GNU.Gcov-a test coverage program[EB/OL].[2014-05-23].http://gcc.gnu.org/onlinedocs/gcc/Gcov.html.

[19]ARM LTD.ARM920T technical reference manual[EB/OL].[2014-05-23].http://infocenter.arm.com/help/topic/com.arm.doc.ddi0151c/ARM920T_ TRM1_S.pdf.

[20]Embedded Microprocessor Benchmark Consortium.MultiBenchTM1.0 Benchmark software[EB/OL].[2014-05-23].http://www.eembc.org/benchmark/multi_sl.php.

[21]C-SKY MICROSYSTEMS CO.,LTD.CK810 introduction[EB/OL].[2014-05-23].http://www.csky.com/product.php?typeid=103.

Cache modeling for MPSoC performance estimation

XIU Si-wen1,LI Yan-zhe1,HUANG Kai1,MA De2, YAN Rong-jie3,YAN Xiao-lang1

(1.Institute of VLSI Design,Zhejiang University,Hangzhou 310027,China;2.Microelectronics CAD Center,Hangzhou Dianzi University,Hangzhou 310018,China;3.Institute of Software,Chinese Academy of Sciences,Beijing 100080,China)

The disadvantages of existing cache modeling techniques for MPSoC performance estimation were analyzed.An static analysis and dynamic annotation combined cache modeling technique for native simulation was proposed.The technique employs GCC profiling,avoids tag-search for hit/miss judgment,and coarsens the granularity of cache updating.An accurate address mapping table for instruction and all types of data variables was established,which improves both simulation speed and estimation accuracy.Multilevel cache modeling was considered,which extends support for multi-processor platform.Experimental results show that the proposed technique can significantly reduce the simulation time and improve the accuracy of estimation result compared with existing techniques.

MPSoC performance estimation;cache modeling;native simulation;GCC profiling;static analysis;dynamic annotation;multi-level cache

10.3785/j.issn.1008-973X.2015.07.023

TN 47

A

1008- 973X(2015)07- 1367- 09

2014- 05- 23. 浙江大学学报(工学版)网址:www.journals.zju.edu.cn/eng

中央高校基本科研业务费专项资金资助项目(2013QNA5008);国家科技重大专项基金资助项目(2009ZX01030-001-002);国家自然科学基金资助项目(61100074).

修思文(1985—),男,博士生,从事多核处理器设计的研究.ORCID:0000-0003-0400-8037.E-mail:xiusw@vlsi.zju.edu.cn

黄凯,男,副教授.ORCID:0000-0002-5034-7171.E-mail:huangk@vlsi.zju.edu.cn