基于OV9712的串行器解串器视频编码方案

2015-10-22张宝龙王靖云郭海成

张宝龙,李 丹,王靖云,郭海成

(1.天津科技大学电子信息与自动化学院,天津300222;

2.香港科技大学显示技术研究中心,香港九龙)

基于OV9712的串行器解串器视频编码方案

张宝龙1,李 丹1,王靖云1,郭海成2

(1.天津科技大学电子信息与自动化学院,天津300222;

2.香港科技大学显示技术研究中心,香港九龙)

以OV9712作为图像传感器,进行高清行车记录仪摄像模组设计.为了提高摄像模组中的高清数字信号传输速率,进而提升输出图像的清晰度,本文还采用了美国TI公司生产的集成芯片组DS90UB913Q及DS90UB914Q作为串行器和解串器,对高清数字信号进行LVDS差分信号编码及解码,最终实现了通过LVDS对差分信号数据进行全双工高速通信的功能.实验表明,该芯片组的应用,大幅提高了远距离高清图像数据传输的质量,使车载行车记录仪图像更为清晰.

OV9712;DS90UB913Q/DS90UB914Q;FPD-Link III;全双工通信

1 引 言

随着汽车电子设计技术的不断更新与提升,各种百万像素照相机的行车记录仪设计方案层出不穷.传统的行车记录仪多采用MCU直接配置CMOS图像传感器,占用了大量的MCU资源,限制了高性能行车记录仪的实现,而且数据并行传输输出的图像也不清晰[1-2].

市面上销售的行车记录仪大部分基于MCU直接配置CMOS方案设计,因此普遍存在受限于传输速率而造成的图像清晰度不足、色彩辨识力不理想等缺点.与这些行车记录仪相比较,美国TI公司提出一种串行器解串器DS90UB913Q/ 914Q:OV9712 3×106pixel照相机FPD-Link III接口设计,该设计中传感器选用Ominivision的OV9712.实现高速接口以及用于差分对LVDS信号数据的串行传输.本设计基于图像传感器OV9712和DS90UB913Q/914Q芯片组,实现了高速率的数据传输,像素时钟稳定,图像清晰稳定.有利于行车记录仪实现高清晰度、高色彩质量和稳定的行车图像记录.

2 DS90UB913Q/914Q系统架构及特点

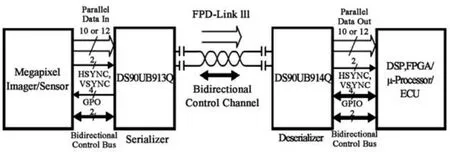

系统分为两部分(如图1):第1部分包括传感器与串行器DS90UB913Q,第2部分包括解串器DS90UB914Q与控制它的MCU.这两部分之间通过FPD-Link III接口相连.

系统的工作原理:首先OV9712输出RGB的数据与串行器DS90UB913Q相连,串行器把并行的数据转化为一对LVDS差分对信号作为数据的发送端[2],然后通过双绞线或者屏蔽线传送数据进而被解串器DS90UB914Q接收端接收,然后解串器输出10/12位并行数据和同步信号与PCLK,通过MCU控制这些信号.

图1 系统总体结构图Fig.1 Overall structure of the system

通过串行差分信号视频的连接,用双向控制总线(I2C),传输全双工高速视频数据(10/12位的并行数据,两个SYNC位和PCLK).所以需要单片机产生I2C来配置DS90UB914Q的寄存器继而配置串行器DS90UB913Q的寄存器与CMOS的寄存器来进行软件的调试[3-4].

本方案选用飞思卡尔公司的单片机MC9S08DZ60来产生I2C信号对解串器进行寄存器的读写从而对系统进行调试.通过串行器DS90UB913Q来编程传感器.

本系统的特色:

(1)DS90UB913Q提供FPD-Link III接口用于差分对上数据发送的双向控制通路,具备连续低延迟、可稳定工作在高达100 MHz的频率下以及驱动线路长等优点,十分适用于汽车相关视频系统,尤其是汽车前端相机的数据处理.

(2)嵌入式时钟技术使用单一差分对信息披露的全双工通信,双向控制信道I2C实现信息的双向传输.通过解决并行数据和串行时钟路径之间的偏差问题,大大降低了系统成本,减少数据路径,从而降低了PCB层的宽度和电缆连接器的尺寸.此外,解串器输入补偿提供长距离传输所造成的损失,进行自适应均衡.实现编码和解码的直流内部平衡,支持交流耦合互连.串行器可用一个32引脚LLP封装,在设备的解决方案中解串器采用48引脚LLP封装.

本系统的关键技术指标:

PCLK时钟支持10~100 MHz的频率范围,具备互连的单差分对儿,10位数据时像素时钟频率可以达到100 MHz,12位数据时像素时钟频率可以达到75 MHz,连续的低延迟双向接口通道I2C,其频率可达400 KHz.支持2∶1多路复用器,系统时钟具有直流编码平衡,支持交流互连耦合,最长可以在25 m的屏蔽双绞线上通讯,具有4个专用的通用输入(GPI)/输出(GPO),LOCK输出报告和高速BIST诊断功能来对结构的完整性进行验证,终端电阻是集成的,1.8 V单电源供电,工作温度范围-40℃~+105℃.(5 mm×5 mm)小型串行器,接收端没有参考时钟,自适应接收均衡,EMC下降,DES接收交错输出[5-6].

3 系统的总体设计

3.1OV9712与DS90UB913Q的设计

3.1.1电源模块

系统的总电源为5 V,通过LMR14203电源芯片先进行滤波处理转化为4 V,然后通过TI公司的TLV70015、TLV70033、TLV70018转化为1.5 V,3.3 V,1.8 V分别给OV9712以及DS90UB913Q供电.如图2所示.

图2 串行器与传感器电源结构图Fig.2 Power structure of serializer and sensor

3.1.2时钟模块

如图3所示,本系统首先通过一个有源晶振SIT9201产生外部时钟连接至串行器DS90UB913Q的GPIO3引脚作为时钟输入,然后GPIO2引脚作为时钟的输出连接至传感器OV9712的输入时钟XCLK,继而输出时钟信号PCLK与串行器的PCLK相连作为发送数据的时钟,在传感器输出10位并行数据的模式下,PCLK的时钟频率理论上是外部输入时钟频率的一半.

3.1.3DS90UB913Q各个引脚功能的设计

DS90UB913Q的MODE引脚在设计时需要注意要连接一个下拉电阻,在本系统中由于采用的是外部晶振,所以根据串行器的datasheet[7]下拉电阻阻值为4.7Ω.

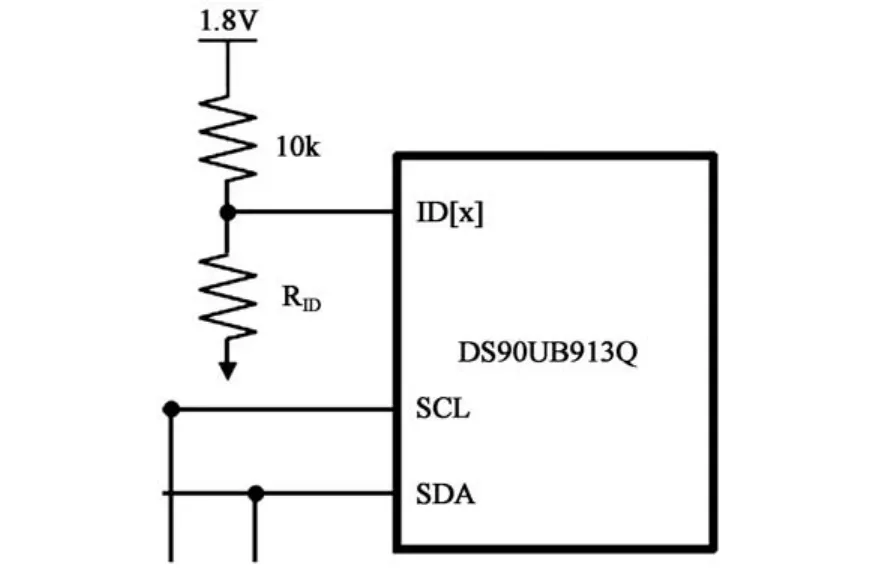

DS90UB913Q的SCL与SDA引脚设计时需要加上上拉电阻,如图4所示.

DS90UB913Q的ID[x]引脚需要加上1个10 kΩ的上拉电阻与1个0 kΩ的下拉电阻,如图5所示.

综上所述,传感器OV9712与串行器DS90UB913Q部分的设计基本就是这样,其他部分比如模拟地与数字地之间通过0欧电阻或者磁珠连接就行了.

图3 串行器与传感器的时钟模块Fig.3 Clock module of serializer and the sensor

图4 DS90UB913Q MODE电阻以及I2C上拉电阻配置Fig.4 DS90UB913Q mode resistor and I2C pull up resistors configuration

3.2DS90UB914Q与MCU部分的设计

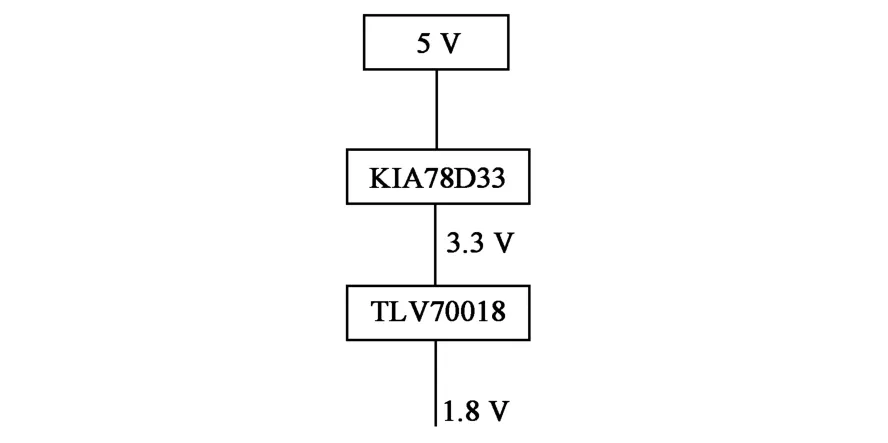

3.2.1电源模块

由于本系统选用的单片机MC9S08DZ60是3.3 V供电的,而且需要一定的驱动电流,所以5 V电源通过KIA78D33转化为3.3 V给单片机供电,3.3 V通过TLV70018转化为1.8 V给DS90UB014供电,如图6所示.

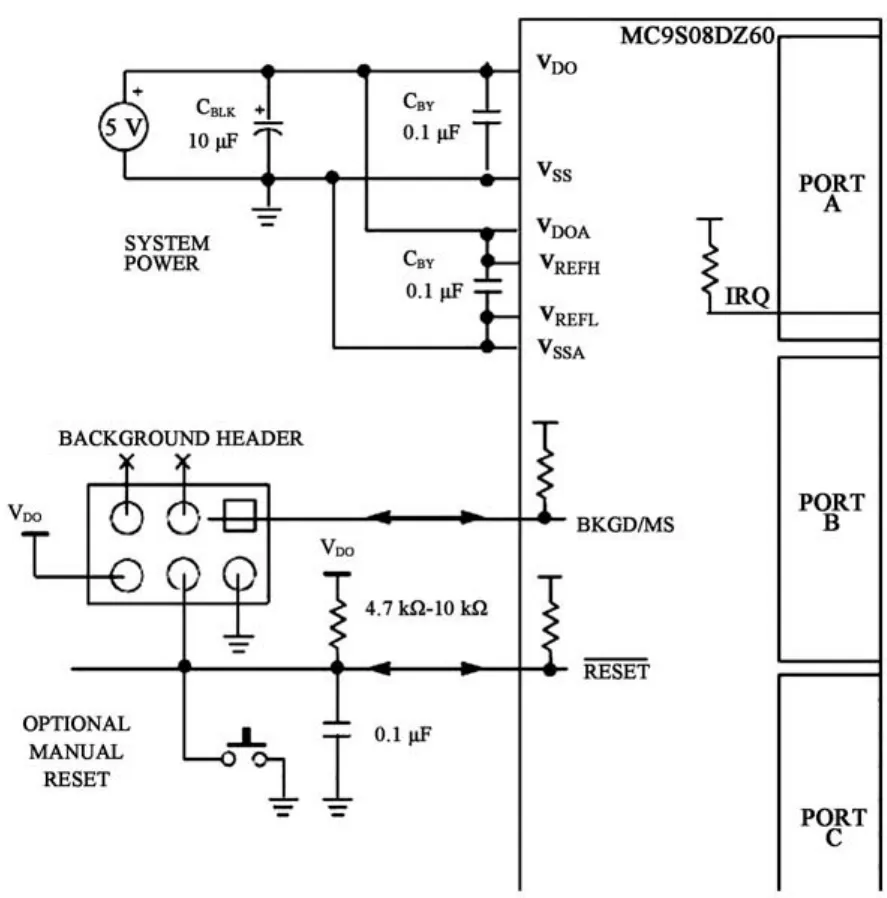

3.2.2MC9S08DZ60的设计

因为系统通过I2C总线控制数据的传送,所以需要一个单片机来产生I2C信号,MC9S08DZ60是飞思卡尔公司生产的,8位HCS08中央处理器;40 MHz HCS08 CPU(20 MHz总线);HC08指令集,支持32个中断源;Flash存储器60KB;EEPROM在线可编程内存2K;4KB的RAM;支持两种低功耗停止模式;53个通用输入/输出(I/O)管脚和1个专用输入管脚;24个中断管脚,每个管脚带触发极性选择.

图5 DS90UB913Q RID电阻配置Fig.5 RID resistor configuration of DS90UB913Q

图6 解串器与MCU电源模块Fig.6 Supply module of deserializer and MCU

本系统会用到MC9S08DZ60的两个外围设备:I2C与CAN.

其中I2C负责控制系统数据的传递,对DS90UB914Q进行读写,从而对串行器DS90UB913Q以及OV9712的寄存器进行读写与访问.

CAN总线模块是为后期做准备,与其他的汽车片上系统进行控制器局域网通信.

此单片机是通过一个6脚的仿真器与计算机相连来进行调试的,BKGD/MS引脚在进行复位的过程中具有模式选择功能.

如果有一个调试系统连接到6脚标准仿真器上,它将在复位的上升沿将BKGD保持在0位,从而使MC9S08DZ60进入调试模式.

BKGD/MS管脚主要用于调试控制器的(BDC)通信.在通信过程中使用一种协议,该协议在每个Byte时间周期内使用目标MCU的BDC时钟的16个时钟周期.目标MCU的BDC时钟速率可以和I2C总线的时钟速率一样快,因此在任何情况下BKGD/MS管脚都不应连接大电容.

BKGD/MS管脚在计算机调试通信协议可以提供瞬间、主动驱动的高速脉冲来确保快速达到上升沿.传输线上的小电容和单片机内部上拉电阻的参数不会影响BKGD/MS管脚的上升沿和下降沿时间.

OV9712控制采用SCCB(SeriaI Camera ControlBus)协议,是简化的I2C协议,SIOC是串行时钟输入线,SIOD是串行双向数据线,分别相当于I2C协议SCL和SDA.通过I2C配置OV9712寄存器时需要注意以下几点:

(1)响应信号ACK被称为一个传输单元第9位,分为Don't care和NA.Don't care位由从机产生;NA位由主机产生.

(2)由于SCCB不支持多字节读写,NA位必须为高电平.另外,SCCB没有重复起始概念,因此在SCCB读周期中,当主机发送完片内寄存器地址后,必须发送总线停止条件.不能产生Don't care响应信号.

图7 MC9S08DZ60原理图Fig.7 MC9S08DZ60 Schematic

(3)由于I2C和SCCB一些细微差别,所以采用GPIO模拟SCCB总线方式.SCL所连接引脚始终设为输出方式,而SDA所连接引脚在数据传输过程中,通过设置IODIR值,动态改变引脚输入/输出方式.SCCB在写周期直接使用I2C总线协议写周期时序[8-9].

单片机原理图如图7所示.

3.2.3DS90UB914Q的设计

解串器上有一个多路转换器,其作用是在两个输入串行器之间进行选择.解串器可以只有一个有效的输入影像器.初级的视频传输在1个单一的高速串行数据流上转换10位或者12位数据.同时进行单独的低延时的双向控制通道传输,并从I2C总线端口接收控制信息,其在视频消失过程中是独立的.

DS90UB914Q的MODE引脚在设计时需要注意要连接一个下拉电阻,在本系统中由于采用的10位数据传输模式,并且像素时钟PCLK在10~100 MHz,所以根据解串器的datasheet[7]下拉电阻阻值为11Ω.

DS90UB914Q的SCL与SDA引脚设计时需要加上拉电阻,如图8所示.

图8 DS90UB914Q MODE电阻以及I2C上拉电阻配置Fig.8 DS90UB914Q mode resistor and I2C pull up resistors configuration

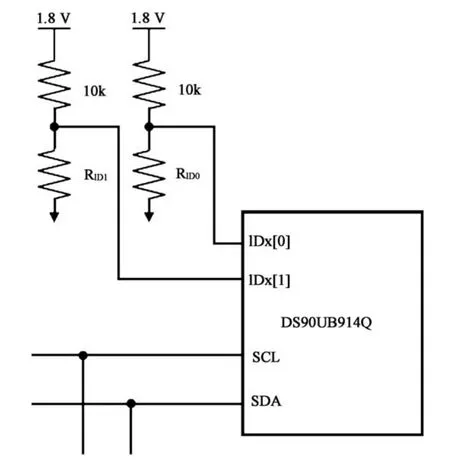

DS90UB914Q的ID[0]、ID[1]引脚需要加上2个10 kΩ的上拉电阻与2个0 kΩ的下拉电阻,如图9所示.

4 FPD Link III接口LVDS信号的设计

系统串行器与解串器之间的连接是数据传输的关键,本系统中FPD Link III接口中包括电源

和GND还有一对儿差分信号,此差分信号为百兆高速的LVDS信号,在设计时首先应该在信号的正负两端串联0.1μF的电容,然后通过共模电感ACM2012H来进行滤波处理,如图10所示.

图9 DS90UB914Q RID电阻配置Fig.9 RID resistor configuration of DS90UB914Q

图10 LVDS信号的滤波Fig.10 LVDS signal filtering

差分信号(Differential Signal)在高速电路设计中具有广泛的应用,电路中关键的通信信号通常都是差分对信号.差分信号的定义就是发送端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来确定逻辑状态是0还是1.而差分信号的那一对儿走线就是差分线.差分信号与普通的单端信号走线相比,信号通信稳定.

为了使两个信号DOUT+/RIN+与DOUT-/RIN-之间组成一对差分信号,差分信号需要加上100Ω电阻进行阻抗匹配.还应该设置等长,注意不要跨分割参考平面[10].

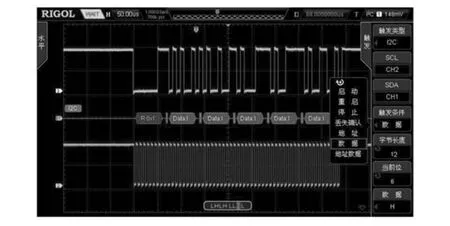

DS90UB913Q/914Q的I2C数据总线提供了MCU和传感器模块之间的通信,其总线波形如图11所示.通过同一串行视频链接,用透明的双向传输.PCLK像素时钟实际结果为50 MHz,I2C总线最高速率为400 kbps.控制信道(I2C),VSYNC是帧同步信号,HSYNC是行同步信号,PCLK是时钟,OUT是数据.在数据传输时,以PCLK的时钟为同步信号,在PCLK的上升沿,产生数据跳变,如图12所示.

DS90UB913Q/914Q芯片组将10位并行图像RGB数据通过LVDS差分对信号的形式进行

图11 I2C总线的波形图Fig.11 I2C bus oscillogram

图12 主要输出信号波形图Fig.12 Waveform figure of main output signal

5 结 论

通过LVDS的串行数据流,DS90UB913Q/ 914Q芯片组支持车载行车记录仪电子系统.单差分对(FPD-Link III)适用于串行器与解串器之间的连接.

[1] 杨坤明,付在明.高清图像处理芯片串行差分输出接口测试研究[J].微计算机信息,2008,24(9-2):294-295,312.

Yang K M,Fu Z M.Research for HD image process TFP-Link LVDS interface testing[J].Microcomputer Information,2008,24(9-2):294-295,312.(in Chinese)

[2] 陈莹,高双成.基于FPGA的LVDS接口应用[J].电子科技,2012,25(1):8-12.

Chen Y,Gao S C.Application of the LVDS Interface Based on FPGA[J].Electronic Science and Technology,2012,25(1):8-12.(in Chinese)

[3] DS90UB913(4)Q:百万象素照相机FPD-LinkⅢ接口方案[J].世界电子元器件,2012(10):20-21.

DS90UB913(4)Q:Megapixel camera FPD-LinkⅢinterface[J].Global Electronics China,2012(10):20-21.(in Chinese)

[4] DS90UB913Q/914Q:串行器/解串器[J].世界电子元器件,2012(10):28-28.

DS90UB913Q/914Q:Serializer/Deserializer[J].Global Electronics China,2012(10):28-28.(in Chinese)

[5] 王胜,王新宇.LVDS技术及其在高速系统中的应用[J].遥测遥控,2005,26(4):41-46.

Wang S,Wang X Y.LVDS and it's application in high speed system[J].Telemetry&Telecontrol,2005,26(4): 41-46.(in Chinese)

[6] 于良耀,宋健.汽车总线数据采集模块设计[J].计算机测量与控制,2007,15(2):268-270.

Yu L Y,Song J.Design of vehicle bus data acquisition module[J].Computer Measurement&Control,2007,15(2):268-270.(in Chinese)

[7] Omni Vision.OV9712芯片手册[EB/OL].Omni Vision.www.ovt.com,2013,10.

Omni Vision.OV9712 Datasheet[EB/OL].Omni Vision.www.ovt.com,2013,10.(in Chinese)

[8] 陶杰,王欣.基于STM32F407和OV7670的低端视频监控系统[J].单片机与嵌入式系统应用,2014,14(3): 60-62.

TaoJ,Wang X.Low-end video surveillance system implemented with OV7670 and STM32F407[J].Microcontrollers &Embed ded Systems,,2014,14(3):60-62.(in Chinese)

[9] 宋海吒,唐立军,谢新辉.基于FPGA和OV7620的图像采集及VGA显示[J].电视技术,2011,35(5):45-47,61.

Song H Z,Tang L J,Xie X H.Image acquisition and VGA display based on OV7620 and FPGA[J].Video Engineering,2011,35(5):45-47,61.(in Chinese)

[10] 童子权,白景玲.LVDS传输技术在高速数据采集系统中的应用[J].国外电子测量技术,2009,28(2):59-61.

Tong Z Q,Bai J L.Application of the LVDS transmission technology to high-speed data acquisition system[J]. Foreign Electronic Measurement Technology,2009,28(2):59-61.(in Chinese)

Exploring the program of video coding based on the OV9712 SER/DES

ZHANG Bao-long1,LI Dan1,WANG Jing-yun1,KWOK Hoi-sing2

(1.College of Information and Automation,Tianjin University of Science and Technology,Tianjin 300222,China;

2.Center for Display Research,Hong Kong University of Science and Technology,Hong Kong,China)

An OV9712 from Omnivision company was chosen as image sensor for design of automotive camera module.In order to improve the communication speed of high definition image signal,a set of chips from TI,DS90UB913Q and DS90UB914Q as serializer and deserializer was adopted to coding and decoding the LVDS differential signal of high definition image.Finally,the design realizes the function of high-speed and full-duplex communication by LVDS.The experimental result shows that the application of these chipsets improves the image quality of automotive camera module greatly.

OV9712;DS90UB913Q/DS90UB914Q;FPD-Link III;full duplex communication

TP29

A doi:10.3788/YJYXS20153006.0965

1007-2780(2015)06-0965-07

张宝龙(1976-),男,天津人,教授,硕士研究生导师,主要从事集成电路设计及半导体制备工艺方向的研究.

李丹(1977-),女,辽宁人,副教授,硕士研究生导师,主要从事光电检测与计算机视觉检测方向的研究.

2015-01-05;

2015-03-15.

天津市科技支撑计划资助项目(No.13ZCZDGX03000)

Supported by Tianjin Science and Technology Support Program(No.13ZCZDGX03000)

∗通信联系人,E-mail:eezbl@tust.edu.cn