一种基于FPGA的航空总线容错机制设计

2015-10-20丁志平东华大学信息科学与技术学院上海201620

丁志平(东华大学 信息科学与技术学院,上海 201620)

一种基于FPGA的航空总线容错机制设计

丁志平

(东华大学信息科学与技术学院,上海201620)

航天应用中,单粒子翻转引发SRAM型FPGA的错误最多,而EDAC设计在纠错模块中有着广泛的应用。将依据扩展海明码设计的[40,32]EDAC模块嵌入到ARINC 659的双口数据DPRAM和指令SRAM中,提高了总线控制器的容错处理能力。

ARINC 659;单粒子翻转;错误检测与纠正;海明码

0 引言

集成电路的应用领域在不断深入扩大,航空航天方面要求系统能长期可靠地运行,其运行的环境辐射比地面辐射严重,集成电路很容易受到干扰,导致设备不能正常工作。单粒子翻转是指高能粒子射入集成电路的PN结,会发生PN结电离、电荷积累、能量转移等。存储器件某一位数据会从一个稳态转变为另外一个稳态,是引发航天器故障的主要因数。

为了最大限度地减少单粒子效应对FPGA的影响,通常采用三模冗余的加固结构,尽管三模冗余结构可以将错误暂时隔离,但是在长期工作的情况下冗余单元也可能继续发生错误。近年来国内外采用EDAC电路来减少或避免错误的发生。常见的EDAC电路都是采用专用芯片配上时序来工作的,这不利于系统的集成小型化和低功耗。本文基于ARINC 659控制器的设计,利用Verilog HDL实现EDAC的功能,使设计朝着高集成、低功耗的方向发展[1]。

1 ARINC 659总线技术简介

ARINC 659[2]是一种航空电子模块化设计的背板总线标准,有鲁棒分区,具有确定的时间和空间性。霍尼韦尔公司根据ARINC 659标准设计的SAFEbus用于波音777的飞机信息管理系统中,从1993年被采纳成为行业标准至今已经稳定运行30多年。它能够应用于大型客机的电子系统,表明ARINC 659是一种较为可靠的内总线,适用于航天系统的综合电子平台。

在ARINC 659标准中,每一个可插拔的子板被称作在线可更换模块(Line Replaceable Module,LRM)。每个LRM有两个总线接口(Bus Interface Unit,BIU)。在该标准中,一条659总线上最多允许连接32个LRM。ARINC 659使用时间触发的调度方式称为表驱动比例访问协议(Table Driven ProportionalAccess,TDPA),并将决定总线时分复用特性的调度表保存在每个BIU中,维护协议的数据开销非常小。ARINC 659的4线交叉校验机制可以对每一位进行校验。

ARINC 659假设每个BIU使用独立的时钟,储存相同的TDPA表,因此在总线工作时是没有中心控制的分布式系统的。同时,ARINC 659也支持LRM的冗余,协议中最多允许某项功能有4个LRM做备份。

目前见到的航空总线标准中,ARINC 659总线的实时性、可靠性和冗余度是最高的,但霍尼韦尔公司只提供整机解决方案,不提供芯片,因此研究该总线能为我国航空电子系统开发与应用提供帮助。

2 EDAC的原理与实现

2.1海明码的基本原理

海明码是一种广泛使用的可以纠正单个错误和检测任意两位错误的线性分组码。常见的海明码应满足不等式2m≥n+m+1,其中n为数据码的位数,m为校验码的位数,如果要求既要能纠正一位错位又能检测出两位错位,则至少需要m+1位校验码。该控制器中传输32bit数据,依据海明码的原理,使用8bit校验位,构成[40,32]扩展海明码。依据规则,在数据位的第2k(k=0,1,2,3,4,5)bit上放置校验码。

2.2EDAC模块的设计与实现

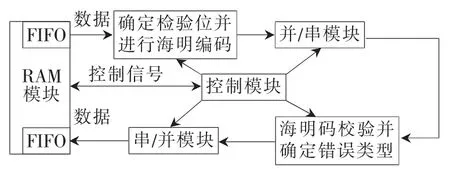

EDAC模块在CPU与RAM之间[3],保护控制器RAM的数据,CPU对RAM操作时,EDAC模块已经对RAM中的数据进行了预处理,同时EDAC模块中也加入了使能信号。EDAC主要工作在写周期和读周期,如图1所示,EDAC主要包括发送和接收两个部分。

图1 EDAC电路框图

上面发送模块负责海明码编码,用控制电路寄存器中的数据位确定校验位,然后依据海明码的长度和编码方案编码。将并行转成串行数据发出去。接收模块主要负责海明码纠错与解码,解码过程就是依据已知校验位数确定码字长度;而纠正就是用已经生成的校验码和形成该校验码的编码方程再进行一次异或操作,如果该等式为0,则代表没有发生错误,若等式为1,说明有错,可以从等式的值判断具体的出错位,纠正后再从码字中选出数据位。

EDAC模块通过Verilog HDL在FPGA中实现,其总体框架如图2所示,其各变量的含义如下:

wr:CPU读写信号,0和1分别表示为写和读。

c_data[7:0]:CPU的传送和接收数据。

mem_data[39:0]:存储器数据包括32bit数据位和8bit校验位。

er_out[1:0]:错误类型,分别为无错误、1bit错、2bit及2bit以上错、校验位错误。

图2 EDAC模型

3 EDAC模块在ARINC 659总线控制器中的实现

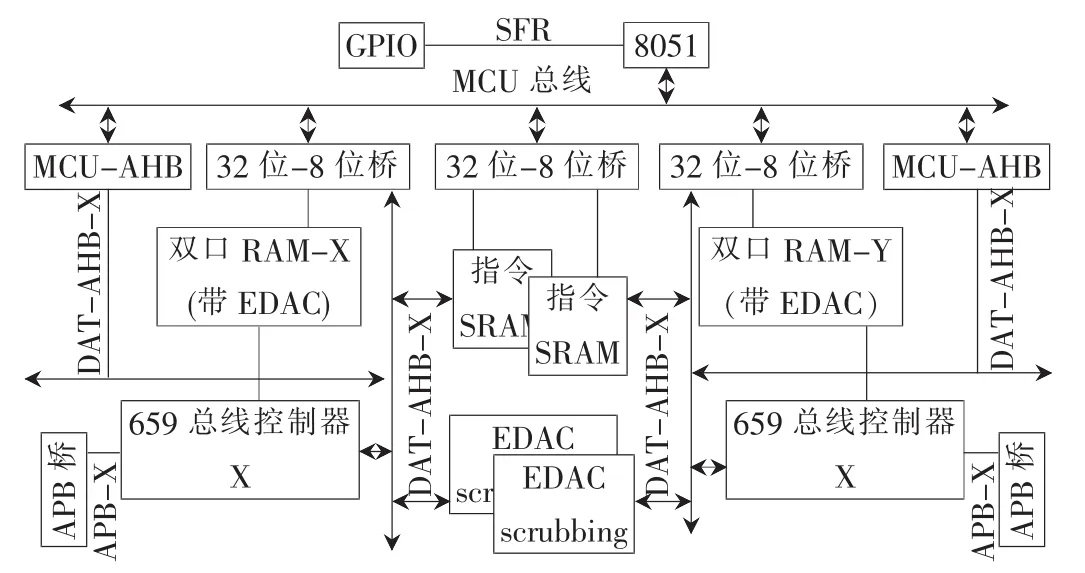

图3是ARINC 659总线的系统框图,双口数据DPRAM使用[40,32]EDAC编码保存数据。8051读取数据时,EDAC状态寄存器记录1bit错或2bit错。EDAC状态寄存器有可屏蔽的EDAC中断。依据海明编码原理,ARINC 659总线控制器读取数据时,1bit错直接纠正,2bit以上的错不做处理,ARINC 659总线控制器自身能保存正常数据,2bit以上的错误导致ARINC 659总线校验全部失效,将数据错误通知其他LRM。

图3 ARINC 659片上系统

指令SRAM也使用[40,32]EDAC编码保存数据,写入方法与双端口数据DPRAM相同。正常状态下,ARINC 659总线控制器只读指令SRAM,指令SRAM自身也有EDAC,但随着时间累积,单粒子翻转可能在指令SRAM中累积,最后发生多位错。针对这种情况,在ARINC 659指令总线上新增EDAC刷新模块,它每次读取指令SRAM的一个字,再将其写入指令SRAM,可以避免1bit错累加形成多位错。659总线控制器读取指令SRAM的EDAC状态时,对1bit错不做处理,对2bit错659总线控制器会断开,另一个659总线控制器依靠交叉使能不一致也会断开。659总线控制器遇到多位错将会变为未知状态,最终因为交叉使能不一致也会断开。图4是32bit数据5A5A5A5A经过EDAC模块之后的状态。

图4 经EDAC模块的SRAM状态

4 注入故障与结果分析

通常SEU发生频率与器件所处的轨道位置和工作时间有关,每天SRAM中SEU的发生约为3×10-5位。为了加快实验进度,采用与实际情况相似的硬件故障注入方式,故障注入基本频率为10次/s。其结构如图5所示,包括注入机和目标机,注入机通过向FPGA发送命令的方式注入故障,实现故障逻辑[4]。

A new avionics bus fault tolerance mechanism design based on FPGA

Ding Zhiping

(Institute of Information Science and Technology,Donghua University,Shanghai 201620,China)

In the space environment,the most fault in SRAM type FPGA is the effect of single event upset(SEU).The EDAC module has a broad application in the field of aerospace error detection.In this paper,we use extension Hamming code to design[40,32]EDAC module and algorithm,which is embedded in ARINC 659 data dual port RAM and instructions SRAM module,to improve the fault tolerance ability of the ARINC 659 bus controller.

ARINC 659;single event upset(SEU);error detection and correction(EDAC);Hamming code

TP37

A

1674-7720(2015)10-0020-02