基于FPGA的数字直放站链路切换设计

2015-10-19俞沁璐同济大学电子与信息工程学院上海201804

俞沁璐,赵 霞(同济大学 电子与信息工程学院,上海 201804)

基于FPGA的数字直放站链路切换设计

俞沁璐,赵 霞

(同济大学 电子与信息工程学院,上海 201804)

针对数字光纤直放站系统的远端单元给出了一种简单高效的链路切换设计方案。首先对通信链路进行检测,其次切换同步时钟,最后改变物理接口与上下行数据的映射关系,并使用FPGA进行实现。实验平台测试表明,在光纤故障和设备故障等通信链路故障时,通过链路切换实现了环网自愈,系统组网更为灵活,大大提高了系统的可靠性,可应用于安全性要求高的场合。

数字直放站;环网;链路切换;FPGA

0 引言

近年来,数字光纤直放站在无线信号补盲方面应用广泛。实际应用中,数字光纤直放站系统常以灵活的组网方式来降低投资成本,增大信号覆盖面积。数字光纤直放站系统中的近端机与远端机(RU Remote Unit)主要的组网方式有星形组网、链形组网和环形组网。星形组网方式简单,适用于信号圆形覆盖场合,在狭长型地带则利用率不高。链形组网通过级联方式能够适用于狭长地带的覆盖,但是如果链路中某级设备发生故障或者某段光纤发生故障,会导致故障节点后级设备无法正常工作[1]。以上两种组网方式都不适用于可靠性要求高的领域,如铁路通信系统。环形组网能够通过切换倒换等方式进行故障链路的通信恢复,保证了通信的实时性和可靠性,可以适用于安全性要求高的领域。

目前,环形组网故障自愈实现有以下几种方式:参考文献[2]介绍了光纤切换保护系统,通过备份光纤链路来保护通信链路,当工作链路出现故障时切换到备份光纤链路,但不能解决因为设备掉电等故障导致通信故障的问题。参考文献[3]提出基于系统拓扑的环网自愈,通过近端机轮询当前系统中RU的状态来更新当前拓扑信息,但不能及时发现链路中的故障,同时占用较多的系统资源。参考文献[4]提出基于设备端口链路切换的机制,由故障节点前级设备上报相关告警信息,再由近端机重新发起拓扑确认信息对故障后级设备进行建链。

为了实时监控环网中故障节点,由RU对通信链路进行检测是必要的,通过RU及时上报自身链路状态可进一步缩短环网自愈时间。本文主要针对RU设计了一种基于FPGA的简易高效端口链路切换方法,实时监测链路状态以及时发现故障节点,通过映射建立物理光口和上下行数据流的对应关系,使实际组网更为简单灵活。

1 环网自愈工作原理

1.1 环网自愈

当环形网络中某个RU出现故障或者光纤断链,该级RU的前级与后级RU能检测到故障,并根据本机的链接情况自动判断是否切换上下行链路端口。环网断链自动切换链路端口保证了环网中除去故障节点外的其他节点能够正常工作。以图1的环形组网方式为例,如图1(a)所示,下行数据流方向为近端机-RU0-RU1-RU2-RU3-RU4-RU5,如果RU1和RU2中间的光纤发生断链故障,此时RU2及之后的设备应自动倒换端口,网络拓扑分裂为两条链型拓扑,数据流方向分别为近端机-RU0-RU1和近端机-RU5-RU4-RU3-RU2(图1(b))。为了实现上述机制,系统中RU接收发送的上下行数据与物理光口之间并不是一一对应关系,本文将接收系统下行数据且恢复接收时钟作为系统参考时钟的物理光口定义为逻辑主口,接收上行数据的物理光口定义为逻辑从口。

图1 环形组网

1.2 时钟同步机制

为了保证系统的正常工作,系统无线数据收发正确,RU与近端机之间需要进行时钟同步。RU通过CDR(Clock Data Recovery)技术从近端机或上一级RU传送过来的光纤数据中恢复出接收时钟,并将接收时钟送入RU时钟电路做时钟参考。在时钟电路中,本地晶振时钟由压控晶体振荡器产生,通过锁相环与接收时钟完成同步锁定,锁定后的时钟为RU的工作时钟。RU恢复的接收时钟是时钟同步的核心,也是RU是否正常工作的基础。

1.3 链路切换机制

为了适应各种组网方式,降低系统功耗,减少系统的资源消耗,本文设计的链路切换机制可根据系统的组网方式进行自适应调整。当系统组网为非环形网络时,该模式下RU对接收到的近端机切换信令视为无效信息,不进行参考时钟与底层数据流间的切换。当系统组网为环形网络时,RU通过光功率检测信号和帧丢失信号来监测当前逻辑主口的光路状态。当监测到逻辑主口光路状态异常时,逻辑主从口同时关闭停止发送数据。其次,将本地参考时钟切换到另一物理光口的接收恢复时钟。待保护时间过后重新对光路状态进行监测,当光路状态正常后,交换RU的逻辑主从口,并由当前逻辑主口向近端机上报链路切换告警。

2 FPGA链路切换设计

本系统使用的是Xilinx公司的FPGA Spartan6芯片xc6vlx75T[5],软件平台为Xilinx公司提供的ISE14.7开发工具,使用的硬件描述语言是Verilog。FPGA实现环网自愈的链路切换单元主要由控制模块、GTP模块、检测模块、时钟选择模块、数据映射模块等组成,如图2所示。控制模块完成环网切换状态机,对整个环路光纤链路的检测和切换进行控制。GTP模块完成物理光口接收时钟和光纤数据的恢复。检测模块完成对端口光纤链路状态的监测。时钟选择模块实现远端机参考时钟的选择和切换。数据映射模块完成物理光口数据和逻辑主从口数据的映射。

图2 链路切换单元示意图

2.1 GTP模块

FPGA Spartan6系列芯片集成了低功耗、高数据收发的GTP收发器[6],GTP工作范围为614Mb/s~3.125Gb/s,支持收发双向,且收发独立;本设计中使用了GTP硬核来完成物理光口的数据接收与发送。调用GTP核时,选择线速率为2.4576Gb/s,选择8B/10B编码,数据位宽16bit。GTP将接收到的数据解码恢复送入映射模块,同时将映射模块的数据进行编码后发送。此外,GTP还将恢复的接收时钟送入时钟选择模块。

2.2 控制模块

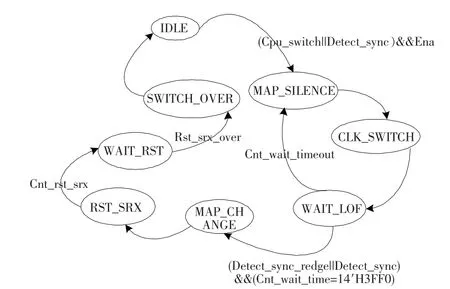

控制模块产生链路切换动作的控制信号。状态机当前状态指示信号和链路切换控制信号输出送给时钟选择、GTP模块和数据映射模块。控制状态机由检测模块的监测信号和GTP模块的复位完成指示信号来启动、迁移和终止。控制状态机有8个状态,状态机的迁移图如图3所示。状态机初始状态为空闲(IDLE),在环网模式时受上位机配置信令和监测信号驱动。如果接收到上位机配置的切换信令或监测端口链路异常,状态迁移至映射静默状态(MAP_SILENCE),该状态下逻辑主从口关闭数据的接收与发送通道。随后状态迁移至时钟切换状态(CLK_SWITCH),此状态下时钟接口模块完成参考时钟的切换,控制时钟切换信号selrefclk0取反。接着状态迁移至失锁恢复等待状态(WAIT_LOF),考虑到光纤的传输时延防止RU之间时钟互锁,因此在该状态下加入保护时间:当等待时间达到0.1s后再进行失锁状态监测;如果参考时钟端口失锁指示正常,则进入映射更改状态(MAP_CHANGE),否则,超时返回MAP_SILENCE。MAP_CHANGE状态的下一状态为 GTP接收复位状态(RST_SRX),该状态下对GTP模块的接收单元进行复位,当接收到复位完成信号后,状态迁移至切换结束状态(SWITCH_OVER)。最后,状态迁移至IDLE。

2.3 时钟选择模块

RU两个物理光口恢复的接收时钟独立,为了完成底层的时钟切换以及保证本地时钟工作正常,通过全局缓存选择器(BUFGMUX)选择本地时钟的参考输入[7]。selrefclk0是由控制模块产生的BUFGMUX选择信号。当selrefclk0信号为1时,BUFGMUX输出的时钟为物理光口0接收恢复时钟,反之为物理光口1接收恢复时钟。

图3 控制状态机迁移图

2.4 数据映射模块

系统中,RU的主口与前一级设备(如近端机)链接,接收系统下行数据,并发送上行数据;从口与后一级设备连接,转发主口接收的下行数据,接收后级设备发送的上行数据。RU数据收发接口结构示意如图4所示。由于逻辑主口和逻辑从口的接口数据差异性,需要独立设计。为了简化设计,降低模块内部耦合度,设计中将逻辑主口与逻辑从口封装成核,留出数据接口,与GTP接口之间通过数据映射模块来完成数据流的对应关系。若当前控制模块的控制状态迁移为MAP_CHANGE时,根据selrefclk0信号状态更改映射状态信号Cur_mapping_state,由该状态信号决定物理光口和逻辑主从口之间数据映射关系。

图4 RU数据收发接口结构示意图

2.5 监测模块

一般在板间通信中,接收端在接收时,首先进行链路同步操作以保证之后的通信工作正常。系统中RU与近端机之间的通信协议使用了 cpri协议[8],当 RU与近端机之间为同步状态时,帧丢失信号LOF为0。若通信过程中接收的数据出现错误,同步状态无效,LOF信号为1。FPGA外部电路提供了光模块检测信号丢失信息SFP_LOS和光模块在位信号SFP_PST。因此将逻辑主口的上述三个信号作为检测端口链路是否正常的判断条件,即每次控制状态机进入检测状态时,都对逻辑主口所对应物理端口的相关信号进行监听,当任意信号的翻转边沿被触发时,输出detect_sync信号到控制模块。

3 实验验证

测试平台包括软件平台和硬件平台。软件平台为直放站系统上位机调试软件和计算机串口通信软件。硬件平台包括一台数字直放站近端机、4台RU设备以及PC,测试平台实物图如图5所示。其中近端机有4个光口,RU有2个光口。RU_2通过光纤接入近端机3号光口,RU_3通过光纤与RU_2级联;RU_31的0号光口通过光纤与近端机 4号光口连接,1号光口与RU_4通过光纤级联。RU_4的1号光口与RU_3的1号光口通过光纤连接。PC接入近端机上的调试网口和RS232串口,通过上位机软件远程控制近端机和RU并读取拓扑信息。为了获得可靠准确的结果,通过上位机软件读取系统的拓扑结构,RS232串口打印CPU通信消息队列辅助分析测试结果。

图5 测试平台实物图

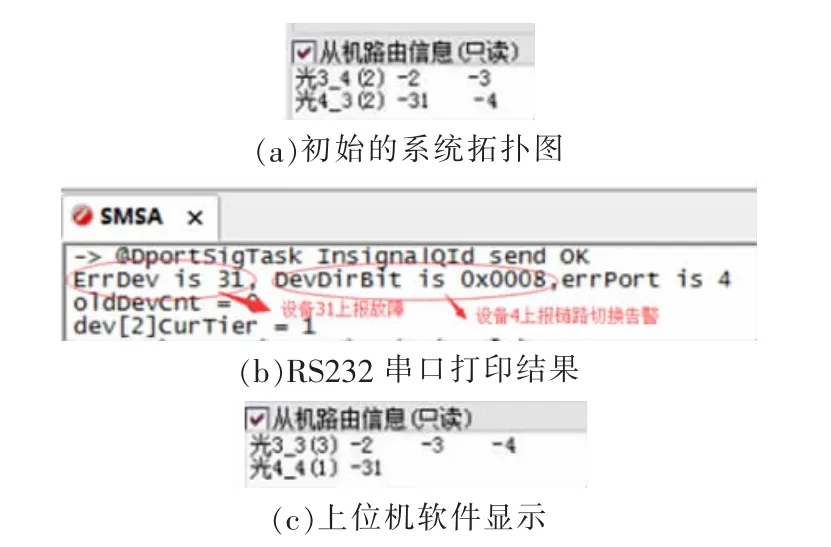

测试初始的系统拓扑如图6(a)所示,系统分配RU_2的设备号为2,RU_3的设备号为3,由近端机3号光口管控;系统分配 RU_4的设备号为 4,RU_31的设备号为31,由近端机4号光口管控;上位机软件表示当前系统物理实际拓扑为环形,显示为“光口3_4/光口4_3”,3号光口和 4号光口是环形拓扑的两个节点,但是逻辑拓扑两条链型;如果物理拓扑结构是链形则显示为“光口 3_3(X)/光口 4_4(X)”,(X)表示管控的 RU设备数目。

图6 测试用例1

测试用例1:断开RU_31和RU_4间的光纤。

理论结果:近端机光口4管控链形拓扑中的末级RU_4发生链路切换,级联至RU_3,成为光口3所管控的链形末级设备。故障节点前级RU_31不发生改变。系统物理拓扑为一条链形和一个星形。

实际结果:RS232串口打印结果显示链路中出现故障,上报故障节点的设备ID为31即为RU_31,且收到设备ID号为4的链路方向调转指示告警,如图6(b)所示;上位机软件显示当前拓扑为两条链形,近端机3号光口管控3台RU,分别为RU_2、RU_3和RU_4;4号光口管控一台RU_31,如图6(c)所示。测试结果与理论结果一致。

恢复RU_31与RU_4之间的链路,此时拓扑由链形拓扑更新为环形拓扑。

测试用例2:RU_3掉电。

理论结果:RU_4发生链路切换,RU_4级联到RU_31。近端机光口4管控的拓扑由星形变为2级RU级联的链形拓扑。故障节点前级RU_2不发生改变。系统物理拓扑更新后只有3台RU设备,即RU_2、RU_31 和RU_4。

实际结果:RS232串口打印结果显示上报故障节点的设备ID为2,且收到设备ID为4的链路切换指示告警;上位机软件显示当前拓扑为一条链形和一个星形,近端机3号光口管控RU_2,4号光口管控 RU_31和RU_4。测试结果与理论结果一致。

实际测试结果表明,系统在光纤故障和设备故障时能定位故障节点,并进行相应的切换,上位机监控的系统拓扑结构与实际拓扑一致。

4 结论

链路切换是环网自愈的重要组成部分,本文介绍了一种基于FPGA的链路切换设计方案。该方案在通信链路出现光纤故障或设备故障等问题时,可及时检测到故障节点并实现自动切换链路,保证了系统正常通信不受影响,提高了系统稳定性;通过逻辑映射对物理接口与逻辑接口进行数据映射,设计简便,系统组网也更为灵活。通过实验验证了该方案可大大提高系统的可靠性,有重要应用价值。

[1]陈礼波,覃宁,张怡.BBU+RRU分布式基站传输组网建设探讨[C].四川省通信学会2014年学术年会论文集,2014.

[2]黄朋.光纤自动切换保护系统的控制系统实现[D].北京:北京邮电大学,2010.

[3]深圳市零一通信技术有限公司.在数字光纤直放站中自适应组网的方法[P].中国:CN102497234A.2011-12-07.

[4]奥维通信股份有限公司.可环形组网自愈的数字光纤直放站系统及其数据通信方法[P].中国:CN101902281A.2010-12-01.

[5]Xilinx,Inc.Spartan-6 Family overview,DS160(v2.0)[DB/OL].(2011-10-25)[2015-04-20].http://www.xilinx.com/.

[6]Xilin,Inc.Spartan-6FPGA GTP Trsansceivers,UG386(v2.2)[DB/OL].(2010-4-30)[2015-04-20].http://www.xilinx.com/.

[7]宋威,方穗明.基于BUFGMUX与DCM的FPGA时钟电路设计[J].现代电子技术,2006,29(2):141-143.

[8]Cpri.CPRI Specification V5.0[DB/OL].(2011-09-21)[2015-04-20].http://www.cpri.info/.

Design of the link switching of digital repeater based on FPGA

Yu Qinlu,Zhao Xia

(School of Electronics and Information Engineering,Tongji University,Shanghai 201804,China)

This paper proposed a simple and efficient link switching scheme for remote unit(RU)in digital fiber repeater.The key steps are as follows.Firstly,the proposed system detects communication links,and then switches the synchronous clock.Finally,the system changes mapping relation between physical interfaces and uplink and downlink data.The whole process is realized by FPGA.Experimental results show that when communication link failure(e.g.,fiber failure and equipment failure)happens,ring network can be recovered by switching link.This link switching scheme makes system networking more flexible,and increases the reliability of system.This scheme can be used in the situation which requires high security.

digital repeater;looped network;link switching;FPGA

TN92

A

1674-7720(2015)18-0032-04

俞沁璐,赵霞.基于FPGA的数字直放站链路切换设计[J].微型机与应用,2015,34(18):32-35.

2015-04-17)

俞沁璐(1991-),女,硕士研究生,主要研究方向:数字信号处理、无线覆盖。

赵霞(1974-),女,博士,副教授,主要研究方向:控制理论及控制控制工程、数字信号处理。