基于NIOS II的1553B总线测试系统设计

2015-10-19王健军刘士全严华鑫中国电子科技集团公司第58研究所江苏无锡214035

黄 正,王健军,刘士全,严华鑫(中国电子科技集团公司第58研究所,江苏 无锡 214035)

基于NIOS II的1553B总线测试系统设计

黄 正,王健军,刘士全,严华鑫

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1553B总线以其可靠性高、实时性好、使用灵活等优点,广泛应用于现代飞机、导弹、卫星、舰艇、坦克等航空、航天、兵器领域,并且逐渐扩展到地铁交通控制等民用领域。而在实际使用过程中,1553B总线由于接口配置复杂,无法直接与PC进行通信,使得系统的安装调试存在困难。利用NIOS II软核处理器面向用户、灵活定制的特性和USB接口方便、支持热插拔的优点,给出了一种在FPGA上已经实现的1553B总线测试系统设计方法。整个系统硬件设计简单,软件设计稳定可靠,可应用于1553B系统调试和测试以及各种仿真实验中。

NIOS II软核处理器;1553B;USB;测试系统

0 引言

MIL-STD-1553B由美国在20世纪70年代提出,具有可靠性高、实时性好、灵活性强的特点,已经发展成国际公认的数据总线标准,广泛应用于现代飞机、导弹、卫星、舰艇、坦克等航空、航天、兵器领域,并且逐渐扩展到地铁交通控制等民用领域。我国从20世纪90年代初开始引进1553B数据总线,经过十多年的发展,1553B已经成为国内航空航天的主要航电总线之一。国内一些研究机构也通过不断努力,已经有能力研制生产出符合1553B标准的接口芯片,本文在设计中即采用了中国电子科技集团公司第58研究所自主研发的JBU61580作为1553B总线通信控制器,其与DDC公司的同型号芯片BU61580完全兼容,支持插拔替换,具有总线控制(BC)、远程终端(RT)和监测终端(MT)三大功能[1]。

1 系统硬件设计

系统采 用Altera公 司CycloneⅡ系列的FPGA(EP2C8Q208C8)作为主控芯片,内嵌NIOSⅡ软核处理器,输入时钟为20MHz,由PLL倍频出两个100MHz时钟分别提供给NIOSⅡ软核处理器和外接的SDRAM使用。USB接口部分采用CH375芯片,1553B接口部分采用JBU61580芯片,均利用SoPC Builder支持的用户自定义元件定制时序转换逻辑,以提高接口芯片的读写速度,而NIOSⅡ则负责两者之间的数据解析和交换。

1.1 总体设计思想

硬件原理框图如图1所示,整个系统可以分为5个部分:(1)系统核心模块:NIOSⅡ处理器;(2)处理器外围支持电路:时钟单元及SDRAM控制器;(3)程序下载调试模块:JTAG接口控制器和异步通信接口(UART用于打印调试信息);(4)系统内部外设模块:诸如系统ID、定时器、用户自定制逻辑等;(5)系统外围设备:EPCS存储器、CH375、JBU61580。

图1 硬件设计框图

1.2 系统外围接口设计

1.2.1 EPCS接口

系统采用Altera专用的配置芯片EPCS4存储FPGA的配置数据和NIOSⅡ的程序,EPCS4总共有4Mbit的存储空间,分成8个64KB的块,并通过专用电路接口与FPGA连接[2]。FPGA的配置数据从EPCS4中偏移地址为0的地方开始存放,紧接着FPGA的配置数据就是NIOSⅡ的程序,也就是说FPGA的配置数据和NIOSⅡ的程序从EPCS4的低端地址开始存放,而在本设计中只占用了不到4个块的存储空间,所以高端块的存储空间可以用来存放JBU61580的配置数据。

1.2.2 CH375接口

CH375是一个USB总线的通用设备接口芯片,工作在全速模式,兼容USB2.0,其内置了USB通信中的底层协议,具有省事的内置固件模式和灵活的外置固件模式[3]。在内置固件模式下,屏蔽了相关的USB协议,自动完成标准的USB枚举配置过程,完全不需要本地端控制器作任何处理,简化了NIOSⅡ的固件编程。本设计中CH375芯片只负责数据的交换,接收上位机下传的数据和NIOSⅡ上传的数据。CH375的8位数据总线、4线控制信号读选通、写选通、片选输入、中断输出通过SoPC自定制逻辑连接到Avalon系统互连结构。

1.2.3 JBU61580接口

JBU61580工作在16位缓冲非零等待模式下,工作电压为5V,在3.3V电压下工作的FPGA不能与其直接相连,中间需要接总线驱动器245芯片进行电平转换。JBU61580的寄存器和存储器的读写控制有两种方法:一是用PIO口来模拟JBU61580的读写时序,此方法的优点是实现简单,扩展性强,但读写速度比较慢,不利于系统的模块化与集成;二是根据HDL语言定制符合JBU61580的时序控制逻辑,以访问内存的方式来读写JBU61580的寄存器和存储器,此方法实现稍微复杂,但是可以极大地提高JBU61580的数据读写速度。本设计中即采用了第二种方法。

2 软件系统设计

由于JBU61580工作在16位缓冲模式,而CH375只有8位数据总线,因此上位机程序要与NIOSⅡ约定相同的数据封装格式。上位机将JBU61580的16位地址和数据信息以及一些传输控制指令拆分成8位数据,经过USB总线传输,NIOSⅡ收到之后再重新解析成16位的地址和数据。在配置数据全部传送完成之后,NIOSⅡ再根据控制指令来配置JBU61580,使其工作在指令要求的模式(BC、RT或MT)下。另外NIOSⅡ还将根据上位机的指令决定是否将配置数据写入EPCS中,使得单板在上电复位之后不需要再从上位机获得配置数据,从而可以离线工作。处于离线工作状态,NIOSⅡ还应实时监测CH375的中断信号,以便接收上位机的控制指令进入联机工作模式。同样,若NIOSⅡ需要上传JBU61580的通信数据,也要将读取的16位数据拆分成两个8位数据,再写入CH375的上传端点中,上位机取走数据之后同样按照约定的封装格式将解析成16位的数据显示出来。

软件系统设计分为NIOSⅡ固件程序和上位机程序。NIOSⅡ固件程序又分为固件主程序、中断处理程序、数据包解析程序。上位机程序则包括BC模式接口及传输控制、RT模式接口及传输控制、MT接口及传输控制3个部分。

2.1 NIOSⅡ固件程序

2.1.1 固件主程序

固件主程序主要负责系统初始化及流程控制。初始化主要包括CH375的工作状态测试、工作模式选择,JBU61580的初始复位,读取并判断EPCS4配置存储器的高位地址特征字符以确认是否需要单板离线工作等。在初始化之后进入主循环,实时监视USB接口和1553B接口的中断信号。

2.1.2 中断处理程序

中断处理程序包括CH375中断处理程序和JBU61580中断处理程序。由于1553B接口的实时要求性高,因此在SoPC系统搭建过程中,JBU61580的中断优先级要高于CH375的中断优先级。

在CH375中断处理程序中首先读取中断状态,判断中断类型,再进入相对应的中断类型处理程序。如果是批量端点接收到数据,则读取缓冲区的数据,并置位中断下传标志,退出中断[4]。如果是批量端点发送完数据,则应置位中断上传标志,退出中断。其流程如图2所示。

图2 CH375中断处理流程

在JBU61580的中断处理程序中,由于存在BC、RT、MT3种不同的工作模式[5],则分别对应了不同的中断处理程序。以RT模式为例,当JBU61580接收到来自1553B总线的与本地址相关的消息时,若符合中断条件,将产生中断。由NIOSⅡ进行处理,中断处理程序中首先读取JBU61580的中断状态寄存器,判断是否是干扰引起的误中断,读消息描述符中的消息块状态字,判断是否是非法指令;读RT状态字寄存器,判断是否是子地址忙;读取RT上次命令寄存器,获取命令字;根据消息描述符中的数据块指针,找到数据块并保存数据至消息块的结构体中[6]。其流程如图3所示。

图3 RT中断处理流程

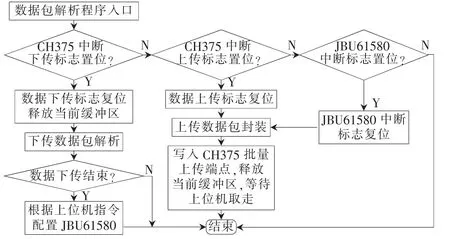

2.1.3 数据包解析程序

数据包解析程序负责解析上位机下传的8位数据及传输控制指令,遵从上位机封装数据的协定,解析出配置JUB61580的16位地址和对应的数据,以及一些如启动、复位等必要的控制指令。另外数据包解析程序还要将从JBU61580读取的16位通信数据分拆封装成8位数据写到CH375的批量上传端口,等待上位机取走。数据包解析程序如图4所示。

图4 数据包解析程序

2.2 上位机设计

CH375在计算机端提供了应用层接口,应用层接口是由 CH375动态链接库DLL提供的面向功能应用的API。用户可以在上位机软件中直接调用这些API,极大地减少了编写USB设备驱动的工作量。CH375动态链接库提供的API包括:设备管理API、数据传输API、中断处理API。上位机的程序可以分成下传数据和上传数据两部分,下传数据调用CH375WriteData()函数来实现,上传数据调用CH375ReadData()函数来实现。由于CH375芯片的上传缓冲区和下传缓冲区只有64B,故一次的数据传输不能超过64B。整个上位机软件采用VB2008编写,图5是RT控制接口界面。

图5 RT控制接口界面

3 结论

按照本文的方法已经成功实现了通过USB实时控制JBU61580的1553B总线接口测试系统,整个系统硬件设计简单,软件设计稳定可靠,可应用于1553B系统调试和测试以及各种仿真实验中。

[1]周远林,吴忠,丑武胜.基于BU-61580的1553B总线接口设计[J].计算机工程与应用,2010,46(35):65-68.

[2]任承志,宋克非,王淑荣.基于BU65170与单片机系统的RT设计与实现[J].微计算机信息,2006,22(6-2):18-20.

[3]雷勇,吴勇,潘莉.基于USB的1553总线通用接口研究[J].计算机测量与控制,2010,18(4):861-864.

[4]DDC.MIL-STD-1553B Designer′s Guide[S].1998.

[5]Condor Engineering Inc.MIL-STD-1553Protocol Tutorial[S.2004

[6]黄长春,徐抒岩.基于DSP的1553B总线系统设计与实现[J].电子设计工程,2010(8):4-7.

Design of 1553B bus test system based on NIOS II

Huang Zheng,Wang Jianjun,Liu Shiquan,Yan Huaxin

(China Electronics Technology Group Corporation No.58 Institute,Wuxi 214035,China)

As a high reliability,good real-time performance and flexibility bus technique,1553B bus is widely used in modern aircraft,missiles,satellites,ships,tanks and other areas of the aviation,aerospace,weapons.In addition,it′s gradually extended to the civilian fields such as the subway traffic control.Actually,the complexity of interface configuration of 1553B bus and not directly communicating with a PC makes system of installation debugging exist difficult.Based on NIOS II soft core processor useroriented,flexible customization features and the advantages of USB interface easy to use,supporting hot-straight,this paper gives a 1553B bus test system that has been implemented with FPGA.The hardware design is simple and software design is stable and reliable.The design can be applied to 1553B system debugging and testing,as well as a variety of simulations.

NIOS II;1553B;USB;testing system

TP391.8

A

1674-7720(2015)18-0098-03

黄正,王健军,刘士全,等.基于NIOS II的1553B总线测试系统设计[J].微型机与应用,2015,34(18):98-100.

2015-05-19)

黄正(1987-),男,本科,主要研究方向:1553B总线测试应用。