基于状态机控制的降压型开关电容DC-DC转换器

2015-10-17邹志鹏

邹志鹏,卜 刚,邹 鹭

(南京航空航天大学 电子信息工程学院,江苏 南京 210016)

基于状态机控制的降压型开关电容DC-DC转换器

邹志鹏,卜 刚,邹 鹭

(南京航空航天大学 电子信息工程学院,江苏 南京 210016)

介绍一种基于状态机控制的多种增益模式转换的控制方法,采用增益跳变和跳周期调制技术,控制增益模式的切换和开关频率,使输出电压稳定,并使系统有较高的转换效率。基于csmc0.5 μm CMOS工艺进行spectreverilog仿真,结果表明能准确控制3种增益的切换和开关频率的变化,并可输出约1.8 V的稳定电压,纹波<20 mV,达到了预期目的。

电容阵列;增益跳变;数字状态机;跳周期调制

随着集成电路技术的不断发展,便携式移动终端的大量出现,对供电电源的要求也越来越高,例如便携性、低功耗、输出稳定、高效率等。目前,传统电荷泵一般采用固定转换比[1-2]和固定开关频率线性控制电荷泵的充放电,具有低噪声,高EMI抑制的优点,但其转换效率低,尤其工作在低负载的转换效率较低。而传统具有多转换比模式的电容泵[3-8],相比固定转换比具有较高效率,但其动态响应速度较慢。另外,为了提高转换效率,降低输出电压纹波,同时采用多种调制机制会产生竞争现象。

在现有的电荷泵开关电源的研究工作中,提出了采用有限数字状态机控制器的调制策略[4]和状态机的设计原则[5],但并未结合开关电源系统设计展开较为具体的研究论述。鉴于此,本文采用了一种基于数字状态机为研究核心,设计了一种以此作为增益跳变调制技术的多转换比电荷泵转换器。针对传统多增益电荷泵工作中低增益切换到高增益时会出现效率陡降的现象,采用状态机来控制并完成各转换比之间的切换,准确平缓地在高低转换比之间进行跳跃,提高了效率、动态响应速度并且使电路数字化,便于实现复杂算法;此外,引入了跳周期调制技术(Pulse Skipping Modulation,PSM)[9-10],同样由数字状态机根据负载情况控制开关频率,起到了粗调后再微调的作用。在保证稳定输出的同时,提高了控制的精度和准确性,并能提供快速的动态响应以及较高的转换效率。同时,状态机能够合理的选择调制机制,一段时间内只允许一种机制工作,有效避免了竞争现象的产生。

1 开关电容DC-DC转换器的工作原理

开关电容DC-DC转换器的开关电容阵列由开关管(SW1~SW9)和电荷泵(C1~C2)构成,电荷泵充作为储能元件,通过时钟发生器及控制电路产生两相不交叠时钟信号phase1和phase2控制9个开关管的导通与关断与电荷泵不同的串并联组合,得到3种增益拓扑结构[8,11],即对应G=1,G=2/3和G=1/2 3种转换比,然后使电荷泵进行周期性的充放电,从而将储存在电荷泵上的能量转移到输出端,进而实现了电压转换。开关电容阵列见和关电容DC-DC转换器系统框图如图1所示。

图1 开关电容DC-DC转换器系统框图

2 增益跳变电路

传统电荷泵一般采用固定转换比进行电压转换[1-2],采用该种结构带来的缺点是,只能保证在有限的输入范围内保持高效率,针对这个问题,采用了多增益调制技术[7-8],即可根据输入电压选择合适的转换比拓扑结构,从而提高了系统效率。

增益跳变电路主要由3部分组成,分别是2 bitADC、输出检测电路和状态机。输入电压经ADC得到2 bit数字量信号d2和d1,其中d2为高位,d1为低位;信号A和B是输出采样信号,作为状态机的输入;信号en、t32和s1是开关电容阵列中拓扑结构的控制信号。

系统输入电压Vin工作在2.6~4.2 V区间内。输入电压经分压后,分别和基准电压Vref1、Vref2进行比较(Vref1=1.2 V,Vref2=0.9 V),从而得到2 bit数字量d2d1,d2d1与开关电容DC-DC转换器增益关系如表1所示。

表1 输入电压与开关电容DC-DC转换器增益关系表

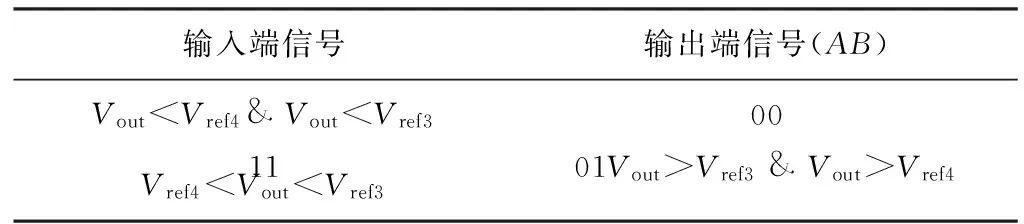

图2左下方是输出检测电路,主要由两个比较器实现。输出检测电路通过检测当前负载状态,给出判断信号A、B,进而在某一段输入电压区间内,根据负载情况,实时地改变开关电容网络的拓扑结构。输出检测电路工作情况如表2所示。

图2 增益跳变电路

表2 输出检测电路工作情况表

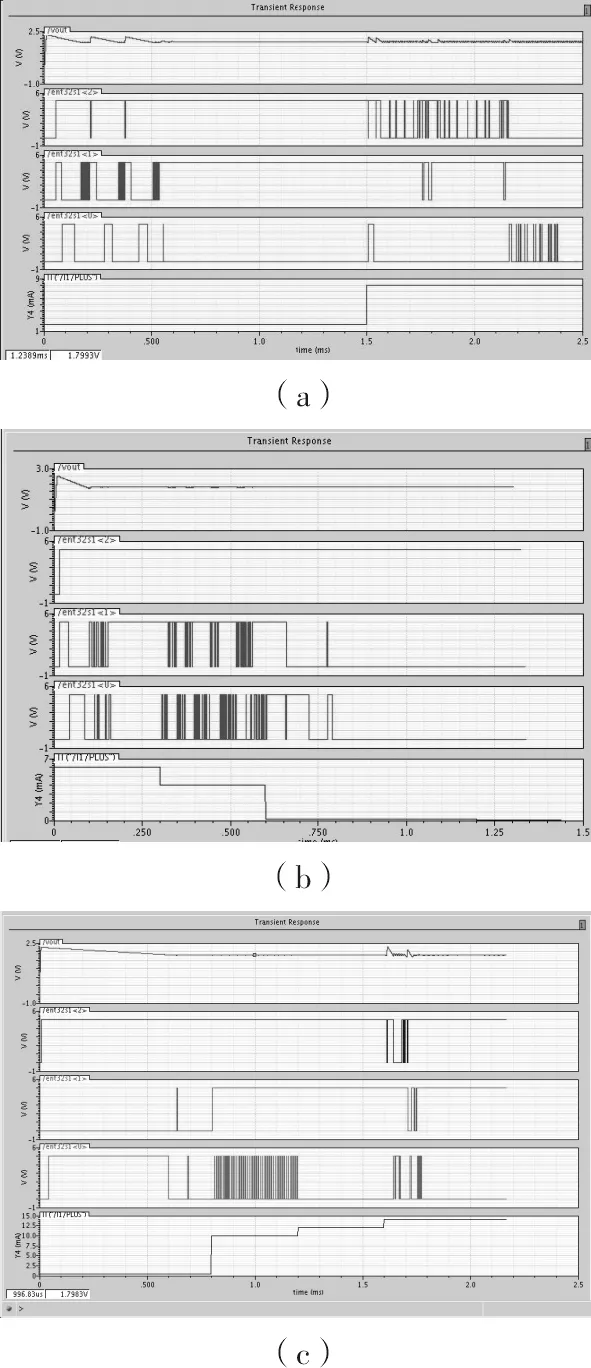

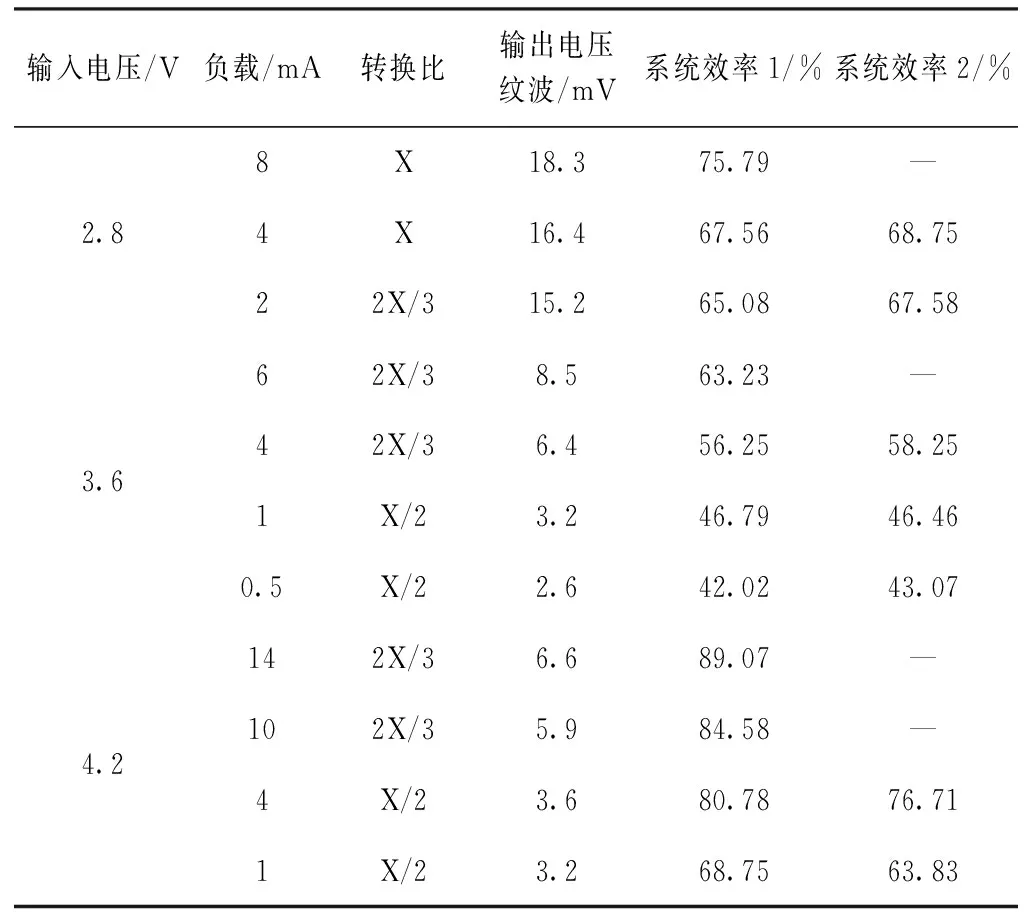

3 脉冲跳周期电路

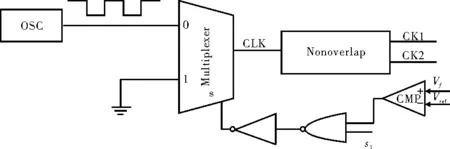

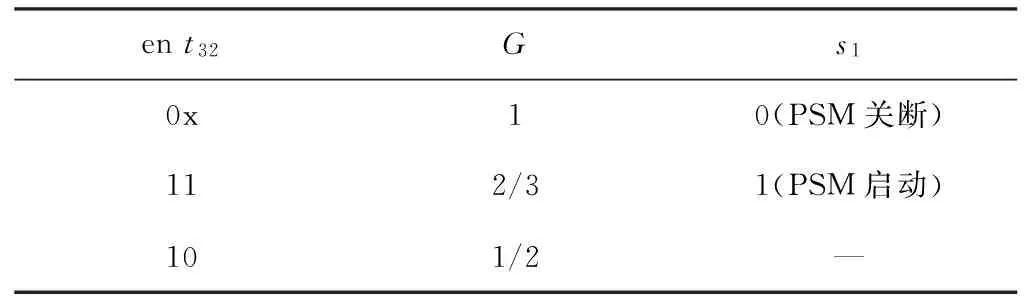

文中采用的跳周期调制技术[9-10]主要由比较器、多路选择器及不交叠时钟产生电路组成。图3中的Vf是系统输出电压采样信号,Vref是基准电压源(Vref=1.8 V),多路器输出信号CLK由控制信号S控制,当S=1时,CLK=0,当S=0时,输出信号CLK为振荡器产生的时钟信号。当Vf>Vref时,比较器输出高电平,则CLK=0,时钟暂时关断,系统输出电压降低,待系统输出电压降低到使得Vf 技术,可降低系统的开关频率,进而得到较高轻载效率。 图3 跳周期调制电路 鉴于系统控制的复杂性,文中采用数字状态机来控制,图4为状态流程图。 图4 数字状态机状态流程图 如图4所示,d2d1AB为状态机4 bit输入,ent32s1为状态机3 bit输出。en和t32为控制开关电容转换器拓扑结构的控制信号,s1为控制脉冲跳变调制的控制信号。 状态机的设计包括一个初始状态Q0,3个增益状态Q1、Q2和Q3,以及两个状态之间的过渡态Q4和Q5,另外还有3个状态控制时钟开关。其中Q1、Q2、Q3分别对应x1/2、x2/3、x1,3个转换比。转换比之间不直接跳转,需经过过渡态Q4、Q5,进而完成跳变过程。 状态机正常工作时,一个时钟上升沿来临时候锁存当前状态,在下一个时钟上升沿来临的时候进行新的状态切换,并输出响应的控制信号,首先由ADC根据输入电压选择合适增益状态,然后根据输出电压采样信号做出下一步的跳转,PSM作为固定转换比下对电压进行微调,两个时钟counter1和counter2控制在x2/3和x1时开启PSM的最大时间,当计数超过最大值时,状态由从高增益切换到下一级的低增益状态,从而提高效率。两个机制相互配合使状态控制更加高效,输出电压更加精确。参考电压,en、t32和s1与开关电容网络拓扑结构关系表如表3所示。 表3 控制信号en和t32与开关电容网络拓扑结构关系表 仿真采用CSMC 0.5 μm混合信号CMOS工艺,仿真器为Spectreverilog,设计采用的开关频率f=500 kHz,占空比D1=0.5,输入电压Vin在2.6~4.2 V中取2.8 V、3.6 V和4.2 V仿真测试。当Vin=2.8 V,IL=4 mA时,仿真结果如图5所示,输出电压约1.8 V,纹波16 mV,状态机输出ent32s1最终稳定在010,系统保持在G=1转换比下;当Vin=3.6 V,IL=4 mA时,仿真结果如图6所示,输出电压约稳定在1.8 V,纹波6 mV,状态机输出ent32s1最终稳定在110,系统转换比保持在G=2/3转换比下;当Vin=4.2 V,IL=4 mA时,仿真结果如图7所示,输出电压稳定约在1.8 V,纹波3 mV,状态机输出ent32s1最终稳定在100,系统保持在G=1/2转换比下。其中,第1行是输出电压,第2、3行是拓扑结构控制信号,第4行是PSM的控制信号。仿真结果汇总表如表4所示。 图5 Vin=2.8 V,IL=4 mA仿真结果 图6 Vin=3.6 V,IL=4 mA仿真结果 图7 Vin=4.2 V,IL=4 mA仿真结果 图8给出系统在不同输入电压和负载的情况下对输出电压的影响波形图。其中,第1行是输出电压,第2、3行是拓扑结构控制信号,第4行是PSM的控制信号,第5行是负载电流波形。 图8 动态负载仿真结果 表4 不同输入电压和负载情况下输出变化表 从表4可看出,输出电压稳定在1.8 V附近,且随着负载电流的减小,输出电压纹波也随之减小,纹波基本能保持在20 mV以内。表4中转换效率1为采用状态机后的系统效率,转换效率2为采用逻辑电路的系统转换效率。从转换效率的角度来说,和以传统逻辑电路作为模式控制相比较,没有明显提高,但相比单一转换比,在不同的输入范围内采用多种转换比,使系统平均效率有效提高。从测试结果还可以看出,由于采用数字状态机,电荷泵能快速地响应负载的变化。当负载跳变时,比较器立即检测到输出电压的变化,数字状态机即可根据比较器给出的结果以及当前工作状态在一个周期(2 μs)内完成逻辑判断同时给出控制信号切换到相应的低增益或增益跳变模式。 开关电容DC-DC转换器相对于线性调制器而言,具有较高的转换效率,相对于电感式DC-DC转换器而言,由于没有电感元件的存在,大幅降低了芯片占用面积且没有电磁干扰,从而符合便携式电子设备发展趋势,通常被用作便携式电子设备的电源解决方案。本论文在现有开关电容DC-DC研究基础上,采用状态机进行控制增益跳变,在输入电压和负载允许范围内进行仿真,使输出电压稳定在设定值附近并限制电压纹波,同时提高了转换效率。 [1] Jaeseo Lee,Hatcher G,Vandenberghe L,et al.Evaluation of fully-integrated switching regulators for CMOS process technologies,Very Large Scale Integration (VLSI) systems[J].IEEE Transactions on Circuit,2007,43(6):1017-1027. [2] Somasekhar,Dinesh Srinivasan,Balaji Pandya,et al.Multi-phase 1GHz voltage doubler charge-pump in 32nm logic process[C].Symposium on VLSI Circuits,2009:16-18. [3] Bhattacharyya K,Mandal P.A low voltage,low ripple,on chip,dual switch-capacitor based hybrid DC-DC converter[C].21st International Conference on VLSI Design,2008:661-666. [4] 张杰,殷亮,潘姚华,等.采用有限状态机控制的升降压双通路高效率电荷泵[J].固体电子学研究与进展,2010,30(2):262-268. [5] 邓莉.升降压双通路电荷泵转换器的研究与设计[D].杭州:浙江大学,2007. [6] 毕查德·拉扎维.模拟CMOS集成电路设计[M].陈贵灿,程军,张瑞智,等,译.西安:西安交通大学出版社,2002. [7] Ramadass Y K,Chandrakasan A P.Voltage scalable switched capacitor DC-DC converter for ultra-low-power on-chip applications[C].Power Electronics Specialists Conference,IEEE,2007:2353-2359. [8] Hanh-Phuc Le,Sanders S R,Alon E.Design techniques for fully integratedswitched-capacitor DC-DC converters,solid-state circuits[J].IEEE Journal of Solid-State Circuits,2011(3):2120-2131. [9] Angkititrakul S,Milpitas C A,Hu H.Design and analysis of buck converter with pulse-skipping modulation[C].Power Electronics Specialists Conference,IEEE,2008:15-19. [10]Bayer E,Schmeller H.Charge pump with active cycle regulation-closing the gap between linearand skip modes[C].Power Electronics Specialists Conference,IEEE 31st Annual,2000:1497-1502. [11]Le H P,Seeman M,Sanders S R,et al.A 32 nm fully integrated reconfigurable switched-capacitor DC-DC converter delivering 0.55 W/mm2at 81% efficiency[C].Solid-State Circuits Conference Digest of Technical Papers (ISSCC),IEEE International,2010:210-211. State Machine Control Based Buck Type Switched Capacitor DC-DC Converter ZOU Zhipeng,BU Gang,ZOU Lu (College of Electronic and Information Engineering,Nanjing University of Aeronautics and Astronautics,Nanjing 210016,China) We propose a control means based on the multi-gain mode conversion based on the state machine control.The system uses the gain hopping technique to switch the mode and the pulse skipping modulation (psm) to change the switching frequency according to the load current and input voltage.Thus,the output voltage will be stable and the system conversion efficiency can be improved.The gain hopping module is automatically controlled by a digital state machine,which is designed and simulated in a CSMC 0.5 μm CMOS process.The result of spectreverilog simulation shows that the state machine can accurately control the switch of three gains and the change of switching frequency.Besides,it could generate the stable output voltage of 1.8 V and attain the expected purpose. capacitor array;gain hopping;digital state machine;pulse skipping modulation 2014- 11- 01 邹志鹏(1990—),男,硕士研究生。研究方向:数模混合集成电路设计。E-mail:lucifersk@163.com。邹鹭(1989—),女,硕士研究生。研究方向:模拟射频集成电路设计。 10.16180/j.cnki.issn1007-7820.2015.05.019 TN492 A 1007-7820(2015)05-063-05

4 数字状态机的设计

5 仿真与测试结果

6 结束语