基于DSP芯片的音频信号滤波系统设计

2015-08-10杨丽丽张醒芝

林 琳,杨丽丽,张醒芝

(新疆轻工职业技术学院 信息与软件分院,新疆 乌鲁木齐 830021)

CMOS技术的出现和进步,1982年推出了基于CMOS的浮点DSP芯片。AT&T公司于1984年推出的DSP32.是第一个高性能浮点DSP。1990年推出了浮点DSP芯片MC96002。可见从80年代以来,DSP芯片的发展突飞猛进,逐渐决定电子产品的更新换代。从运算速度看,DSP芯片关键的乘法器部件从40%降到5%以内,片内RAM数量增加一级以上。引脚数量增加到200个以上,大大提高了芯片灵活性。本文介绍了基于TMS320C5416DSP芯片的音频信号滤波系统,结合音频编解码TLV320AIC23芯片,FLASH存储器等实现语音录放器硬件的设计;接着以CCS环境下的C语言为软件设计。将语音信号输入后,经AIC23进行采样后保存在外扩存储器中,再经过DSP带缓冲串口MCBSP 2读入DSP,经过FIR滤波器滤除信号中的噪声,最后进行离散傅里叶快速变换。

1 硬件设计方案

本系统采用DSP芯片TMS320C5416和TLV320AIC23音频编解码芯片实现系统的软硬件设计,并在此基础上完成语音信号的采集、播放、存储、分析功能。文中包括3部分:音频信号采集、DSP芯片处理信号、Flash存储器。系统总体设计结构如图1所示。

图1 系统总体结构计图Fig.1 The system overall structure

TMS320C5416是文中采用的主芯片,是一款低功耗、高性能的DSP芯片,主要功能包括采集语音信号、存储以及控制模块间通信等,将音频信号经过采集和压缩后存放到Flash存储器中。AIC23的高性能立体声信号的输入支持MIC和LINE?IN两种方式,可配置寄存器选择,并且具有可编程增益调节。其内部集成模数和数模转换部件,采用先进的采样技术,采样范围在8K~96K之间。

本设计的从芯片TLV320AIC23音频编解码芯片,是立体声音频Codec芯片,主要负责对语音信号的A/D转换,采样编码及滤波,该芯片是理想的音频模拟器件,应用广泛;DSP芯片三个中有两个缓冲串口MCBSP0和MCBSP1负责控制音频芯片AIC23,其中MCBSP0串口是SPI接口,实现语音数据的发送和接收,MCBSP1串口是 I2S接口,任务是写控制字;Flash存储模块可快速访问、可电擦写,即使停电信息也不会丢失数据的存储器,而且成本很低,可靠性高、稳定性强,容量大有几GB,外形小巧等特性,进行读取和存储操作为载体。

1.1 系统硬件电路设计

本系统采用的DSP芯片TMS320C5416,最高频率可达160MIPS,系统实时性良好;音频编解码芯片TLV320AIC23采样精度在16~32位。上述两种芯片的结合是解决移动音频录放系统、现场采集语音的理想设计。TMS320C5416的3个MCBSP可以方便地实现AIC23之间的控制和通信。AIC23是可编程芯片,其内部含有11个16位寄存器,由MODE引脚选择控制接口采用SPI或者I2C哪种工作方式,MODE=0采用I2C模式;MODE=1表示采用SPI模式。

AIC23独立的控制口接收控制器的命令字,而独立的数据接口交换DSP语音数据。为DSP提供工作时钟的是12M外部晶振。本系统C5416DSP的MCBSP0连接AIC23的控制接口,MCBSP1连接AIC23的数据接口。TMS320C5416DSP连接TLV320AIC23的接口框图如图2。

图2 TMS320C5416DSP和TLV320AIC23的连接电路框图Fig.2 Connect the TMS320C5416DSP circuit diagram and TLV320AIC23

1.2 TMS320C5416DSP模块设计

本次设计采用TMS320C5416芯片,其内部128K*16的RAM,能有效提高系统的集成度和总体性能。另外它还有3个多通道缓冲串口,提供128个通道。C5416芯片的特点有:工作频率可达160 MIPS;可以访问的数据存储空间64K、I/O空间64K。

TMS320C5416和TLV320AIC23连接的引脚如下:BCLKX0/1:传输时钟信号,是多通道缓冲串行接口发送器的串行移位时钟信号,复位时,默认为输入。当OFF为低电平,BCLKX进入高组态;TMS320C5416连接FLASH器件时,DSP芯片每次采集32位的语音数据,依次从左声道开始往右声道写入Flash器件进行存储。

1.3 TLV320AIC23语音采集及回放接口电路模块

AIC23芯片内部集成了ADC和DAC,兼容C5416的输入/输出电压,它的数字接口和DSP的MCBSP端口无缝连接。AIC23采用先进的Sigma-delta过采样技术,将大部分的噪声转移到阻态,采样频率范围8K~96K提供4种16 bit、20 bit、24 bit和32 bit的采样数据,ADC和DAC的输出信噪比分别达到90 dB和100 dB。

TLV320AIC23与TMS320C5416连接的引脚图如下。BCLK:I2S数字音频接口时钟信号,串行数据传输时钟,当主模式是AIC23时,由AIC23产生BCLK且由它传输给DSP,此时的频率仅为主时钟的1/4,当从模式时,DSP产生BCLK;DIN:I2S格式输入给D/A转换器;DOUT,立体声ADC产生,I2S格式A/D转换器串行数据输出;LRCIN/LRCOUT:I2SD/A和A/D转换器字时钟信号,主机模式下,AIC23产生该信号发送给DSP,从机模式下,由DSP产生;SCLK:控制端口串行时钟输入;SDIN:控制端口串行数据输入,控制协议,传输配置数据;/CS:在SPI模式下,是数据锁存控制端,在I2C模式下,作为外设7位地址的末位;XTI/MCLK:外部时钟输入。本文中AIC23由外接的晶振提供工作时钟,TLV320AIC23从电路模块电路如图3。

图3 TLV320AIC23从电路模块电路Fig.3 TLV320AIC23 from the circuit module circuit

1.4 语音数据存储接口电路模块

本文的语音数据存储模块采用32M*8位的Flash存储空间,能够满足文中对存储器芯片的容量以及读取语音信号速度。Flash存储器内存放录音和放音系统数据。Flash的构成是由一组可独立擦除的1KB区块,擦除一个区块将使该区块全部复位为1。Flash存储器每个区块的基地址都固定不变。Flash存储器在存储器中处于起始位置,一般从0开始。下图4为Flash存储模块电路图。

Flash存储器是一种不挥发性内存,存储特性相当于硬盘,因此成为便携式数字设备的存储介质,同时Flash存储器采用串行结构,读写单元以页和块为单位,容量可以很大,成本低廉,而且又能确保数据读写的正确性。闪存的I/O端口有8位,数据传送的方式是轮流传送命令字。DSP采集到的32位语音数据,通过外部总线分4次,从左往右声道写入闪存中。

1.5 电源接口模块

图4 Flash存储模块电路Fig.4 Flash memory module circuit

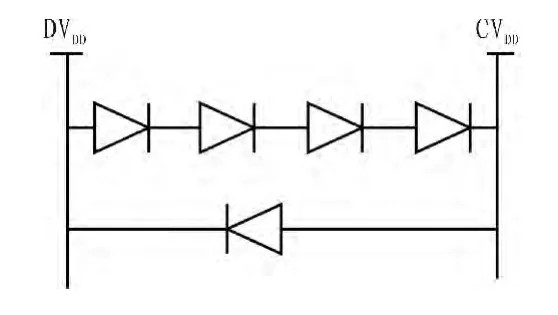

TMS320C5416DSP的供电结构采用双电源器件芯片,内核电源CVDD和I/O电源DVDD,需要考虑相对电压和上电次序。两种供电控制策略不同:DVDD是3.3 V单电源上电,而CVDD只加载1.6 V,降低供电是想要降低芯片的功耗。双供电模式可以消除电源间的延时。在理想状态下,I/O电源和内核电源应该同时加电,但实际情况下想要做到并不容易。如果不能同时加电,需要根据引脚电平对工作模式进行配置,内核要优先于I/O供电,要求一种电压要低于操作电压,另一个电压供电时间不能超出要求。上电过程中,要保证I/O缓冲接收到正确的内核输出,并防止系统的总线冲突。加电次序主要取决于内部静电保护电路如图5所示。

图5 内部静电保护电路Fig.5 The internal static protective circuit

图6中可见,需要DVDD不超出CVDD 2 V,于是采用4个二极管降压,而内核电源不能超过I/O电源电压0.5 V,因此只用一个二极管,否则容易损坏芯片。

2 系统软件设计模块

本语音录放系统的软件环境是DSP集成开发环境IDE提供成熟的核心功能和便捷的图形可视化工具,使得设计更快。CCS2.0提采用图形接口界面,有编辑工具和工程管理工具,提供软件开发、程序调试和仿真环境,集成了汇编器、编译器、建库工具等。CCS集成的代码调试工具具备各种调试功能,同时支持汇编和C/C++语言,本系统的程序软件均采用C语言混合编写。既容易调试,又能提高软件的执行效率,能对DSP进行指令级仿真和实时数据分析。同时它还具有丰富的库函数。

本系统的软件部分主要是从现场线路输入和麦克语音所采集到的信号,收集并存储到Flash存储器中,由滤波后播出信号,并将信号变换到频域,即FFT离散傅立叶快速变换。

2.1 语音分析子模块

现场输入的语音信号,送入立体声音频编解码器AIC23中,AIC23控制芯片内寄存器,将信号A/D转换,用数字计算机处理数字信号,然后由数字滤波器滤波,再送到Flash存储器暂存。数字滤波器是一个离散时间系统。程序语音模块处理过程:首先初始化系统,包括设置时钟发生器、AIC23的初始化、多通道缓冲、工作变量的初始等。

语音分析程序模块处理过程:TLV320AIC23初始化,语音录音数据读取后存入数据缓冲区,调用FIR数字滤波器滤波,效果突出,然后将数字语音信号暂存在闪存内,最后由耳机发出,同时进行FFT离散快速变换算法。语音数据输出到MCBSP。语音分析子程序模块流程图如图6所示。

图6 子程序模块流程图Fig.6 Subroutine module flow chart

2.2 数字滤波器设计

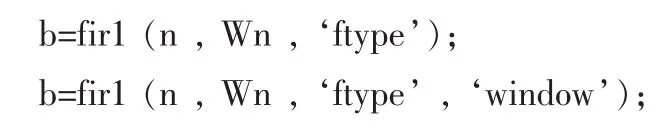

使用窗函数的有限长,实现加窗线性相位FIR数字滤波器,能够满足转移序列或脉冲响应的常见问题。

n为滤波器的阶数,Wn为截止频率,ftype决定滤波器类型,high时为高通滤波器,stop时为带阻滤波器。window采用窗函数类型,是一种通过截短和计权的方法使无限长非因果序列成为有限长脉冲应响应序列的设计方法,其默认值为汉明窗,w=hamming(n),产生一个n点的汉明窗函数。编写matlab程序,生成FIR系数存放在FH[n]中,程序运行后在显示区显示结果。

FFT是快速计算DFT的高效方法,能够显著降低运算量,大大提高DFT运算速度。大部分DSP芯片能在单指令周期内完成乘法累加运算。FFT算法是利用DFT系数的特性,合并运算,将长序列转换为短序列DFT,以减少运算量。FFT算法的实现过程:

1)把N点的 时域信号分解成N个时域信号,单点组成信号,并计算出频谱。

2)输入数据的比特反转,即将输入序列整理成位序颠倒的次序。位码倒置可以提高程序执行速度和存储效率。

3)实现N点复数FFT,执行3个循环套计算FFT变换,最内层都进行蝶形运算,第一级、第二级、第三级至第log2N级都是蝶形运算。序列点数N=2m,N为2的整数幂的FFT算法。

4)估计功率普 X(k)=∑X(n)WnkN,X(k)一般分成虚部和实部,计算时将FFT算法变换好的数据求平方和。

2.3 控制寄存器程序设计

本文的TLV320AIC23利用串行传输数据。前半部分数据控制所需存放寄存器地址,后半部分将所要写入的值保存在寄存器中。采用两个8 bit处理串行传输的控制数据。结合实际本文对于I2C写入模块采用汇编语言。

DSP通过I2C总线将配置命令发送到AIC23,完成初始化配置,然后AIC23开始工作。AIC23的初始化记录在一个数组中,利用串口发送命令,采用循环方式发送。AIC23数据写入时序图如图7。

图7 AIC23控制寄存器数据写入时序Fig.7 AIC23 control register data write timing

如图中所示B[15~9]是记录控制寄存器的地址,B[8~0]是要写入的值被保存在寄存器中。

3 结 论

文中设计了TMS320C5416DSP芯片的音频信号滤波系统,结合音频编解码TLV320AIC23芯片、FLASH存储器等完成语音录放器硬件的设计过程;软件设计分为语音设计子程序和控制寄存器程序设计。在CCS环境下的C语言编程,将外部输入的语音信号,经AIC23进行采样后保存在外扩存储器中,再经过DSP带缓冲串口MCBSP 2读入DSP,经过FIR滤波器滤除信号中的噪声,最后进行离散傅立叶快速变换再进行播放。

[1]王秋生,孙圣和,郑为民.数字音频信号的脆弱水印嵌入算法[J].计算机学报,2002,25(5):520-525.

[2]陆汝华,段盛,杨胜跃,等.基于CGHMM的轴承故障音频信号诊断方法[J].计算机工程与应用,2009,45(11):223-225.

[3]陈璇,李启海,朱万彬,等.基于声卡和 MATLAB的音频信号的采集和处理[J].长春理工大学学报:自然科学版,2010.

[4]王剑飞,程耀瑜.基于DSP的多路音频信号采集与处理设计[J].光电技术应用,2013,28(4):72-75.

[5]陈宝远,姜海鹏,史玲玲,等.矢量量化的音频信号类型确认算法的研究[J].哈尔滨理工大学学报,2010,15(1):108-111.

[6]张家田,封川川,严正国.基于 DSP的音频信号分析仪设计[J].西安石油大学学报 :自然科学版,2009,24(1):85-88.