基于FPGA的ARM SoC原型验证平台设计

2015-08-02代雪峰

王 丹,代雪峰

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.东北大学理学院物理系,沈阳110004))

基于FPGA的ARM SoC原型验证平台设计

王 丹1,代雪峰2

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.东北大学理学院物理系,沈阳110004))

随着应用需求的不断提升,SoC设计规模急剧增大,功能日益复杂,性能要求也越来越高,如何缩短验证时间,提高验证效率和质量以缩短芯片的生产时间成为当今SoC设计领域中最为关注的课题之一。FPGA原型验证是SoC设计的有效途径。在流片前建立一个基于FPGA的高性价比原型验证系统成为SoC验证的重要方法,可以及时发现芯片设计中的缺陷和错误,同时进行软件程序设计,进而缩短SoC芯片的开发周期。描述了以ARM为核心处理器的SoC设计的FPGA原型验证平台实现过程,介绍了怎样利用该平台进行软硬件协同验证,并在此基础上移植了uC/OSII嵌入式操作系统,对该SoC设计进行系统级验证。

ARM处理器;SoC设计;FPGA原型验证;软硬件协同验证;uC/OS-II操作系统

1 引 言

随着集成电路设计技术和半导体工艺技术的不断进步,IC设计的规模和复杂度迅速增长,SoC(System on Chip)验证工作也越来越困难,验证和调试所占的时间可以达到总工期70%以上,单靠软件仿真,不足以发现一些问题。为了模拟实际应用环境,FPGA作为设计的原型载体,被应用到验证中进行软硬件协同验证,弥补了软件仿真的速度问题,使设计者尽快发现电路中存在的缺陷[1]。下面详细论述了一个以ARM为核心处理器的SoC芯片的FPGA原型验证平台实现过程。文章首先描述了该SoC芯片的系统架构,然后阐述了该SoC芯片FPGA验证平台的硬件设计、软件设计、软硬件协同验证。

2 SoC芯片系统架构

SoC一般是指将微处理器、模拟IP核、数字IP核和各类存储器集成在单一芯片上。SoC不是各个芯片功能的简单叠加,而是从整个系统功能和性能出发,选用合适的平台,软硬结合的设计和验证方法,在一个芯片上实现复杂的功能[2]。所验证的SoC芯片以ARM为核心处理器,具有高度灵活的可配置性,方便集成各种标准接口。

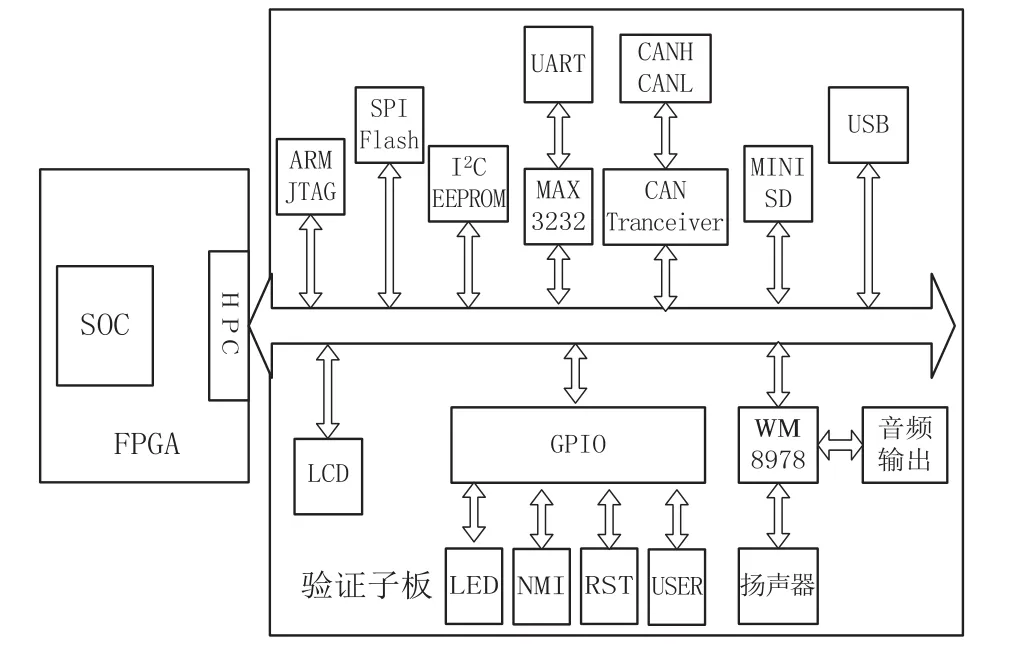

该SoC设计[3]内嵌了256KB的Flash和96KB的SRAM、4个32位定时器、2个看门狗定时器、多个GPIO口、片外设备接口(EPI)、通信接口包括三路UART、三路CAN 2.0控制器、两路I2C模块、两路同步串行接口SPI、一路音频接口I2S、集成MAC和PHY的10/100以太网、USB 2.0 OTG/Host/Device。图1为该SoC的系统架构。

图1 SoC系统架构

3 FPGA验证平台硬件实现

现场可编程门阵列(FPGA)作为集成电路设计技术的第三次重大进步标志,可以使RTL综合的结果直接运行在FPGA芯片上,重用性及现场灵活性较好。SoC设计在流片之前进行系统原型验证,就是将仿真平台硬件化,所以其验证就更具有真实性。

该FPGA验证硬件平台包括FPGA原型验证母板和验证子板。FPGA验证母板与验证子板之间通过HPC接口连接,如图2所示。

该验证系统的FPGA验证母板采用Xilinx公司的TEL-Device Kintex7 325T FPGA开发板[4],该器件采用了TSMC领先的28nm高性能、低功耗工艺。

由于ASIC和FPGA在物理结构上有很大不同,ASIC是基于标准单元库,FPGA是基于查找表结构,所以使用FPGA进行原型验证时,需要把ASIC设计转换为FPGA设计。需要转换的主要有以下几个方面:

图2 FPGA验证平台的硬件结构框图

(1)时钟

在ASIC设计中,用布局布线工具来放置时钟树,利用代工厂提供的PLL进行时钟设计,而在FPGA中通常有一定数量的PLL宏单元,并有针对时钟优化的全局时钟网络,这样的时钟网络可以保证相同的时钟沿到达每个触发器的延迟时间差异是可以忽略不计的,因此时钟单元要进行转换。

(2)Memory

ASIC中的存储单元使用代工厂所提供的Memory Compiler来定制,这是FPGA不能综合的部分,FPGA内部提供了经过验证并优化的存储单元,因此存储单元需要转换为FPGA中的存储单元或者用外部存储器芯片来替换。

(3)I/O

由于ASIC的Pad使用的是ASIC器件库中的单元,FPGA不能直接使用,要替换成FPGA的I/O。

FPGA硬件实现流程如图3所示。SoC系统的RTL设计代码,通过ISE和Synplify软件进行FPGA综合并映射,映射工具根据设置的约束条件对设计代码进行逻辑优化并生成网表,接着进行布局布线,生成配置文件和进行静态时序分析,如果时序不能满足约束,可通过时序报告文件来确认关键路径,进行时序优化。可以通过修改约束条件,或者修改RTL代码来满足时序要求。当时序能满足约束条件时,就可以利用配置文件进行下载。

由于该SoC设计包括丰富的接口模块,为了更好的验证这些接口模块,需要设计一块验证子板,该验证子板包括:

·2MB SPI Flash(W25Q16),通过读写Flash,实现SoC的SPI接口功能测试;

·2048-Bit I2C EEPROM(AT24L02),通过读写EEPROM,实现SoC的I2C接口功能测试;

·4.3英寸QVGA带触摸屏的TFT LCD(分辨率480×272,SSD1963主控),该LCD显示屏是通过EPI接口连接的,通过LCD显示,实现SoC的EPI接口功能测试;

图3 FPGA硬件实现流程

·Micro SD卡座,SD卡是通过SPI接口控制,读写SD卡,实现SoC的SPI接口功能测试;

·CAN收发器SN65VHD230,实现CAN数字信号转为差分信号,用于CAN总线的数据传输。将该CAN接口与其它开发板的CAN接口互连进行收发测试,实现SoC的CAN控制器功能测试;

·USB PHY芯片TUSB1106PWR,通过与PC机的USB接口通讯,实现SoC的USB控制器功能测试;

·Ethernet PHY芯片RTL8201BL,通过与PC机的网口进行通讯,实现SoC的Ethernet MAC功能测试;

·1个232串口收发器芯片MAX3232,实现UART信号的电平转换,通过与PC机的UART接口通信,实现SoC的UART控制器功能测试;

·1个I2S音频编解码芯片(WM8978)。通过I2C接口实现对该音频编解码器的控制,通过I2S接口传输音频数据,扬声器可播放音频,实现SoC的I2C和I2S接口功能测试;

·1个Reset按钮,用于系统复位,1个NMI按钮,用于产生不可屏蔽的中断信号,1个用户自定义的按钮,用于测试SoC的GPIO输入功能;

·1个电源指示LED灯,显示供电系统是否正常,3个LED灯,用于测试SoC的GPIO输出功能;

·1个JTAG接口,用于调试和下载测试程序;

·验证子板的电源及时钟均来自于FPGA母板。

4 FPGA验证平台的软件实现[5-6]

前一部分主要介绍了FPGA验证平台的硬件部分,在这个硬件平台上运行的程序就是验证平台的软件部分。软件部分的实现方式有两种:一种是编写汇编和C代码直接在平台上运行,此种方法用于验证单个功能模块,不能并行工作;另一种是先将嵌入式操作系统移植到平台上,然后在操作系统的基础上用C语言编写验证代码,此种方法适用于系统级验证。

4.1 模块级验证

验证平台的软件集成开发工具使用的是IAR Embedded Workbench,这是一套用于编译和调试嵌入式系统软件程序的开发工具,支持汇编、C和C++语言。它提供完整的集成开发环境,包括工程管理器、编辑器、编译链接工具和C-SPY调试器。

软件实现主要包括:启动代码、驱动程序、应用程序三个部分。

启动代码是系统上电后执行的第一段代码,主要完成系统的初始化,为系统运行准备好软硬件环境。该部分代码的设计由汇编完成,实现的功能为:①定义入口地址;②建立异常中断向量表;③初始化外部存储器;④初始化堆栈指针;⑤进入到C程序。

驱动程序是硬件的接口,应用程序只有通过这个接口才能控制硬件工作,离开驱动程序,硬件模块是无法工作的。为了方便用户使用,可以将驱动程序开发后,以API函数的形式提供给用户使用。

应用程序是在驱动程序的基础上,直接针对特定的应用场景或者特定的功能测试而开发的软件代码。

启动程序运行后,完成最基本的初始化工作,然后应用程序直接调用驱动程序中的API函数,针对模块的功能,或者模拟用户的使用场景,对SoC设计中的各个模块进行功能验证。该部分工作是分别对各个模块的功能进行验证,能够及时发现各个模块的设计缺陷,是系统级验证的基础。

4.2 系统级验证

实时操作系统是嵌入式系统的灵魂,它对整个系统进行硬件资源管理、多任务协调调度、任务间同步和通信及存储管理。在SoC上移植嵌入式操作系统并开发测试程序,可以对整个SoC进行集成后的系统级验证,也是一种更为有效的验证方式。现在流行的嵌入式操作系统有很多种,如Linux、WinCE、uC/OS-II、VxWorks、Andrio操作系统等,主要阐述在该SoC运行uC/OS-II[7]及上层应用程序来验证与测试该SoC系统的设计。采用uC/OS-II来验证与测试该SoC设计,是因为uC/OS-II具有如下显著优点:

·开放源码。测试人员可以根据自己的验证与测试需要直接修改uC/OS-II源码。

·精简小巧。这使得软件虚拟仿真在花费较少时间的情况下便可以检测到SoC逻辑设计错误。

·易裁减。测试人员可以根据自己的需要集中测试某个IP核设计。

·多任务。由于uC/OS-II支持多任务,所以在系统级测试时,可以使多个IP核并发工作。

uC/OS-II的移植只需要修改与处理器相关的代码,在uC/OS-II内核源码中与操作系统相关的源码涉及三个文件:os_cpu.h、os_cpu_a.s、os_cpu_c.c。

(1)os_cpu.h

包括了用#define定义的与处理器相关的常量、宏和类型定义。需要根据ARM处理器的特点修改系统数据类型定义、栈增长方向定义、关中断和开中断定义、系统软中断的定义等相关源码。

(2)os_cpu_a.s

这部分需要对处理器的寄存器进行操作,需要修改四个子函数:OsstartHighRdy()、OSC_txSw()、OSIntCtxSw()、OSTicklSR()。

(3)os_cpu_c.c

该文件中共定义了6个函数,需要修改的函数是OsTaskstklnit(),其他的函数无需修改,是对系统内核扩展时用的。

uC/OS-II提供了任务调度的内核和一些系统服务。开发底层驱动需要为系统编写中断处理控制程序和各个模块的驱动程序。在底层设备驱动开发成功后。再为各个模块编写一些专门用于测试其功能的应用层任务,并给各个测试任务赋予不同的优先级,使它们在uC/OS-II操作系统并行运行起来。通过稳健地运行uC/OS-II操作系统,验证各个模块能否在系统环境下并行正常工作,即进行集成后的系统级验证。

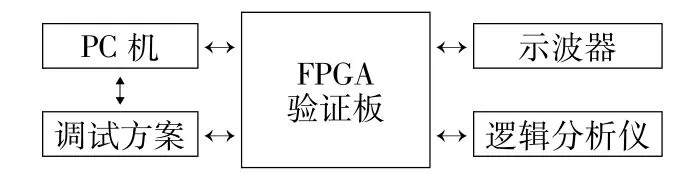

5 基于FPGA的软硬件协同验证[8]

软硬件协同验证是一种在硬件设计确认制造之前,验证软件在设计的硬件上能否正确运行的过程,使软件和硬件同时得到验证。PC机上编写好的测试程序,可以通过仿真器,下载到验证板的存储系统中,SoC设计中的ARM核心处理器,读取并执行存储器中的指令,控制外围模块工作,从而验证SoC的设计功能是否正确。基于上面的原理,整个FPGA软硬件协同验证平台架构如图4所示。该系统分为:PC机部分、验证板部分、调试方案。其中PC机负责配置文件的产生与配置,激励数据的收发与测试结果的读取;验证板部分包括FPGA验证母板及验证子板,FPGA验证母板实现整个SoC设计,是被测试的设计部分;验证子板包括各种接口模块芯片,与SoC设计中同种类型的接口模块之间进行通信,测试其功能是否正确。调试方案负责控制监测运行结果。三者相互配合,共同完成整个SoC系统的验证。具体功能说明如下:

图4 软硬件协同验证平台架构

(1)PC机部分

>生成配置FPGA的BIT流文件,并通过JTAG口配置FPGA;

>编写调试测试程序,并对FPGA中实现的SoC设计进行调试下载;

>与FPGA中实现的SoC设计进行通信,接收测试程序运行的结果或控制测试程序的执行流程。

(2)验证板部分

该系统的验证板包括FPGA开发母板和验证子板两部分,共同实现下面的功能:

>FPGA开发母板中实现SoC设计,是被测试的部分;

>验证子板包括各种接口模块的芯片,与SoC设计的接口通信;

>接收PC机发送的测试程序和测试数据;

>运行测试程序形成运行结果;

>将运行结果发送PC机。

(3)调试方案

FPGA实现的功能趋于复杂化,其调试也越来越困难,很多时候仅凭很少的输入/输出信号,很难判断设计是否有问题以及设计的症结所在,因此,硬件调试中非常有必要深入FPGA内部去了解数据的运算、存储、流动是否正常,主要采用断点调试、串口显示运行结果、示波器和逻辑分析仪等调试手段。

6 结束语

阐述了SoC设计的FPGA原型验证的软硬件实现,在芯片流片前,通过这个验证平台对SoC设计进行功能测试,一方面可以加快验证的速度,迅速发现设计中的问题,另一方面方便进行软件开发,从而大大缩短了项目的开发周期。

[1] M.Abramovici,C.Stroud,M.Emmert.Using Embedded FPGAs for SoCYield Improvement[J].39th Design Automation Conf.2002:10-14.

[2] 杨杰林.基于嵌入式处理器的片上系统设计和应用[D].西安:西安电子科技大学,2004.

Yang Jie-lin.Based on the design and application of embedded system on chip[D].Xi'an:Xidian University,2004.

[3] 夏宇闻.Verilog数字系统设计教程(第2版)[M].北京:北京航空航天大学出版社,2008.

XIA Yu-wen.Verilog digital system design(Second Edition)[M].Beijing:Beijing University of Aeronautics and Astronautics Press,2008.

[4] 田耘,胡彬.Xilinx ISE Design Suit 10.x FPGA开发指南:逻辑设计篇[M].北京:人民邮电出版社,2008.

Tian Yun,Hu Bin.Xilinx ISE Design Suit 10.x FPGA Development Guide:Logic design articles[M].Beijing:People’s Posts and Telecom-munications Press,2008.

[5] 周立功.ARM嵌入式系统基础教程(第2版)[M].北京:北京航空航天大学出版社,2008.

ZHOU Li-gong.ARM Embedded System Essentials(Second Edition)[M].Beijing:Beijing University of Aeronautics and Astronautics Press,2008.

[6] 杜春雷.ARM体系结构与编程[M].北京:清华大学出版社,2003.

DU Chun-lei.ARM architecture and programming[M].Beijing:Tsinghua University Press,2003.

[7] Jean J,Labrosse.MicroC/OS_II The Real-Time Kernel(Second Edition)[M].USA:CMP Books,2002.

[8] 詹瑾瑜.SoC软/硬件协同设计方法研究[D].成都:电子科技大学,2005.

ZHAN Jin-yu.Research on collaborative design method of hardware and software of SOC[D].Chengdu:University of Electronic Science and technology,2005.

Design of Prototyping Method Based on FPGA for ARM SoC Verification

Wang Dan1,Dai Xuefeng2

(1.The47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China;2.Physics Department,Collage of Sciences,Northeast University,Shenyang 110004,China)

With the application requirements constantly promoting and the SoC design size growing,the function is gettingmore and more complex and the higher requirements are generated for the performance as well.So how to shorten verification time and improve efficiency and quality of test chips to reduce the production time has become one of the greatest concern issues in today's SoC designing field.FPGA prototype verification is an effective verification way of SoC design.FPGA prototype verification system is becoming very important to build a prototype of the SoC before taping out.It can find the shortcomings and mistakes in the chip design in time,and also can save the developing timewith software programme design at the same time.In this paper,the implementation of FPGA prototyping verification platform for ARM SoC design flow is described,aswell as how to progress hardware and software co-verification.As a result,the uC/OS-II embedded operating system is transplanted and the system level verification of the SoC design is conducted.

ARM processor;SoC design;FPGA prototype verification;Hardware and software co-verification;uC/OS-IIembedded operating system

10.3969/j.issn.1002-2279.2015.06.004

TN492

B

1002-2279(2015)06-0015-04

王丹(1982-),女,辽宁省锦州市义县人,工程师,硕士,主研方向:嵌入式微处理器设计、验证。

2015-03-11