CCD遥感相机视频电子系统FPGA软件集成化设计

2015-07-24马飞,刘琦,尹娜,荣鹏

马 飞,刘 琦,尹 娜,荣 鹏

(北京空间机电研究所,北京 100094)

0 引 言

CCD遥感相机视频电子系统主要包括焦平面电路、信号处理电路和积分时间电路3部分。其中焦平面电路的功能是为CCD提供驱动时序,确保CCD正常工作;信号处理电路的功能是将CCD输出的模拟信号转换为数字信号,并进行信号的合成处理;积分时间电路的功能是为信号处理电路提供工作所需的主时钟、行同步等信号,并向信号处理电路发送指令信息[1⁃3]。

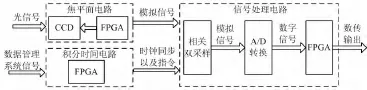

在传统设计方法中,3部分电路具有各自的FPGA作为核心处理器控制实现相应功能,焦平面电路FPGA软件为CCD器件提供具有严格相位关系的时序驱动信号,并调整CCD的级数,使CCD工作在满足要求的状态下;信号处理电路FPGA软件驱动A/D转换器完成A/D转换,接收数字图像信号并按照要求的格式转换成数据传输格式后输出给数传分系统;积分时间电路FPGA软件主要功能是将数据管理系统的指令解析后发送给信号处理电路,并生成主时钟和行同步信号提供给信号处理电路。采用传统设计方法实现的视频电子系统框图如图 1 所示[4⁃5]。

图1 传统视频电子系统框图

传统设计方法中,由于每部分电路采用单独的FP⁃GA进行控制,使得软硬件集成度不高的同时,增加了研制成本,同时由于FPGA设计的降额要求,造成一定程度的逻辑资源浪费。为提高视频电子系统的集成度以满足相机小型化的需要,本文研究并设计了一种新的视频电子系统软件架构,在传统视频电子系统的基础上,只保留信号处理电路的FPGA,将焦平面电路和积分时间电路FPGA软件的功能集成到信号处理电路的FPGA中,实现软件集成化设计,以达到提高集成度节约软硬件资源的设计目的。

1 集成化设计实现

1.1 集成化方案设计

集成化设计后的视频电子系统框图如图2所示。焦平面电路简化为只有CCD的工作电路,工作时序由信号处理电路FPGA提供;主时钟和行同步信号由信息处理器发送,信号处理电路FPGA接收到主时钟和行同步信号后自己产生内部工作所需要的各种时钟信号和内部行同步信号。

图2 集成化设计后的视频电子系统框图

与传统设计相比,集成化设计后的视频电子系统只保留了信号处理电路的FPGA作为核心处理器,减少了FPGA的使用数量,但相比较而言,集成化设计后的FP⁃GA设计复杂度比传统设计有所增加。

1.2 软件集成化设计

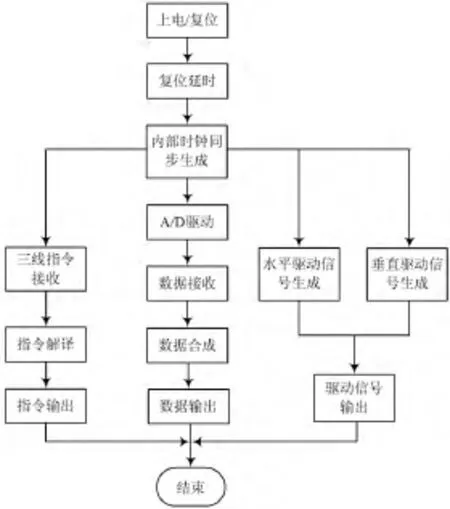

积分时间FPGA软件主要包括时钟行同步产生和指令解码两部分,时钟行同步产生部分根据外部输入的主时钟和行同步信号产生内部工作所需要的各种时钟和内部行同步信号,指令解码部分接收外部遥控三线指令,并对指令进行解码,按照指令要求实现相应功能;焦平面FPGA软件主要包括水平驱动信号生成和垂直驱动信号生成两部分,分别产生CCD工作所需的水平驱动时序信号和垂直驱动时序信号;信号处理FPGA软件主要包括A/D驱动和数据合成两部分,A/D驱动部分产生A/D转换器的驱动信号,确保A/D转换器正确实现A/D转换,数据合成部分对接收到的图像数据进行合成处理,并按照要求的格式将合成后的图像数据输出。在集成化设计中,三部分软件在一片FPGA中实现,软件集成化设计的软件架构如图3所示。

集成后的FPGA软件工作流程如图4所示。上电或复位后,对复位信号延时以确保复位信号稳定有效,之后根据信息处理器发送的主时钟和行同步信号生成内部工作需要的各类时钟信号和行同步信号。时钟和行同步信号生成之后软件工作流程按照积分时间软件、信号处理软件和焦平面软件三部分软件的功能分为3个主要流程:

(1)接收三线指令并对指令进行解译,将解译后的指令输出到相应模块进行响应;

(2)产生A/D转换器的配置驱动信号,驱动A/D转换器对图像模拟信号进行A/D转换,并接收转换后的图像数据,按照相应格式将数据合成之后输出;

(3)产生CCD正常工作所需的水平驱动时序信号和垂直驱动时序信号,驱动CCD正常工作,为A/D转换器提供正确的像元信号。

图3 集成化软件架构

图4 FPGA软件工作流程

2 集成化设计难点分析

2.1 多时钟域设计

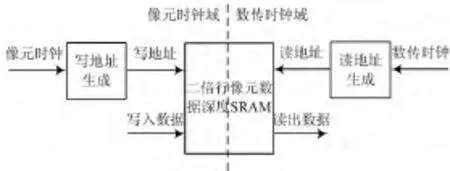

集成化设计将积分时间软件、焦平面软件和信号处理软件的功能集成在一片FPGA中,集成后的软件各个功能模块工作在多个时钟域下。积分时间功能模块工作在主时钟域,焦平面功能模块工作在像元时钟域和二倍像元时钟域,信号处理软件工作在主时钟域、像元时钟域和数传时钟域。数传时钟为主时钟二分频,二倍像元时钟为主时钟四分频,像元时钟为主时钟八分频。主时钟从信息处理器发送到信号处理FPGA,数传时钟、像元时钟和二倍像元时钟通过对主时钟分频计数产生,由于FPGA内部布局布线产生的延时,在逻辑设计过程中,4种时钟并不按照同源时钟来处理,而是按照异步时钟进行逻辑设计,在跨时钟域进行数据传输时,通过2次采样操作或者通过存储器隔离的方式完成。

图像数据从像元时钟域向数传时钟域的传输设计如图5所示。利用FPGA的内部存储资源开辟二倍每行像元数深度的双端口SRAM,写入端开放给像元时钟域,读出端开放给数传时钟域。写入端利用像元时钟产生写地址,将A/D转换后的像元数据写入到SRAM中。读出端利用数传时钟生成读地址,将像元数据在数传时钟域读出,之后在数传时钟域下完成数据的合成与输出。

图5 像元数据跨时钟域传输

2.2 数据处理乒乓设计

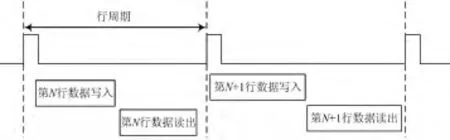

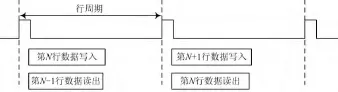

数据处理要求在一个行周期内将图像数据接收完毕并按照数据传输格式发送完毕。若采用当前行数据在当前行实时合成输出的处理方式,需要等待一行数据全部写入存储器后才能够进行读出操作,写入和读出操作顺序进行,需要更快地处理速度或更长的行周期时间,如图6所示。

图6 数据实时处理方式示意图

为保证在处理速度和行周期时间不变的情况下一行的数据能够在一行内完全发送完毕,采用乒乓处理的方式完成数据的读写操作,如图7所示,首先要开辟二倍像元数据深度的SRAM,在第个N行周期将第N行数据写入SRAM的高半地址,同时从SRAM的低半地址读出第N-1行的数据;在第N+1行,将第N+1行数据写入SRAM的低半地址,同时从SRAM的高半地址读出第N行的数据。乒乓处理后读出与写入操作互不影响,可以并行进行,从而保证在行周期不变的情况下,完成一个行周期内整行数据的完整输出。

2.3 软件标准化设计

软件集成化设计将积分时间软件、焦平面软件和信号处理软件集成在信号处理电路的FPGA中,与分别利用三个FPGA实现各自的功能相比较,其软件复杂度更高,FPGA资源占用率更高,对逻辑的优化设计要求也更高。

图7 数据处理乒乓操作示意图

为了使软件更优化,减少资源的占用率,软件集成化不是简单地将3部分软件以3个单独模块的形式例化在同一个顶层逻辑中,而是通过软件标准化设计,在保证积分时间软件、焦平面软件和信号处理软件各部分的功能正确实现的前提下,将具有相同逻辑功能的逻辑模块在一个模块中实现,减少逻辑的设计冗余,使实现相同功能所需要的逻辑资源尽量少。比如,3部分软件都需要对主时钟进行分频,在集成化设计中,采用标准化的分频模块,在一个模块中实现对主时钟的分频,分频后的时钟再送给各部分功能模块使用,从而实现逻辑的优化。

经过标准化模块的采样和逻辑功能的整合,使得3部分软件更好地成为一个逻辑整体,在确保功能实现的同时,使软件的可读性更强,软件架构更加清晰明确,有利于后期的软件维护。

3 测试与分析

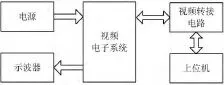

视频电子系统软件功能测试方案如图8所示。将视频电子系统与视频转接电路相连,再通过视频转接电路与上位机相连,视频转接电路模拟信息处理器为视频电子系统提供主时钟、行同步以及遥控三线信号,同时接收视频电子系统输出的数传数据,转换为Cameralink数据格式,通过Cameralink接口将图像数据传输到上位机,在上位机上通过图像采集软件观察图像数据输出是否正确。示波器用来观察各接口时序波形,以确定各输入输出信号时序关系是否正确。

图8 测试方案框图

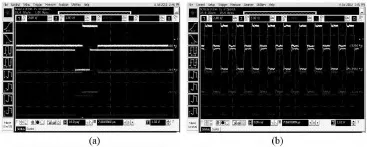

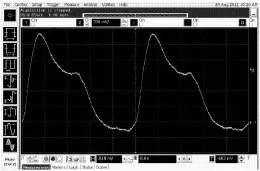

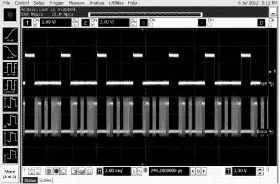

利用示波器观察FPGA输出给CCD的垂直转移驱动信号图9(a)和水平转移驱动信号图9(b)所示。与CCD所要求的时序关系相比较,FPGA所产生的水平转移信号和垂直转移信号满足CCD的驱动要求,能够驱动CCD正常工作,CCD输出的像元信号如图10所示,能够满足设计要求。

图9 水平转移和垂直转移驱动信号波形

图10 CCD像元波形

利用示波器观察信号处理电路输出的数传格式数据和同步信号波形如图11所示,其中同步信号低电平对应有效数据,数传输出满足功能和性能要求。

图11 数传数据与同步信号波形

图像数据经过视频转接电路发送到上位机,通过上位机图像采集软件观察图像数据,从而确定数据传输是否正确。通过上位机发送级数和增益调整指令,观察图像变化,从而判断指令响应是否正确。上位机图像如图12所示,(a)是增益0 dB,CCD级数为3级时两个谱段的图像;(b)是增益0 dB,CCD级数为5级时两个谱段的图像;(c)是增益6 dB,CCD级数为3级时两个谱段的图像。从图12中图像的比较可见,增益指令与级数指令能够正确响应,随着增益与级数提高,图像数据的值增大,图像变亮。通过上位机图像采集软件和示波器波形的观察,可以确认集成化设计之后的视频电子系统软件满足各项功能要求。

图12 上位机像元数据图像

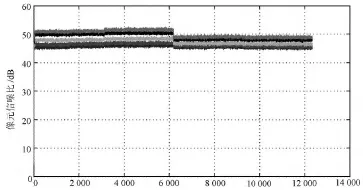

利用Matlab图像处理软件对上位机的图像进行处理,计算出图像的信噪比,如图13所示。

图13 不同级数下信噪比

从图中可见,随着级数从1~5级的增加,图像的信噪比也随之增加,在级数为1级时信噪比为46 dB,在5级时信噪比达到52 dB,软件性能能够满足要求。

4 结 语

通过对CCD遥感相机视频电子系统各部分软件的集成化处理,实现了视频电子系统的小型化与集成化设计。将传统视频电子系统中的积分时间软件、焦平面软件和信号处理软件集成在同一片FPGA中,简化了系统设计复杂度。通过采用跨时钟域信号处理和标准模块的使用,使得集成后的软件工作更加稳定可靠,效率更高。通过对硬件输出信号的观测与分析,以及对上位机图像的信噪比等指标的分析,本文提出的FPGA软件集成化设计方法能够满足CCD遥感相机对视频电子系统的功能与性能上的要求,具有很高的工程应用价值。

[1]陈瑞明,吴淞波,王建宇,等.对地观测高分相机视频电子学集成化技术[J].航天返回与遥感,2013,34(3):34⁃40.

[2]达选福,王怀义,李涛,等.基于集成信号处理芯片的CCD相机视频电子学系统设计[J].航天返回与遥感,2008,29(4):30⁃35.

[3]贾建军,舒嵘,王斌永.无人机大面阵CCD相机遥感系统[J].光电工程,2006,33(8):90⁃93.

[4]郑亮亮,张贵祥,金光.高速多光谱TDI CCD成像电路系统[J].中国光学,2013(6):939⁃944.

[5]胡君,王栋.空间光学遥感器的多光谱TDI CCD信号检测与生成[J].光学精密工程,2009,17(8):1810⁃1818.

[6]李爱玲,张伯珩,张健,等.多光谱CCD相机图像采集系统的设计[J].微计算机信息,2011,27(15):15⁃16.

[7]宁永慧,马天波,郭永飞.基于TDI CCD的成像FPGA系统软件设计与应用[J].现代电子技术,2011,34(2):167⁃169.

[8]武奕楠,吕增明,张宇,等.基于FPGA的多通道面阵CCD成像系统设计[J].光机电信息,2011,28(6):39⁃43.

[9]李红梅,陈敏聪,陈子瑜,等.线阵CCD数据获取方法研究与设计[J].电子测量技术,2008,31(6):124⁃126.

[10]刘蕾,江洁,张广军.基于CPLD的线阵CCD的驱动及数据采集[J].电子测量与仪器学报,2006,20(4):107⁃110.

[11]陈世平.空间相机设计与试验[M].北京:中国宇航出版社,2003.