基于云模型进化算法的硅通孔数量受约束的3D NoC测试规划研究

2015-07-18许川佩陈家栋万春霆

许川佩 陈家栋万春霆

(桂林电子科技大学电子工程与自动化学院 桂林 541004)

基于云模型进化算法的硅通孔数量受约束的3D NoC测试规划研究

许川佩 陈家栋*万春霆

(桂林电子科技大学电子工程与自动化学院 桂林 541004)

针对硅通孔(TSV)价格昂贵、占用芯片面积大等问题,该文采用基于云模型的进化算法对TSV数量受约束的3维片上网络(3D NoC)进行测试规划研究,以优化测试时间,并探讨TSV的分配对3D NoC测试的影响,进一步优化3D NoC在测试模式下的TSV数量。该方法将基于云模型的进化算法、小生境技术以及遗传算法的杂交技术结合起来,有效运用遗传、优胜劣汰以及保持群落的多样性等理念,以提高算法的寻优速度和寻优精度。研究结果表明,该算法既能有效避免陷入局部最优解,又能提高全局寻优能力和收敛速度,缩短了测试时间,并且优化了3D NoC的测试TSV数量,提高了TSV的利用率。

3维片上网络;硅通孔;云模型;进化算法

1 引言

随着集成电路技术的发展,3维片上网络(Three-Dimensional Network-on-Chip, 3D NoC)的思想逐步出现在集成电路设计中。3D NoC通过硅通孔(Through-Silicon-Via, TSV)技术将各层2维结构芯片互连起来,其优点表现为:一是缩短了全局互连;二是降低了延迟,提高了系统性能;三是由于缩短了连接线的长度而降低了功耗;四是增加了封装密度,减小了芯片面积[1]。然而,由于TSV占用了芯片大量区域(特别是为TSV需要而留出的“禁用区”),使得芯片上的IP核数量大大减少,另外,生产TSV的开销很大[1],这些因素使得设计者在设计3D NoC时需要考虑TSV数量问题,而对于数量受约束的3D NoC测试,需要有针对性的测试方案,从而提高TSV的利用率,优化测试时间。

目前对于3维集成电路的测试规划研究,文献[2]提出了在各层均衡分布IP核,并对IP核进行测试调度的方法,减小了芯片的测试时间;文献[3]提出了在TSV数量受约束条件下,如何减少3D SoC中分立电路测试时间的方法,但不能保证优化全局的测试时间;文献[4]研究了在TSV数量一定的情况下减少3D SoCs测试时间的方法,以及提出优化TSV数量的方法。国内外学者针对NoC的测试研究主要集中在2D NoC,例如文献[5]探讨了NoC重用对系统测试的影响,并提出了抢占式和非抢占式测试调度的测试方法,但该方法缺乏快速有效的规划算法;文献[6]在文献[5]的研究基础上,将NoC测试规划与遗传算法结合起来,从而优化了测试时间。

由于3D NoC的测试规划问题是一个NP难问题,本文基于高精度寻优的云模型进化算法,研究3D NoC 测试资源(I/O端口,TSV)分配策略,以提高资源利用率,优化测试时间,并探讨TSV数量及其在各层间的分配对3D NoC测试的影响。

2 3D NoC结构

3D NoC结构主要有3D mesh 结构,蝶形胖树结构,XnoTs结构等。目前学者主要研究的是3D mesh 结构。典型的3D mesh结构NoC如图1(a)所示,相邻两层对应的上、下两个路由节点均由TSV连接起来。

3D NoC的一个基本单元如图1(b)所示。其中R表示路由节点(Router),每个路由节点有7对I/O端口,其中一对端口与本地芯核(core)相连,其余6对分别与相邻的东(E),南(S),西(W),北(N),上(U)以及下(D)6个方向的路由节点相连,垂直方向U和D的互连线由TSV构成,U和D方向均包含up-to-down TSV和down-to-up TSV[7],为了便于研究,文中称一个垂直方向含有1束TSV。互连的两个节点之间的通信可以采用全双工的通信方式。core表示一个资源节点,可以是处理器内核、存储器、FPGA或IP核等。NI表示网络接口,是路由节点与资源节点的通信接口。

很明显,TSV越多,各层资源节点之间的通信就越便捷。然而,由于芯片生产开销以及芯片面积的限制,3D NoC在设计和使用时需要考虑TSV数量问题。本文在TSV数量受约束的前提下对3D NoC进行测试规划研究。

图1 3D mesh 结构NoC及其基本单元

3 TSV数量受约束的3D NoC测试规划

3.1 NoC测试规划

为减少硬件开销,NoC测试采用重用片上网络的测试访问机制[6,8,9],即复用片上网络的路由节点和通道(channel)等资源,实施并行测试以提高测试效率。在测试core时,测试矢量由输入端口送入网络,按一定的路由算法到达core,生成的测试响应以同样的路由算法到达输出端,由外部的测试响应接收并分析,完成一个核的测试。

本文采用非抢占式的测试策略,给每个测试核分配一条测试路径,包括输入端口、输出端口,以及相应的通道,一旦某测试核的测试路径确定之后,该路径上的所有资源(输入/输出端口,通道)将预留给该测试核,其他核的测试矢量以及测试响应不得抢占,直到该核测试完毕为止。

TSV数量受约束的3D NoC测试时,测试数据需要经过特定的I/O端口以及特定的TSV才能完成芯核的测试,因此,本文研究的测试规划问题可描述为:给定NC个待测核core, NIO对I/O端口,各层的TSV数量,在确定的路由算法下,如何将输入/输出端口,以及TSV合理有效地分配给各个core,确定这些core的测试路径,并且在功耗允许的条件下,无冲突地调度各个待测核的测试顺序,使整体测试时间最小。

3.2 路由算法及路径冲突

在测试过程中,采用XYZ路由算法,数据包由源节点沿X方向传输,到达与目标节点x坐标相同的路由节点后,转向Y方向进行传输,到达与目标节点y坐标相同的路由节点后转向Z方向传输,直至目标节点。

根据已制定的测试策略,一旦给某个core分配了输入/输出端口以及TSV等资源,那么按照XYZ路由算法,该core的测试路径便是确定的。由于多个core同时进行测试,如果芯核测试顺序调度不合理,测试路径便有可能产生冲突,即两个core的测试数据在某个路由节点处向相同路由节点进行传输。

3.3 测试时间以及功耗约束

(1)测试时间 多对端口并行测试规划如图2所示,总测试时间取决于测试时间最长的那对I/O端口。

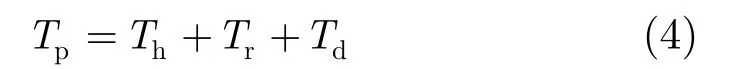

总测试时间为

图2 多对端口并行测试规划图

其中,Ti代表core i分配到第j对I/O端口上的测试时间,NC代表core的数量,Tkx(j)为第j对I/O端口上测试资源冲突或功耗过大时的空闲时间,NIO为I/O端口对数,单个核的测试时间Ti包括测试数据的传输时间以及测试所消耗的时间,即Ti=Ttr+Tte,而在核进行测试的同时,其余数据包已相继传入网络,因此数据传输所耗的时间主要是第1个测试数据包从输入端口至测试核以及最后1个测试响应数据包从测试核至输出端口所耗的时间。

式中Tp(first), Tp(last)分别为第1个测试数据包和最后1个测试响应数据包在两个路由节点之间的传输时间,hopi和hopo分别代表数据包输入以及输出测试核所经过的路由跳数。

Th为路由器处理数据包头所耗的时间,Tr为确定路由的时间,Td为数据传输至下一路由节点所耗的时间。

通常,核的测试时间远大于数据包的传输时间,因此本文不考虑传输时间的影响。

(2)功耗约束 考虑到异构NoC每层的功耗不同,因此有必要将功耗约束到每一层。对于每个时隙(time slot),第 l层的功耗必须满足:

单个核的功耗包含传输功耗和测试功耗,即P=np ·Pp+Pc,其中np是该核的数据包数量,Pc是该核的测试功耗,Pp是一个数据包通过路径的传输功耗。

其中Pr代表数据包在一个路由器上的传输功耗,Pxy代表数据包在一条水平通道上的传输功耗,Ptv代表数据包在一条TSV上的传输功耗,Nr, Nch, Ntv分别代表数据包经过的路由器数量,通道数量以及TSV数量,其中通道数量包含了TSV数量。

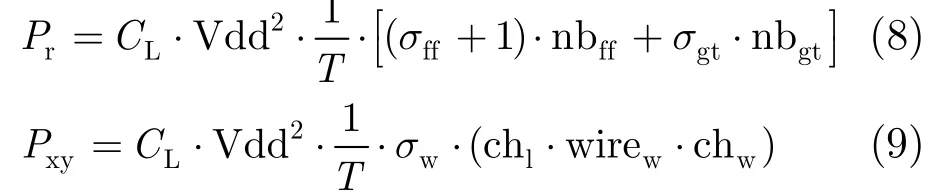

其中CL, T和σw分别表示负载电容(技术有关常数)、时钟周期以及开关因子。变量nbff, nbgt, σff和σgt分别表示活性元件的数量(触发器或者逻辑门)及其通过的路由器上相应的开关因子[10]。

Pr, Pxy以及Ptv均为常数。采用文献[10]的功耗模型,Pr=10, Pxy=2。由于互连TSV很短,比水平互连通道小两个数量级,所以功耗远远小于水平通道的功耗,考虑到TSV的工艺与分布结构还没有统一,本文设定Ptv=1。

4 基于云模型进化算法的测试规划方法

3D NoC测试规划属于NP难问题[11],而基于云模型的进化算法[12-14]是一种高精度寻优的算法,将该算法与3D NoC测试结合起来,可以迅速而且准确地找到最优的资源(I/O端口,TSV)分配方案,从而提高TSV利用率,优化测试时间。

4.1 算法的相关设计

假定NoC有L层,将底层称为第 0层, 其上各层按顺序依次称为第 1层,第 2层……。核数量为第 l层的核数量,各层核的编号依次0, 1,…,-1。TSV数量其中为第 l层的TSV数量,各层TSV编号依次为0, 1,…,-1。设I/O端口对数为NIO,则I/O端口对的编号依次为0, 1,…,NIO-1。

本文以3层NoC为例来进行说明。

4.1.1 染色体 对于本文所研究的问题,一条染色体就是完成一个待测核测试的一种资源(I/O端口,TSV)分配方案。设定染色体Ali=(G0, G1, G2, G3, G4),其中G0~G4为染色体中的基因。G0所含信息为I/O端口编号,G1~G2依次为测试数据从输入端口传输至core li先后经过的各层TSV编号,G3~G4依次为测试数据从core li传输至输出端口先后经过的各层TSV编号。各基因在3D NoC中的映射如图3所示。染色体所包含的信息为测试core li时测试数据所经过的关键通道。例如染色体A26= (0, 0, 0, 3, 3)所含信息为测试第2层第6号芯核时,测试数据先后经过的关键通道依次为输入0→底层TSV0→第1层TSV0→core li→第1层TSV3→底层TSV3→输出 0。需要注意的是,当测试底层芯核时,测试数据不需要经过任何TSV,此时G1~G4为无效基因,用‘X’来表示,染色体标志为(G0,X,X,X,X);当测试第1层芯核时,测试数据不需要经过第2层以上的TSV,此时G2和G3为无效基因,染色体标志为(G0,G1,X,X,G4)。

图3 染色体结构映射图

4.1.2 个体 个体为完成对所有待测核进行测试的一种资源分配方案。一个个体有Nc条染色体,Nc为待测核的数量。例如,A00=(2,X,X,X,X), A10= (1,1,X,X,2),20= (0,0,0,3,3)构成一个个体,该个体有3条染色体,代表NoC有3个待测核,分别分布在第0, 1, 2层,每条染色体所含的信息代表着一个待测核的测试路径。

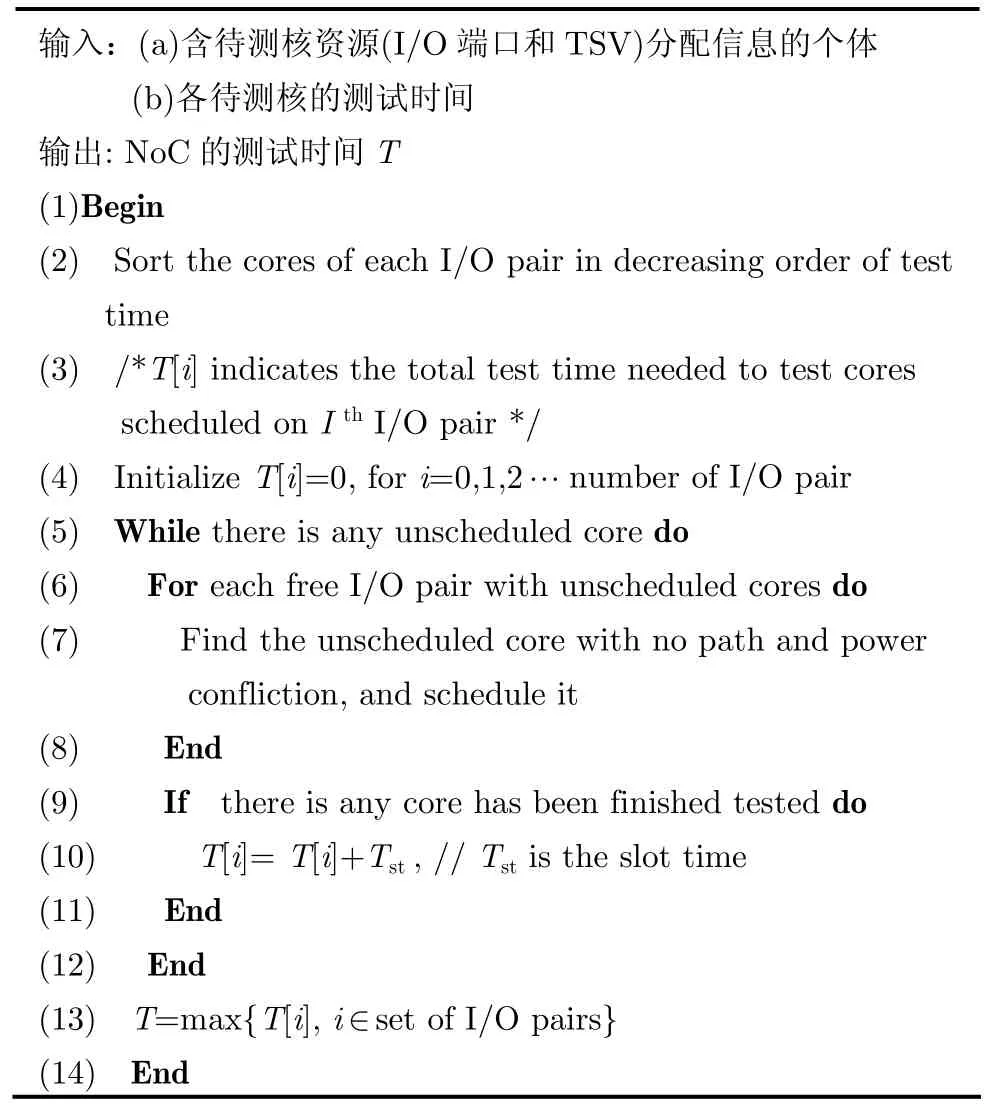

4.1.3 个体适应度值 文中以完成对所有core进行测试所需的时间作为个体的适应度值,测试时间越小,该个体越优秀。测试时间依据式(1)计算。在测试过程中,需要对分配在各I/O端口对上进行测试的芯核进行调度,尽量缩短测试时间。本文采用非抢占式的测试调度策略,测试调度的伪代码如表1所示。

表1 测试调度的伪代码

4.1.4 云模型 本文选用1维正态云模型C(Ex, En, He)实现进化过程。期望Ex代表父代的优良特性;熵En表示云模型中云滴距离期望值Ex的离散范围;超熵He是熵的不确定度,反映了云模型中数值的凝聚程度。正态云模型更新云滴过程:

(1)生成期望值为En,方差为He的正态随机数,

(2)以Ex为期望值,()2为方差生成正态随机数x, x称为云滴;

更新个体时,Ex取个体的基因值,En代表基因在进化过程中变异的范围,En=e/c1,其中e为各基因取值范围。当Ex=G0时,e值为I/O端口对数;当Ex=G1或G4时,e值为底层TSV数量;当Ex=G2或G3时,e值为上层TSV数量。He代表了进化过程中搜索寻优的范围,He=En/c2。c1, c2均为可控参数。在进化过程中,出现跨代精英即更优秀个体时,应调节c1, c2使En和He减小,缩小搜索范围,进行局部求精;当平凡代数(连续不出现跨代精英的代数)达到一定值时,应调节c1, c2使En和He增大,从而扩大搜索范围,进行局部求变操作。

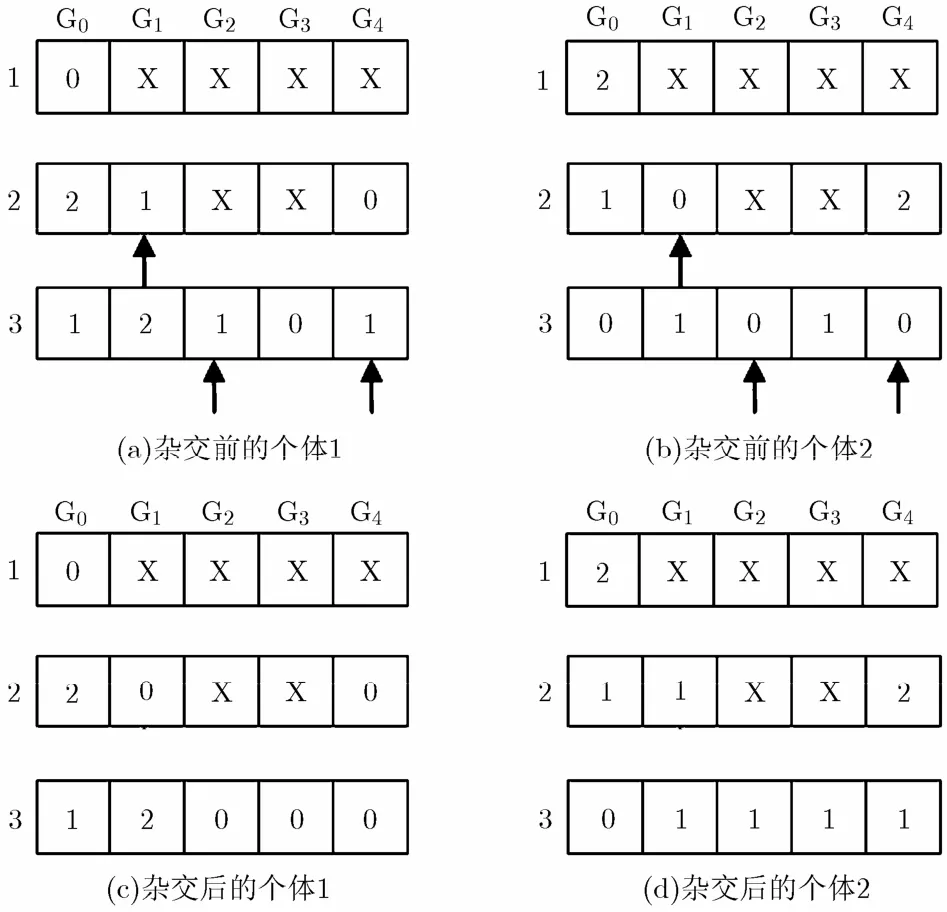

4.1.5 交叉变异 包括杂交、自交以及变异。杂交过程采用轮盘赌的方式选取2个个体,越优秀的个体被选中的概率越大,个体的基因交换方式采用多点交换,同样以轮盘赌的方式选择需要交换的染色体,含有有效基因较多的染色体被选择的概率较大,基因交换如图4所示。自交过程是将一个个体中不同染色体的相同位置的有效基因进行交叉互换。变异则是利用随机函数更新个体中的某些有效基因。交叉变异后的个体需要检验是否合格:个体中所有G0基因的值是否涵盖了所有I/O端口编号值,若不是,则个体不合格,需重新进行交叉变异。

4.2 算法设计

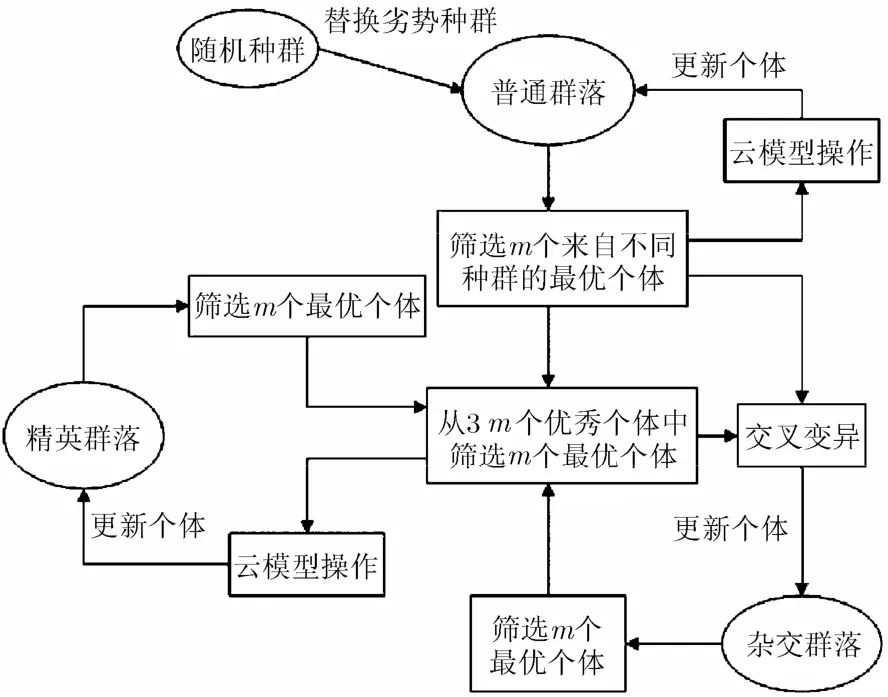

普通的云模型进化算法一般只针对一个群落,从该群落中选取优秀的种子进行个体更新,当连续n代没有发现精英个体才进行交叉变异操作,而且各种子个体间有血缘关系,进化代数达到一定时,各个体的基因有很大相似度,最终导致算法寻优速度慢、容易陷入局部最优等情况。为了克服这些缺点,算法中设计了普通群落、杂交群落以及精英群落3个群落,群落的系统结构如图5所示。普通群落为整个系统提供多样基因,用以维持系统的多样性,主要利用了生物学中物以类聚的小生境原理,该群落中的各种群之间没有血缘关系。根据优胜劣汰的生存原则,利用随机种群替换普通群落中的劣势种群。实验证明,杂交群落中往往比较容易产生优良品种,因此在算法中加入杂交种群以加快寻优速度。精英群落挑选优良品种进行繁殖,该群落使用云模型进化来更新个体以提高寻优精度。

图4 基因交换

图5 群落的系统结构框图

3个群落之间的关系体现在种子筛选的环节。

种子筛选:从普通群落中筛选m个来自不同种群的最优个体,作为更新普通群落的种子(普通种子)。从所有群落中选取m个不同的最优个体,作为更新精英群落的种子(精英种子)。将普通种子与精英种子作为杂交群落的种子。由于普通群落中的各种群之间没有血缘关系,因此普通种子之间有较大的基因差异,可以保持系统的多样性,避免算法进入局部最优。精英种子主要利用优良种子进行繁殖,加快算法寻优速度。

整个算法流程如图6所示,主要步骤有:初始化群落、适应度评估、个体选择、个体更新等。

(1)初始化群落:利用随机函数产生n个个体,n为群落规模,每个个体含有Nc个待测核的测试资源(I/O端口,TSV)分配信息,初始化3个群落。

图6 算法流程图

(2)适应度评估:计算每个个体的测试时间。

(3)个体选择:如前文的种子筛选。

(4)个体更新:该步骤是整个算法的核心部分,包括3个群落的个体更新,其中普通群落和精英群落利用云模型更新个体,过程相似。而杂交群落通过交叉变异来更新个体。

云模型操作:通过正向云发生器来更新每个个体中的基因,无效基因‘X’不需要更新。步骤如下:

(1)设置云模型中的3个特征参数Ex, En, He,设置过程已在4.1节作了分析;

(2)将3个特征参数输入到正向云发生器中,产生一个云滴,即一个新的基因。

(3)重复步骤(1)至步骤(2),直到产生群落所需的个体数为止。此过程中,越优秀的种子产生的种群规模越大。在普通群落中,淘汰掉最劣势的种群,用随机函数补充种群,充分利用自然界优胜劣汰的生存规则,以加快寻优速度。

交叉变异操作:设定杂交概率为0.8,自交和变异的概率均为0.1。在筛选种子时,为了减小近亲杂交的概率,应限定所选种子中最多只有一个精英种子。

5 实验结果与分析

本文选择ITC′ 02 SoC标准电路作为实验对象,采用Visual C++编写程序,其中正向云发生器用MATLAB 7.1的MCC方式与VC混编实现,在Intel(R) core i3 3.1 GHz CPU, 3 G内存Windows XP操作系统下运行。本文基于4×3×3 mesh结构的3D NoC,选取SoC基准电路d695×3(30个内嵌核)和p93791(32个内嵌核)作为研究对象。

实验设定不同的TSV数量,利用本文算法对每种TSV数量的各种分配方案进行测试分析。实验过程中,分别设定I/O端口对数为2, 3, 4和5;测试功耗限制为系统功耗的50%。由于本实验测试的规模较大,为了保证能搜寻到最优测试时间,经过多次实验调整,设定每个群落的规模为1000。

图7给出了各种TSV数量所对应的两种基准电路IP核的最优测试时间。由图7可以看出,I/O端口对数一定时,测试时间随着TSV数量的增加而下降,但当TSV增加到一定数量时,测试时间基本上保持稳定的变化趋势。原因是TSV数量在一定范围内的增加使得测试数据可以在上下层之间畅通传输,但当TSV过多而I/O端口对数有限时,只会造成一些TSV处于饥饿状态,即造成TSV浪费。另外,由图7纵向对比可知,当TSV数量一定时,测试时间随着I/O端口对数的增加而减少,但当TSV数量较少时,上下层间测试数据的传输达到了饱和状态,此时即使增加I/O端口对数,也不能减少测试时间。图7数据表明,对于规模为4 ×3×3的3D mesh 结构NoC, I/O端口对数与TSV数量有一定的匹配关系,当I/O端口对数为2时,在TSV数量为4左右处开始寻得最优测试时间;当I/O端口对数为3时,在TSV数量为6左右处开始寻得最优测试时间;当I/O端口对数为4时,在TSV数量为8左右处开始寻得最优测试时间;当I/O端口对数为5时,在TSV数量为10左右处开始寻得最优测试时间。此时TSV在各层的最优分配方案如表2第3列所示,括号中第1个数据为上层TSV数量,第2个为底层TSV数量。由表2中数据可以看出,在测试模式下,当TSV总数一定时,底层分配的TSV数量多于上层,可以提高TSV的利用率,优化测试时间。

为了验证改进算法(ICEA)的性能,在表2相同的条件下,即I/O端口对数、TSV总数以及TSV分配方案相同,NoC的结构不变,将其与没有采用精英群落、杂交群落以及小生境技术的算法(CEA)进行NoC测试规划研究比较,实验设置CEA的群落规模为3000,最大进化代数设为2000,将研究结果与ICEA的研究结果进行比较,结果如表2所示。由表2的测试时间和寻优代数可以看出,无论在寻优精度还是寻优速度上,算法ICEA都比算法CEA有明显的优势,特别是在I/O端口对数以及TSV总数比较大时,优势更为明显。原因是本文算法将云进化算法与小生境技术以及遗传算法中的杂交技术有效地结合起来,提高了算法的寻优精度和寻优速度。

图7 测试时间与TSV数量关系

表2 最优TSV数量的分配方案以及算法比较

6 总结

本文采用改进后的进化算法对TSV数量受约束的3D NoC进行测试规划研究,并探讨TSV数量优化问题。选取ITC′ 02测试标准电路进行仿真实验,实验结果表明,当I/O端口对数一定时,适度选取TSV数量可以降低测试成本;当TSV数量一定时,底层分配的TSV数量多于上层,可以提高TSV的利用率。实验结果证明,加入小生境技术以及杂交技术的云模型进化算法收敛速度快,利用其对3D NoC进行测试规划研究,可以快速而且精确地找到最优测试方案。

本文提出的测试规划方法针对3D NoC的测试资源分配进行研究,算法将测试数据经过的路径定义为染色体,不依赖于NoC结构,因此适用于不同拓扑结构的3D NoC。不同拓扑结构的3D NoC需要选取合适的路由算法,但不同的路由算法主要影响数据的传输时间,不会影响本方法的应用。

[1] Hwang Yong-joong, Lee Jae-hun, and Han Tae-hee. 3D Network-on-Chip system communication using mini-mum number of TSVs[C]. ICTC 2011, Seoul, Korea, 2011: 517-522.

[2] 欧阳一鸣, 刘蓓, 梁华国. 一种三维SoCs绑定前的测试时间优化方法[J]. 电子测量与仪器学报, 2011, 25(2): 164-169. Ouyang Yi-ming, Liu Bei, and Liang Hua-guo. Optimizing method for pre-bond test time on three-dimensional SoCs[J]. Journal of Electronic and Instrument, 2011, 25(2): 164-169.

[3] Noia B, Chakrabarty K, and Xie Y. Test-wrapper optimization for embedded cores in TSV-based three-Dimensional SoCs[C]. IEEE International Conference on Computer Design, Lake Tahoe, CA, USA, 2009: 70-77.

[4] Roy S K, Giri C, Ghosh S, et al.. Optimizing test wrapper for embedded cores using TSV based 3D SoCs[C]. IEEE Computer Society Annual Symposium on VLSI, Chennai, India, 2011: 31-36.

[5] Cota Érika and Liu Chun-sheng. Constraint-driven test scheduling for NoC-based systems[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2006, 25(11): 2465-2478.

[6] Mali G, Das S, Rahaman H, et al.. Non-preemptive test scheduling for Network-on-Chip(NoC) based systems by reusing NoC as TAM[C]. IEEE Asia Pacific Conference Circuits and Systems, Kuala Lumpur, Malaysia, 2010: 268-271.

[7] Liu C, Zhang L, Han Y H, et al.. Vertical interconnects squeezing in symmetric 3D mesh Network-on-Chip[C]. Asia and South Pacific Design Automation Conference(ASPDAC), Yokohama, Japan, 2011: 357-362.

[8] Sbiai T and Namba K. NoC Dynamically reconfigurable as TAM[C]. 2012 IEEE 21st Asian Test Symposium(ATS), Niigata, Japan, 2012: 326-331.

[9] Amory A, et al.. Determining the test sources/sinks for NoC TAMs[C]. 2013 IEEE Computer Society Annual Symposium, Natal, Brazil, 2013: 8-13.

[10] Cota E, Zeferino C, Carro L, et al.. Reusing an on-chip network for the test of core-based systems[J]. ACM Transactions on Design Automation of Electronic Systems, 2004, 9(4): 471-499.

[11] Chakrabarty K. Test scheduling for core-based systems using mixed-integer linear programming[J]. IEEE Transactions on ComPuter-Aided Design of Integrated Cireuits and Systems, 2000, 19(10): 1163-1174.

[12] 张光卫, 何锐, 刘禹, 等. 基于云模型的进化算法[J]. 计算机学报, 2008, 31(7): 1082-1091. Zhang Guang-wei, He Rui, Liu Yu, et al.. An evolutionary algorithm based on cloud model[J]. Chinese Journal of Computers, 2008, 31(7): 1082-1091.

[13] 许川佩, 姚芬, 胡聪. 基于云进化算法的NoC资源节点优化测试研究[J]. 电子测量与仪器学报, 2012, 26(3): 192-196. Xu Chuan-pei, Yao Fen, and Hu Cong. Optimal test of NoC resource nodes based on cloud evolution algori-thm[J]. Journal of Electronic Measurement and Instrument, 2012, 26(3): 192-196.

[14] 李国柱. 基于云模型的实数编码量子进化算法[J].计算机应用, 2013, 33(9): 2550-2552, 2569. Li Guo-zhu. Real-coded quantum evolutionary algorithm based on cloud model[J]. Journal of Computer Applications, 2013, 33(9): 2550-2552, 2569.

许川佩: 女,1968年生,教授,硕士生导师,主要研究方向为自动测试总线与系统、集成电路测试技术.

陈家栋: 男,1986年生,研究生,研究方向为集成电路测试.

Research on Test Scheduling of 3D NoC under Number Constraint of TSV (Through-Silicon-Vias) Using Evolution Algorithm Based on Cloud Model

Xu Chuan-pei Chen Jia-dong Wan Chun-ting

(School of Electronic Engineering and Automation, Guilin University of Electronic Technology, Guilin 541004, China)

As Through-Silicon-Vias (TSVs) in three-Dimensional Network-on-Chip (3D NoC) accompany some overhead such as the cost and the area, in order to optimize the number of TSVs of 3D NoC in test mode and reduce the test time, a new method using evolution algorithm based on cloud model is proposed to research on the test scheduling of 3D NoC and the impact of TSVs number and their allocation in each layer on 3D NoC test. This method combines the cloud evolution algorithm with niche technology and hybridization technique in genetic algorithm. It uses effectively the concepts of heredity, natural selection and community diversity to improve the quality of the algorithm on optimizing speed and precision. Experimental results demonstrate that the proposed method can not only effectively prevent from running into local optimization solution, but also improve the ability and speed of searching the best solution, and that TSVs number of 3D NoC can be optimized to improve the TSVs’ utilization.

Three-Dimensional Network-on-Chip (3D NoC); Through-Silicon-Via (TSV); Cloud model; Evolution algorithm

TN407

A

1009-5896(2015)02-0477-07

10.11999/JEIT140165

2014-01-24收到,2014-04-24改回

*通信作者:陈家栋 cljxdm@163.com