多晶电阻工艺监控与影响因素研究

2015-07-05张世权马慧红吴晓鸫中国电子科技集团公司第58研究所江苏无锡214035

张世权,马慧红,吴晓鸫(中国电子科技集团公司第58研究所,江苏 无锡214035)

多晶电阻工艺监控与影响因素研究

张世权,马慧红,吴晓鸫

(中国电子科技集团公司第58研究所,江苏 无锡214035)

摘 要:首先介绍了多晶电阻在线监控和工艺控制模块(PCM)监控的两种方法:四探针法和范德堡法,并解决了四探针法在线监控方法多晶电阻波动大的问题;针对生产过程中遇到的多晶电阻偏小问题,通过扫描电镜分析发现多晶晶粒明显偏大,通过对多晶淀积速率的分析确定多晶速率越小,多晶淀积晶粒越大,根据多晶导电理论可知多晶晶粒大,晶粒间界变小,晶粒间界杂质俘获变少,多晶掺杂浓度转化为载流子的比例变高,因此多晶电阻变小。最后根据工程实践列举了影响多晶淀积速率的两大主要因素为多晶淀积温度和多晶炉管维护次数,为保证多晶淀积速率稳定,多晶炉管维护次数尽量少于6次,同时需要对多晶淀积温度进行控制。

关键词:多晶电阻;晶粒;淀积速率;四探针法测试电阻

1 引言

多晶硅薄膜在集成电路制造工艺中被广泛使用[1],主要有多晶硅栅极、自对准硅化物、多晶电阻、多晶发射极及MEMS牺牲层等。多晶电阻由于其和CMOS工艺的较高兼容性和较低的寄生效应,在静态存储器等CMOS工艺电路中有着广泛应用。但由于多晶电阻的波动性较大,影响多晶电阻的因素较多,给多晶电阻的控制带来难题。多数工程研究针对整个多晶电阻流程中的关键控制点比如注入、退火等工序做了详尽分析[2],但针对多晶淀积本身导致多晶电阻变化的原因分析较少。本文针对多晶淀积工艺,分析多晶淀积对多晶电阻影响的根本原因,从而提出多晶淀积工序的控制要求。

常规多晶电阻的整个工序主要为多晶淀积、多晶注入、退火、多晶刻蚀。因此该4步工序的稳定性都直接影响多晶电阻的稳定性,在常规的单步控制中都有各自相应的质量监控。多晶淀积主要监控多晶厚度和片内均匀性,多晶注入监控注入剂量稳定性,退火监控退火电阻稳定性,多晶刻蚀主要监控刻蚀剖面和关键尺寸[3]。

2 问题背景

2.1多晶电阻测试方法

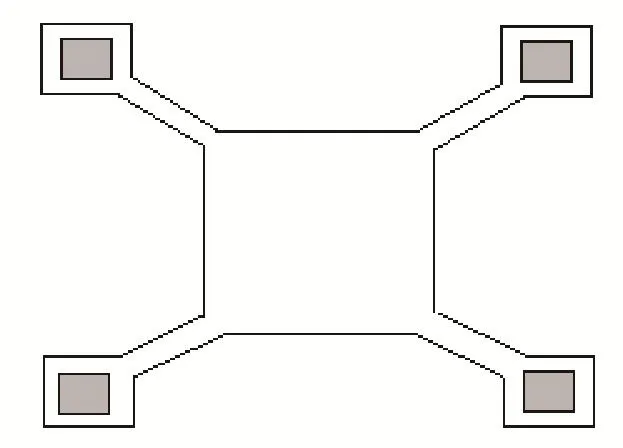

2.1.1范德堡法

范德堡法测试薄膜电阻示意图如图1,正中的正方形是待测的薄层电阻,测量时从正方形任一边的两个欧姆接触点通入电流I,另外一边的两个欧姆接触点测试电压U,Rs=U·I-1[4];生产线PCM多晶电阻监控方式采用范德堡结构测试,该方法测试精确度高,避免光刻腐蚀带来的形貌影响,但该方法监控流程复杂,流片时间长,不适合在线直接监控。

图1 范德堡法测试薄膜电阻示意图

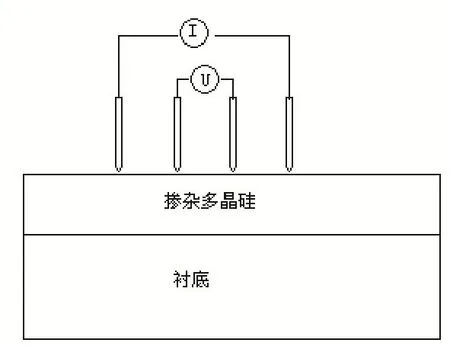

2.1.2四探针法

四探针法测试薄膜电阻示意图如图2,采用四个等间距探针排在一条直线上,通过两根内侧针测试电压,外侧针通过电流,则可计算出该薄层的方块电阻为Rs=C×U·I-1,其中C为修正系数,当样品尺寸远大于探针间距时C=4.532[5]。四探针法测试结果直观,监控流程简单,适合在线测试,但存在和最终结果匹配的问题。

综合以上两种测试方法的优劣,在线测试常用四探针法测试,出线测量采用精度更高的范德堡法测量。

图2 四探针法测试薄膜电阻示意图

2.1.3在线监控流程

普通硅衬底 P型<100> 14~25 Ω·cm衬底材料片,经过氧化层生长、多晶淀积、多晶注入、退火后四探针测试多晶方块电阻。但在监控过程中发现,在线监控结果四探针法测试的结果波动大,且变化趋势有时会误导PCM出片测试结果。经过多次试验和验证发现,四探针法实验过程中对衬底材料片控制较松,每次衬底片材料有相应差异,或采用多次回收片,经过统一材料片并严禁回收使用后确认在线测试和PCM出片测试多晶电阻的趋势基本一致。在线四探针法即可发现多晶电阻的变化趋势,一旦发现异常变化,可不用等待PCM出片后的结果直接排查问题,减少了问题排查时间,也降低了流片风险。

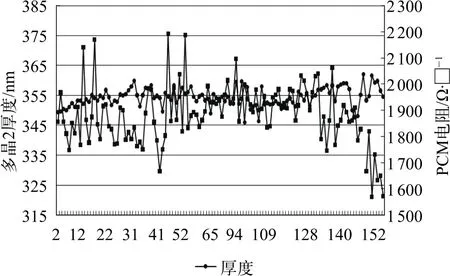

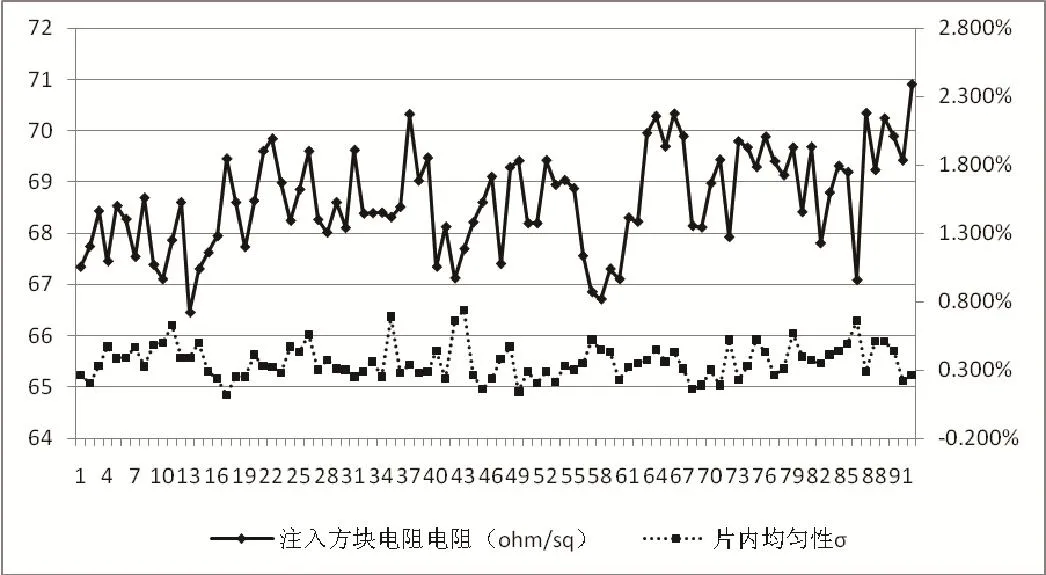

2.2多晶电阻异常现象与背景

在生产线生产过程中,在多晶2电阻各项在线监控和工艺控制均正常的情况下,流片电路的PCM测试电阻急剧下降,如图3。但初步调查多晶淀积厚度整体波动正常,多晶注入退火QC波动正常,如图4。根据常规控制经验已无法判断问题点,因此需要继续深入调查。

3 原因分析

3.1SEM分析

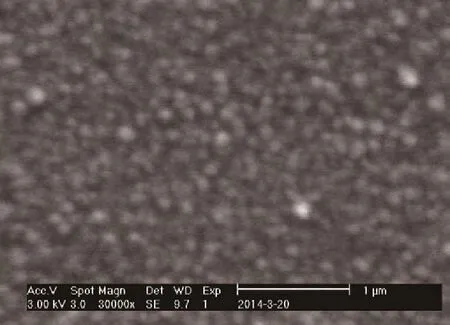

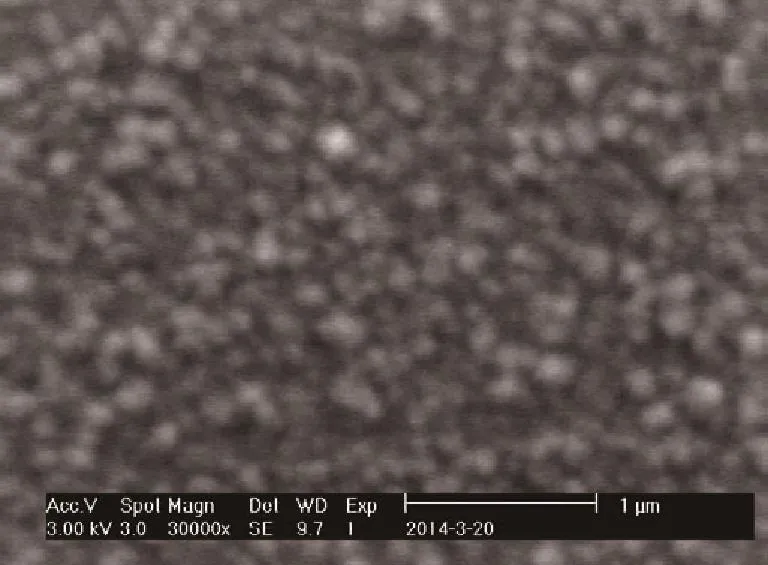

针对正常多晶电阻和偏低多晶电阻的陪片进行SEM分析,表面观察发现正常电阻的多晶晶粒约0.12 μm(如图5),电阻偏低的多晶表面晶粒约0.16 μm(如图6)。因此可知电阻偏低的主要原因是晶粒变大所致。

晶粒变大有两种可能,一种是多晶淀积本身晶粒异常变化,另外一种是退火工艺变化导致多晶晶粒变大。但由于前面常规控制中对多晶注入后退火QC监控可知注入和退火工艺稳定,而多晶工序由于只有厚度监控,未对晶粒进行控制,因此极有可能是多晶淀积工序出现异常。

图 3 多晶电阻(PCM测试)变化趋势图

图 4 多晶注入退火QC控制趋势图

图 5 2 000 Ω·□-1多晶电阻SEM图

图 6 1 600 Ω·□-1多晶电阻SEM图

3.2多晶淀积工艺调查

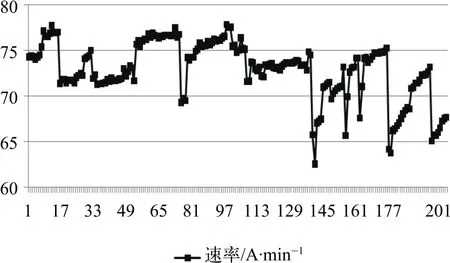

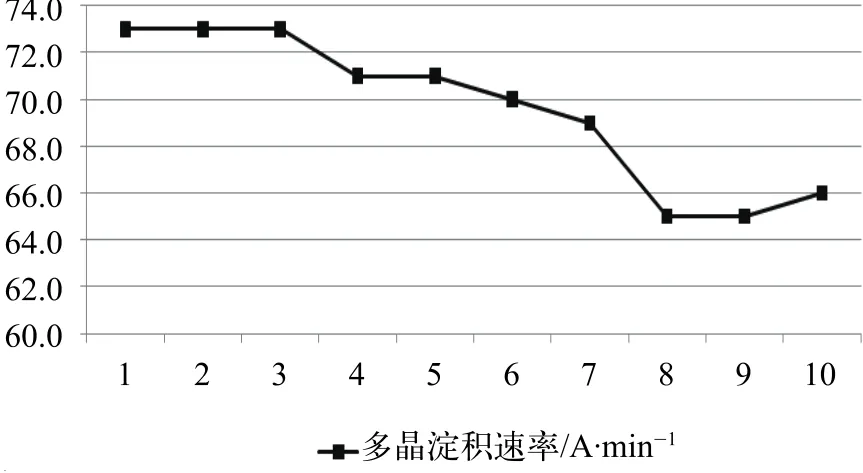

针对多晶淀积过程中的工艺控制要点,对多晶淀积速率进行了排查,图7是同期多晶淀积速率趋势图。

图7 多晶速率监控趋势图

从图7中可看出多晶速率有明显的下降趋势,该下降趋势和多晶电阻下降趋势一致。根据薄膜生长理论和多晶硅薄膜电学性质基本特性[1],多晶硅的导电特性相对复杂,不仅有不同晶向的小晶粒,还有晶粒间界的影响。由于晶粒间界能够对掺杂源进行俘获,这部分杂质无法自由运动,不能全部电离成为载流子。因此晶粒间界越多,意味着俘获的杂质越多,在同样掺杂浓度的情况下,掺杂杂质成为载流子的比例较小,晶粒间界越多则电阻越大。当多晶速率偏低后多晶膜层生长致密,多晶晶粒偏大,晶粒间界变少,掺杂杂质成为载流子的比例增大,因此多晶电阻变小。

3.3多晶淀积速率的影响因素

炉管温度是影响多晶淀积速率的重要工艺参数,温度越高速率越快,多晶晶粒也越大[6]。

影响多晶淀积的另外一个重要因素是多晶炉管的维护次数。随着炉管维护次数的增加,由于炉管每次维护需要用HF酸漂洗管壁,导致管壁越来越薄,影响到炉膛的温度分布和气氛变化,最终导致多晶淀积速率严重下降。根据生产经验,炉管经过6次维护后需要更换新管,旧管无法继续使用。

图8 多晶淀积速率随炉管维护次数变化图

4 结论

多晶电阻在线监控可用四探针方式监控,流程简易,流片周期短,可及时反馈电阻变化情况。但衬底材料需要严格管控,避免材料回收使用。出片后多晶电阻采用范德堡结构测试,可避免线宽变化带来的影响。

多晶淀积过程严重影响多晶电阻,其核心因素是多晶淀积速率发生变化导致多晶晶粒变化。多晶淀积速率越小,淀积越致密,晶粒越大,晶粒间界变少,晶粒间界杂质俘获变少,掺杂杂质变为载流子的比例提高,多晶电阻相应变小。

多晶淀积工序需要严格控制多晶淀积速率,多晶淀积温度、炉管维护频次等都严重影响多晶速率,在生产过程中需要对这些设备参数严格监控,尤其是炉管维护超过6次需要更换新管。

参考文献:

[1] 王阳元,等. 多晶硅薄膜及其在集成电路中的应用[M].北京:科学出版社,2001.

[2] 吴建伟,等. 提高多晶电阻工艺稳定性[J]. 电子与封装,2009, 9(8).

[3] Wolf, Stanley. Silicon for VLSA Era [M]. Volume2: Process Integration, Lattice Press , 1990.

[4] 张军琴,等. 薄层方块电阻自动测量法[J]. 电子测量技术,2000,(2).

[5] 刘新福,等. 四探针技术测量薄层电阻的原理及应用[J]. 半导体技术,2004, 29(7).

[6] M Hamasaki, T Adachi, S Wakayama, M Kikuchi. J Appl. Phys., 1978.

Research of Polycrystalline Silicon Resistance Processing Monitor and Influencing Factor

ZHANG Shiquan, MA Huihong, WU Xiaodong

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214035, China)

Abstract:The paper put forward and makes an overview for two method of testing polycrystalline silicon resistance: four probe method and van der pauw method, which were used in online test and PCM test individually, and then solve the problem of the big fluctuation by four probe test. For production process in the encountered of poly resistance getting small, through the scan electric microscope analysis we found the bigger of crystal grain the smaller of the poly resistance. According to the polycrystalline silicon conductive theory, when the poly grain become lager, the grain boundaries which can capture carrier become smaller, polycrystalline doping concentration into the carrier ratio becomes higher, so the polycrystalline resistance small. According to the engineering practice we found the two leading factors for polycrystalline deposition rate is polycrystalline deposition rate temperature and furnace maintenance number, in order to ensure stable polycrystalline deposition rate, deposition temperature must be controlled and furnace maintenance should be less than 6 times.

Key words:polycrystalline silicon resistance; grain; deposition velocity; process control module

中图分类号:TN305

文献标识码:A

文章编号:1681-1070(2015)05-0033-03

收稿日期:2015-01-17

作者简介:

张世权(1982—),男,甘肃会宁人,2006年毕业于兰州大学微电子学与固体电子学专业,获工学硕士学位,目前从事半导体工艺技术开发和管理工作。