SRAM存储器动态参数测试向量分析

2015-07-05罗喜明张一波湖北航天技术研究院计量测试技术研究所湖北孝感43000中船重工西安东仪科工集团有限公司西安70065

张 吉,罗喜明,王 军,唐 力,张一波(. 湖北航天技术研究院计量测试技术研究所,湖北 孝感 43000;. 中船重工西安东仪科工集团有限公司,西安 70065)

SRAM存储器动态参数测试向量分析

张 吉1,罗喜明1,王 军1,唐 力1,张一波2

(1. 湖北航天技术研究院计量测试技术研究所,湖北 孝感 432000;2. 中船重工西安东仪科工集团有限公司,西安 710065)

摘 要:半导体存储器一般由存储体、地址译码驱动器、读/写放大器和控制电路组成,是一种能存储大量信息的器件,它是由许多存储单元组成的。半导体存储器的测试有功能测试、直流参数测试、交流参数测试,而功能测试和交流参数测试对存储器来说是至关重要的。SRAM(静态随机存储器)的功能测试是通过算法图形发生器产生不同的测试图形,对被测器件各个不同存储单位进行读写操作,以检查其功能。主要讲述了SRAM交流参数测试原理及其测试关键技术,介绍了SRAM交流参数测试的故障模型。通过研究SRAM交流参数测试图形向量,给出了SRAM交流参数测试图形向量的优化方法。

关键词:存储器;动态参数;测试图形

1 引言

半导体存储器一般由存储体、地址译码驱动器、读/写放大器和控制电路组成,是一种能存储大量信息的器件,它是由许多存储单元组成的。每个存储单元都有唯一的地址代码加以区分,而且能存储一位(或一组)二进制信息,半导体存储器是目前应用最广泛的存储器件。半导体存储器的测试也和其他数字电路一样,有功能测试、直流参数测试、交流参数测试,而功能测试和交流参数测试对存储器来说是至关重要的。

2 动态参数测试原理

SRAM的功能测试是通过算法图形发生器产生不同的测试图形,对被测器件各个不同存储单位进行读写操作,以检查其功能。而交流参数测试是测量器件晶体管转换状态时的时序关系。交流测试的目的是保证器件在正确的时间发生状态转换。输入端输入指定的输入边沿,特定时间后在输出端检测预期的状态转换。在具体的SRAM存储器交流测试中,就是利用SP3160V测试系统的时钟发生器对器件的输入端输入技术手册所要求的时钟类型和时钟边沿,并利用算法图形发生器按照预先编写的测试向量规定器件发生状态转换前的状态,在特定时间后利用失效存储器检查转换后的状态是否和预期一致。

3 SRAM交流参数测试关键技术

半导体存储器的功能测试是通过不同的测试图形对被测存储器各个不同的存储单元进行读写操作,以检查存储器的功能是否正确。目前大多数带有存储器测试选件的集成电路测试系统如SP3160II 和SP3160V测试系统均能实现其功能测试。交流参数的测试由于不能融合到该算法图形中,故未能实现交流参数的测试。为了解决SRAM交流参数的测试问题,程序设计通过编制测试图形向量和合理设置时序得以实现。SRAM内部每个存储单元都涉及到交流参数的测试,但是由于存储容量大,比如CY7C1049B-20VI,为512 k×8位的SRAM存储器,在对其进行交流参数测试时,每一个单元需要读写数据28×2次[1],若对所有单元都进行读写操作就需要512 k×28×2 = 262 144 000次,那么所编写的测试向量也就需要262 144 000条。显然在实际测试中这种做法是不科学、不合理的,也不具备现实可操作性。因此,在SRAM存储器交流参数测试中,如何合理选取交流参数测试图形向量,是实现存储器交流参数测试的关键。

4 故障模型

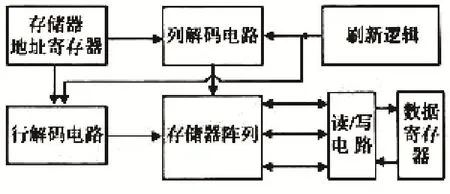

研究存储器的动态参数测试,就必须清楚存储器单元的内部结构,先建立存储器单元的动态故障模型,即要求把物理故障模型化为逻辑故障。典型的SRAM功能模型如图1所示。

对于图1的SRAM功能模型,可见存储器单元主要由三部分组成:读写逻辑模块、地址解码器和存储器阵列。存储单元的动态故障主要表现在三个方面:

(1)读后恢复时间过长,即读出放大器读完一串相同数据以后,不能立即读出与前相反的数据;

(2)写后恢复时间过长,当读周期前有写周期时,读取数据的时间变长;

(3)延时故障,即译码电路需要一定的延迟后才能正确译码。

图1 SRAM功能模型

前两种故障跟读写放大器有关,延时故障则跟地址译码器有关。根据这三种故障模式可知,存储器的交流参数主要与读写放大器及地址译码器有关。故测试交流参数时,不需对所有存储单元进行测试,只需编写不同的测试图形向量分别对读写放大器和地址译码器进行交流参数测试即可。据此,需要对SRAM交流参数测试图形向量进行优化。

5 测试向量分析

5.1读写逻辑模块

对读写逻辑模块的测试即是对存储单元数据线的测试。由于地址解码器的测试总是在假定数据线正常的情况下进行,所以要先进行数据线测试。

图2 RAM的结构图

图2是一个4×4 RAM的结构图,从图中可以清晰看出它内部每一个存储单元内所要存储的4位数据彼此间都是独立的,每位数据的输入或者输出是由片选控制。引起这部分的动态失效原因主要是读写后恢复时间过长。也就是如果写一个存储单元马上就读取同一个单元的数据,可能读到的只是数据线上的数据,而不是实际存储单元的。另外考虑到要测试每根数据线,因此选择任意两个存储单元作为测试单元。选任意一个基地址base_add,选择测试单元的偏移地址为base_add+offset_1base_add+offset_2,则实际测试单元的实际地址分别为base_add+offset_1和base_ add+offset_2。先对base_add+offset_1地址单元写入01010101(55),再对base_add+offset_2地址单元写入10101010(AA),然后先读base_add+offset_1单元,再读base_add+offset_2单元,接着对base_ add+offset_1单元写入10101010(AA),再对base_ add+offset_2单元写入01010101(55),还是选读base_add+offset_1单元,再读base_add+offset_2单元,并做判断。其流程如图3所示。

图3 流程图

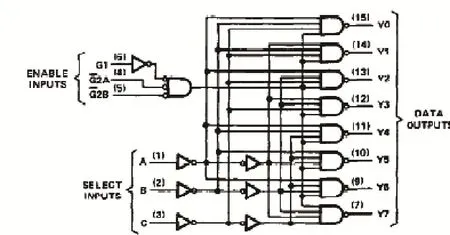

5.2地址解码器测试向量

地址解码器是由多个译码器组成的,延迟时间主要来源于译码器。LS138常被用来作为存储器的译码电路,以LS138为例进行说明,其原理图如图4所示。

图4 LS138原理图

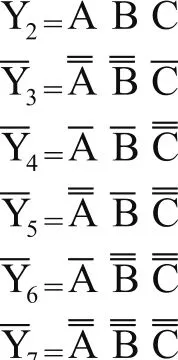

单独分析一个译码器的延迟时间:如选择0地址单元时,地址码ABC为000,也就是译码器的Y0作用,此时,同理得出选择1~8地址单元时[2],地址码经过译码器的变化情况:

由此可见,只有当Y0作用时,它的输入端都只经过一次反相器,所以延迟最小,其余任意一个输出都至少有一个输入端经过2次反相器。而最后到达与非门时,无论3个输入端各自经过了1或者2个反相器件,全部到达与非门的延迟时间,必定是其中一个输入端的最大延迟。所以只需要考察出每一个输入端单独经过2个反相器的延迟时间,然后比较得出最大的那个延迟时间就是整个译码器的延迟时间。具体测试是依次将SRAM的每一根地址线拉高,这里设基地base_add为全零地址单元,写入一个数据01010101 (55),向相对偏移地base_add+2n-1(n=1,2,….,n; n=地址位宽)写入一个不同的数据10101010(aa),读取两单元的数据是否正确。

综合上述地址译码器测试图形向量优化实现流程,根据地址译码器的工作原理,设计特定的测试图形向量,保证每次只变换一根地址线,考核地址译码器最大延时时间,达到了对存储器交流参数测试的目的。

6 结论

本文较详尽地介绍了SRAM的动态故障模式,

Test Pattern Analysis of SRAM Dynamic Parameter

ZHANG Ji1, LUO Ximing1, WANG Jun1, TANG Li1, ZHANG Yibo2

(1. Hubei Aerospace Institute of Measurement and Test Technology, Xiaogan 432000, China; 2. Xi’an Dong Yi Science Technology and Industry Group Co., Ltd, CSIC, Xi’an 710065, China)

Abstract:The test method of SRAM includes function parameters, DC parameters and AC parameters. The key are Function parameters and AC parameters. The function test method of SRAM need apply with pattern generator. It can inspect function with read-write operation. The article presents test method and test principle of SRAM Dynamic Parameter, and introduces fault model of it. According to the research of test pattern and vector, the experiment results optimize method of test pattern and vector.

Key words:SRAM; dynamic parameter; test pattern

中图分类号:TN407

文献标识码:A

文章编号:1681-1070(2015)05-0004-03

收稿日期:2015-01-23