基于多核DSP 的FMCW SAR 实时处理设计

2015-07-01张义飞

孔 石,张义飞

(中国空空导弹研究院,河南洛阳 471099)

合成孔径雷达(synthetic aperture radar,SAR)是一种全天候、全天时高分辨率微波遥感成像雷达,自20 世纪50年代以来,其技术得到了飞速的发展。调频连续波(FMCW)合成孔径雷达是一种新近被提出来的成像雷达体制,它具有体积小、质量轻、成本低、分辨率高、低截获概率等一系列优点,可以安装在无人机甚至航模上,将在国民经济和国防建设中发挥越来越大的作用[1-2]。

FMCW SAR 处理运算量大,对计算精度要求较高,所以国内SAR 处理一般采用传统的FPGA +多片浮点DSP 协同并行处理的架构。FPGA 一般用于实现滤波,距离脉压等实时性要求高的计算,而DSP 用于实现精度要求较高的运动补偿以及方位向处理。由于单片DSP 处理性能有限,信号处理涉及多片DSP 并行流水处理以及数据传输设计,系统实现较繁琐[3]。近年来数字信号处理芯片出现了多核发展的趋势[4-5],本研究所介绍的系统采用TI 公司的8 核心1. 25 GHz 主频的DSP TMS320C6678 进行SAR 实时信号处理,其多片互联架构,高存储带宽,通用的串行互连接口整合进一步提升了DSP 的系统综合性能。

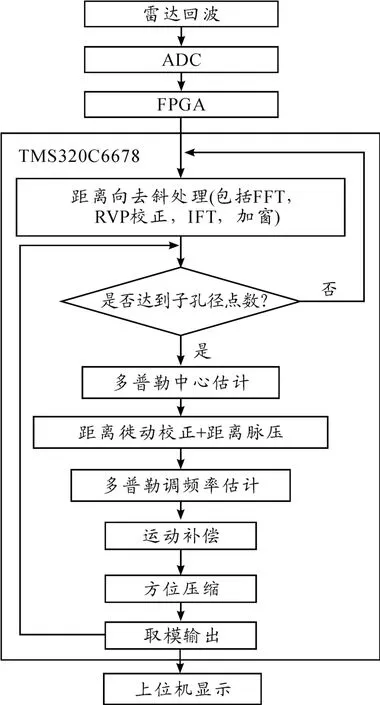

1 基于FMCW 的SAR 实时成像算法流程

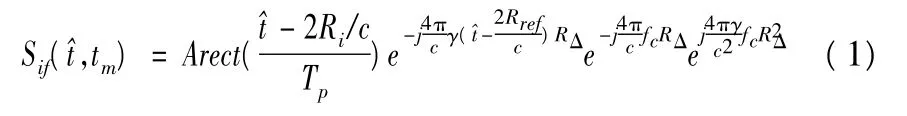

雷达回波与参考信号进行差频处理后,信号形式为其中:^t 为快时间;tm为慢时间;γ 为距离向调频率;Ri为目标到雷达平台的距离;参考距离设为Rref,RΔ=Ri-Rref;在快时间域中,Sif为频率与距离差RΔ成正比的单频脉冲,所以对该差频信号进行傅里叶变换便可在频域得到各距离回波的sinc 状窄脉冲,即脉冲压缩的结果表现在频域里[6]。

式(1)中的第三相位为剩余视频相位(RVP),它会对回波多普勒产生影响,所以应将其去除。不同距离的回波包络在时间上是错开的,希望将不同距离的回波在距离上取其,所以要进行去斜处理,去斜的结果RVP 项也随之消失。去斜因子为

由于雷达与目标的相对运动,二者之间的距离会随时间变化,产生距离徙动,距离徙动的产生模型如图1 所示。

图1 斜视时距离徙动的示意图

由于作用距离近并且子孔径较小,所以距离弯曲量很小,本文只进行距离徙动校正[7]。

载机运动不平稳使雷达与点目标之间的距离变化出现误差,所以需要进行运动补偿。运动补偿主要包括2 个方面:法平面和沿航线运动误差的补偿。由于本文所述系统子孔径很小,假设在单一子孔径内航向速度不变,斜距变化与慢时间无关,所以只补偿法平面内的运动误差[8]。由回波数据可以估计出法平面内的运动加速度,进而得到法向距离误差,构造补偿因子为

其中,r(tm)为由法平面加速度求得的法平面内的运动误差。

合成孔径雷达的方位向信号为线性调频信号,同一目标的能量在一个子孔径时间内是分散的,为了将同一个目标的信号能量聚焦在一起,要对方位信号进行脉冲压缩处理。与距离向脉压方式相同,方位脉压的结果也表现在频域里,参考函数为

其中,fdc与fdr均为由回波数据估计出来的多普勒中心与多普勒调频率。

综合上述步骤,FMCW SAR 实时成像算法流程如图2所示。

图2 FMCW SAR 实时成像算法流程

2 系统硬件设计方案

信号处理硬件主要基于最新的高性能多核DSP 来实现。TMS320C6678 数字信号处理芯片具有8 个核心,当运行在1.25 GHz 的时候,8 核并行峰值浮点性能达160GFLOPS。该DSP 支持三级存储架构,每个内核都配置了32kB 一级程序存储器(L1P),32kB 一级数据存储器(L1D)以及512KB 二级存储器(L2),并具有4MB 的多核共享存储器,每片DSP 外接DDR3 容量高达2GB。增强型直接存储器存取控制器(EDMA3C)可以实现各级存储之间的高速数据流通。TMS320C6678 集成了4 通道Serial RapidIO 接口,可以实现与前端FPGA 的高速互联。该接口可配置为1x(1 通道)、2x(2 通道)、4x(4 通道)工作模式,每个通道速度可配置为1.25 GHz、2.5 GHz、3.125 GHz、5 Gbps。该DSP 还支持千兆以太网接口,可以实现与主机通信[9]。信号处理板的功能框图见图3。

AD 采集的每一个距离向回波数据送至FPGA 缓存,通过高速Serial RapidIO 发送至DSP,在DSP 中首先进行距离向处理,处理完后将数据发送至DDR3 SDRAM 中,待以后方位向处理。当距离向积累满一个子孔径后,DSP 再将数据从DDR3 中读出进行参数估计、徙动校正、运动补偿、方位压缩等处理。方位向处理完成后再将数据发送至DDR3 中,留作以后的拼图用。

图3 功能框图

3 系统软件设计方案

3.1 TMS320C6678 多核任务分配与同步

DSP 工作模式为数据流模式(Data Flow Model),核0 —核3 进行距离向处理;核4 — 核7 并行处理之后的算法,包括多普勒中心估计、距离徙动校正、多普勒调频率估计和方位压缩。数据流通模式如图4 所示。

DSP 外挂DDR3 SDRAM 所需容量分析:Page1:原始数据为16 384 ×512 点复数矩阵,共64 MB,Page2:距离向处理结果为16 384 ×512 点复矩阵,共64 MB,Page3:距离徙动校正之后每个距离向截取有效地2048 点,校正结果为2 048 ×512 点复矩阵,共8 MB,Page 4:矩阵转置结果为512 ×2 048点复矩阵,共8 MB,Page 5:成像结果为2 048 ×512 点的实矩阵,共4 MB。因为距离向数据是不断采集的,在进行前一个子孔径的方位向处理时,下一个子孔径的距离向数据在不断积累,所以还需要128 MB(Page1 +Page2)的空间用于子孔径积累。所需DDR3 SDRAM 总容量为276 MB。

采用信号量(Semaphore)进行多核同步,信号量的获取(Acquire)与释放(Release)可以向DSP 核产生中断,通知DSP 进行算法处理。此种同步方式与BIOS 同步相比,不仅操作简单便于调试,而且代码量大大减小。

图4 数据流通模式

3.2 TMS320C6678 实时成像软件设计

该系统针通过将SAR 二维回波数据进行分块操作,充分发挥TMS320C6678 多核并行处理的优势,实现实时成像,DSP 实时成像处理流程为:

第一部分:进行距离向去斜处理,移除回波信号的剩余视频相位。FPGA 通过Serial RapidIO 接口向DSP 发送前端AD 采集的回波数据,DSP 核0 至核3 的协调工作模式为:FPGA 将第i 个距离向数据发送至DSP core0 的L2,core0 接受完成后会响应中断,进入中断服务子函数处理第i 个距离向数据;FPGA 发送完第i 个距离向后,开始向DSP core1 发送第i+1 个距离向,core1 接受完成后响应中断,处理第i+1个距离向。以此类推,后面的距离向依次发给core2,core3。每个核接收距离向的时间间隔为1/PRF×4 = 2 ms,所以每个距离向的处理时间必须控制在2 ms 内,单核距离向处理时间为1.158 2 ms,满足实时性要求。各核将处理之后的距离向数据通过DMA 搬至DDR3 SDRAM 中,当方位向点数积累至512 点时开始进行以下算法处理。

第二部分: 多普勒中心估计。选取一部分场景(800 ×512)进行估计,虽然本部分算法按方位向进行处理,但是由于数据量较小,且只进行一次操作,所以不需要进行矩阵转置。将数据按距离向分块,每核处理的数据量为200 ×512点。需要在DSP 的共享存储器(MSM)中开辟一个长度为800 点的浮点类型数组,用来存放由每个方位向数据估计出来的角度,最后再由各核将其读出,取中值得多普勒中心。涉及MSM 的读写操作要维护好cache 一致性。

第三部分:校正距离徙动与距离脉压。距离徙动按距离向进行处理,每核需要处理的数据量为16 384 ×128 点,校正完成后每个距离向截取2 048 点。

第四部分: 矩阵转置。第三部分的结果数据在DDR3 SDRAM 中按距离向存放,因为之后的多普勒调频率估计和方位压缩均要按方位向操作,所以要进行矩阵转置。转置之后利于DMA 按帧连续读取,相比按地址跳转读取节省了时间。采用分块转置的方法:首先将大块矩阵(2 048 ×512)分成小块矩阵(128 ×128),再将各小块矩阵进行转置,最后将各转置之后的小块矩阵拼接起来,这样就完成了整个大矩阵的转置。每核进行512 ×512 点的复矩阵转置,将转置之后的矩阵拼接成2 048 ×512 点的大矩阵。矩阵转置前后的数据都要保存,转置前的数据存放在DDR3 Page 3 中,用于后面的运动补偿,转置之后的结果存放在DDR3 Page 4 中,用于多普勒调频率估计和方位脉压。转置过程在DSP 中的操作如图5 所示。

第五部分:多普勒调频率估计。取能量最大的前160 个方位向进行估计,所以每个核需处理的数据量为40 ×512 点的复矩阵,此处涉及对MSM 的读写操作,故也需要维护cache 一致性。

第六部分:运动补偿。按距离向进行补偿,每核处理的数据量为2048 ×128 点的复矩阵。

第七部分:方位压缩。构造方位向补偿因子,各核处理数据量为512 ×512 点的复矩阵,对方位压缩结果取模输出,至此子孔径成像完成。

图5 矩阵转置操作示意图

3.3 系统实验参数说明

实验中的雷达参数为:发射信号带宽B =300 MHz,脉冲宽度Tp=5e -4 s,波长λ =8.6 mm,脉冲重复频率PRF =2 000 Hz,飞行速度v=52 m/s,中心斜距Rs=5 260 m,斜视角φ=1.084 2°。每个子孔径距离向采样点数为16 384 点,方位向采样点数为512 点。

3.4 软件效率分析

距离向处理时间分析如表1 所示。

表1 DSP 处理每个距离向效率ms

因为PRF=2 000 Hz,所以2 个距离向的产生间隔为500 μs,但是DSP 处理一个距离向需要1.158 2 ms,所以4 个核处理距离向是可以满足实时性要求的。

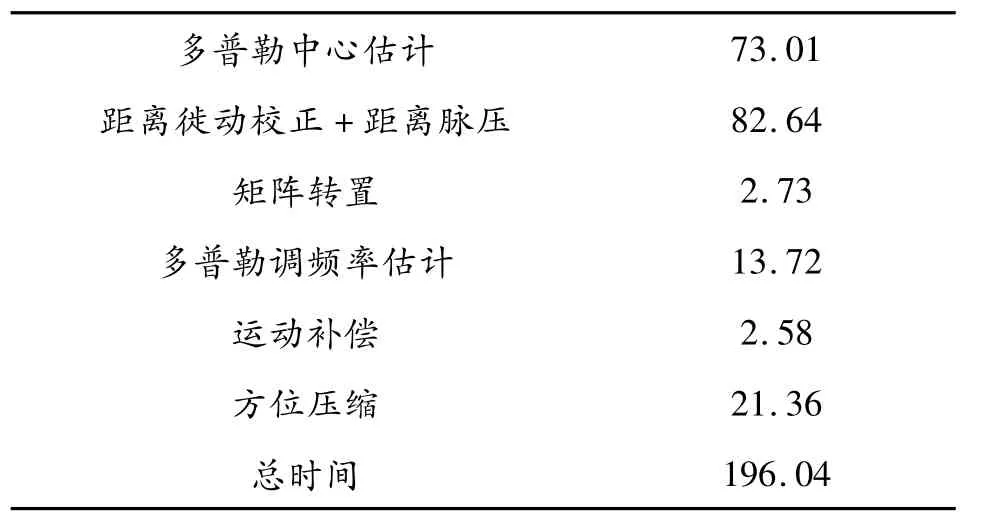

算法各步骤效率分析如表2 所示。

表2 软件各部分效率ms

距离向累积512 点所需时间为: 500 μs ×512 = 256 ms,核4 ~核7 进行算法处理只需196.04 ms,所以,此雷达成像系统可以满足实时性要求。

4 结论

本研究分别从FMCW SAR 成像算法,系统硬件设计以及多核DSP 软件设计3 个方面介绍了雷达实时成像系统的工作方式和流程。选择新型多核DSP 芯片作为主处理器,充分发挥其强大的浮点处理能力,利用多核并行处理算法,提高了系统综合性,避免了多片处理器的分散设计与调试,不仅节省了硬件资源,而且方便了软件设计,提高了成像效率。

[1]van Rossum W,Otten M,van Dorp P.Multichannel FMCW SAR[C]//The 9th European conference on Synthetic Aperture Radar,Nuremberg,Germany,2012:279-282.

[2]Meta A,Hoogeboom P,Ligthart LP. Signal Processing for FMCW SAR[J].IEEE Transactions on Geoscience and Remote Sensing,2007,45(11):3519-3532.

[3]Eugin Hyun,Woojin Oh,Jong-Hun Lee.Design and implementation of automotive 77 GHz FMCW radar system based on DSP and FPGA[C]//2011 IEEE International Conference on Consumer Electronics (ICCE). Las vegas,NV,2011:517-518.

[4]Gatherer Alan,Biscondi E. Multicore DSP programming models[In the Spotlight][J].IEEE Signal Processing Magazine,2009,26(6):220-222.

[5]Karam L J,AlKamal I,Gatherer Alan,et al.Trends in multicore DSP platforms[J].IEEE Signal Processing Magazine,2009,26(6):38-49.

[6]Ian G.Cumming,Frank H.Wong.合成孔径雷达成像—算法与实现[M]. 洪文,胡东辉,译. 北京:电子工业出版社,2007.

[7]保铮,邢孟道,王彤.雷达成像技术[M].北京:电子工业出版社,2005.

[8]包敏,周松,史林,等.一种适用于宽测绘带弹载SAR 成像的运动补偿方法[J].西安电子科技大学学报,2013,40(4):188-196.

[9]Jieming M,Kerem K,Murtaza A,et al.Ultrasound phase rotation beamforming on multi-core DSP[J]. Utrasonics,2014,54(1):99-105.