基于NiosⅡ的LVDS图像数据存储转发系统的设计*

2015-06-23孟令军李加超赵盼盼

孟令军,李加超,文 波,赵盼盼

(中北大学电子测试技术国家重点实验室,太原 030051)

基于NiosⅡ的LVDS图像数据存储转发系统的设计*

孟令军,李加超,文 波,赵盼盼

(中北大学电子测试技术国家重点实验室,太原 030051)

针对高速图像数据的远距离传输提出了一种基于NiosⅡ处理器的LVDS图像数据存储转发系统的设计方案,详细介绍了LVDS图像数据的存储方法和数据转发的工作原理,并对该系统的软硬件设计以及各功能模块的具体实现原理进行了分析和实际测试,实验结果验证了该设计的可行性、稳定性及高效性。

NiosⅡ处理器,LVDS,乒乓结构,DMA

0 引言

随着遥测采集技术的迅速发展,数据的高速、可靠传输已经成为当前遥测领域研究的热点问题,传统的串行和并行数据传输方式由于其速度和距离方面的限制逐渐成为系统整体性能的瓶颈,而LVDS数据传输方式以其速度和可靠性的优势在图像采集系统中得到广泛应用。同时Altera公司的NiosⅡ系统是一种以FPGA作为物理载体、可按需求定制的嵌入式系统,具有很强的灵活性、稳定性和可操作性,广泛应用于高速数字图像处理领域[1]。

1 基本原理

1.1 NiosⅡ系统

NiosⅡ系统是Altera公司基于SOPC(System on Programmable Chip,片上可编程系统)技术推出的一种高效、灵活、可配置的嵌入式系统,设计方式灵活,开发周期短,可升级、可扩充、可裁减,具有很强的移植性,并具备软硬件在系统上可编程的功能[2]。

1.2 LVDS技术

LVDS(Low Voltage Differential Signaling)是一种低振幅差分信号技术,它采用恒流源模式和低幅度电压信号驱动,使用幅度非常低的信号(约350 mV)通过平衡电缆或一对差分信号线传输数据,系统功耗低,且不易受共模噪声的影响,传输速率可以达到数百兆位每秒。目前,LVDS技术在对信号完整性和共模特性要求较高的高速数据传输系统中得到越来越广泛的应用。

2 系统设计

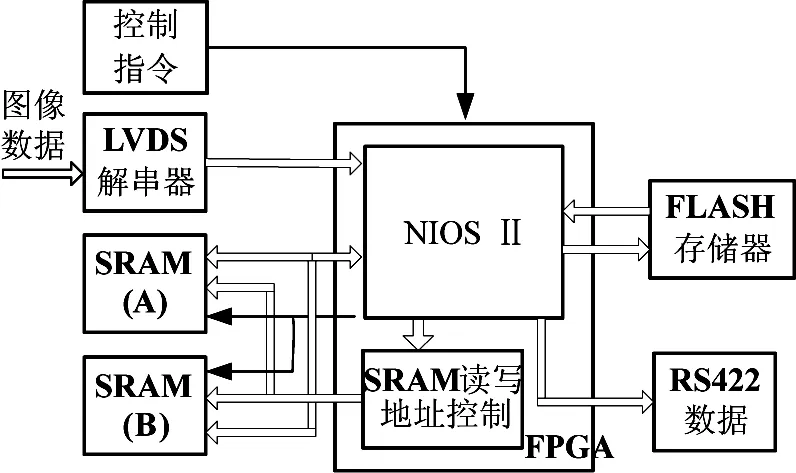

图像数据存储转发系统主要是利用NiosII嵌入式系统稳定可靠的优势和LVDS数据传输的功耗低、速度快、干扰少的特点完成LVDS图像数据的存储和特定帧的图像转发功能。系统采用两片SRAM构成的乒乓缓存结构保证图像数据的实时性和完整性,利用DMA方式存储实时接收到得图像数据。系统的设计结构框图如图1所示,NiosII嵌入式处理器将LVDS接口解串后的图像数据通过乒乓模式存储到两片片外扩展的SRAM中进行缓冲,然后将数据从SRAM中读出并以DMA方式将数据存储到FLASH中或者将图像数据通过RS422进行转发。

2.1 NiosⅡ嵌入式处理器

NiosII嵌入式处理器是基于Altera公司推出的CycloneⅢ系列(EP3C120F484)FPGA芯片实现的,在构建NiosⅡ嵌入式处理器软内核时,根据系统要实现的功能选择合适的处理器类型和外部设备,然后通过QuartusⅡ和SOPC Builder生成具有相应功能的软核[3]。同时,NiosII嵌入式处理器还可以通过VHDL、Verilog语言或者使用第三方的IP核定制用户外设和用户指令来实现各种需求。系统的配置组建及接口模块如图 2所示,NiosII处理器与MAX9218通过PIO接口进行通讯,串行FLASH用于存储整个系统程序,SRAM用于缓存采集到的图像数据,方便系统进行数据存储和实时数据上传分析,SDRAM用作系统内存,整个系统程序在SDRAM内运行。

图1 系统设计结构框图

图2 NiosⅡ处理器配置的组件图

2.2 DMA数据转存

为了提高NiosII处理器的数据处理速度,在系统中引入了DMA控制器。在DMA数据传输方式下,DMA控制器接管了总线的控制权,并以中断的方式向处理器报告传送操作的结束。采用DMA数据传输方式省去了处理器先读入数据,再把数据输出的操作,大大节省了数据传输的时间和系统资源,也减轻了处理器传输数据的负担[4]。

由于图像数据传输速度比较快,瞬时速率达到70 MB/s,这远远大于Flash的写入速度,为了解决图像数据的接收和存储之间的速率匹配,需要在系统的输出端加入异步FIFO,在数据处理单元、FIFO以及FLASH之间形成以DMA方式直接控制高速数据传输模式。为了保证图像在存储过程中的完整性,系统采用两片高速SRAM交替工作完成图像数据无缝缓存,构成乒乓机制工作状态,在一片SRAM执行DMA传输的同时另一片执行写操作,这样不会造成数据丢失,状态也比较容易控制。同时在SRAM中设置了帧缓冲,主要利用帧与帧之间的消隐间隔来完成DMA传输,将缓存在SRAM中的一帧数据搬移到片内FIFO,提高了数据传输效率。

2.3 LVDS数据接收

LVDS接收模块主芯片采用27 Bit,速度最高可达35 MHz的MAX9218 LVDS解串芯片,该芯片可以解串发送端串化芯片对应引脚上所串化出来的电平特性,其具体数据传输位数可以根据设计需求进行配置,在本设计中所接收的数字图像格式为:320列×256行×16位,图像采样位数为16bit/像素,采用16 bit带宽35 MHz的速度进行数据传输,芯片的数据位(RGB_OUT16)用来接收表示行同步的信号(HSYN),因此,只利用了其中17个包含数据同步信号的并行数据输出引脚,其他没有使用的引脚可以悬空。在更高速度和位数要求的设计中LVDS串化和解串速度可根据具体情况选择速度更快和位数更多的 LVDS串化和解串芯片[5],MAX9218解串时的数字图像时序如图3所示。

图3 MAX9218解串时序图

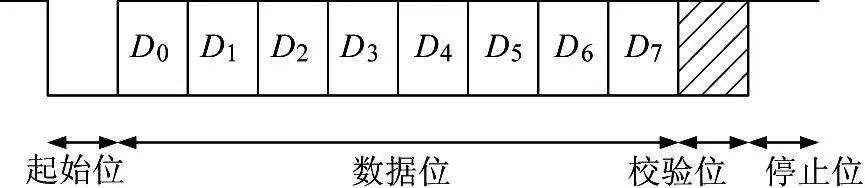

2.4 图像数据转发

该系统的图像实时转发功能用于其他设备进行图像数据处理,图像数据转发模块采用标准异步串行RS422接口,该接口数据传输率最大可达10 Mbit/s。该系统采用2.5 Mb/s的波特率,在进行转发图像数据的过程中,首先从SRAM中读出16位图像数据,最初转发的低电平作为低16位图像数据的起始位,待图像数据和奇校验位传输结束后以高电平作为这一次数据包传输的停止位,然后再以同样的过程传输高8位图像数据,至此1个像素的数据传输完毕。RS422图像数据传输格式如图4所示。

图4 RS422图像数据传输格式

图5 上位和还原图像

3 系统调试结果

图5为上位机还原出的图像,其中图5(a)为NiosⅡ嵌入式处理器根据控制指令将某一时刻SRAM中缓存的图像数据经过异步串行接口转发出去的图像,图5(b)为FLASH存储器中相同时刻存储的原始图像,实现了图像数据的实时存储和特定转发功能,满足了设计要求。

4 结束语

本文介绍了一种基于NiosⅡ处理器的LVDS图像数据存储转发方案,实现了高速LVDS图像数据的接收、实时存储和转发。设计中采用了SRAM乒乓缓存结构和DMA数据传输机制,增强了整个系的统数据处理能力,保证了图像数据的连续性和完整性;采用SOPC技术构建NiosⅡ嵌入式处理器,具有较强的移植性,使整个系统的性能有了很大提高,适用于通讯、雷达、电子对抗等高速数字图像处理设备中,应用前景十分广泛。

[1]邹晨,高云.FPGA内嵌处理器的SOPC系统设计与分析[J].航空计算技术,2013,43(5):123-127.

[2]李兰英.NiosII嵌入式软核SOPC设计原理与应用[M].北京:北京航空航天大学出版社,2006.

[3]张可,焦国太,彭晴晴.基于SOPC的LVDS数据接收系统设计[J].火力与指挥控制,2012,37(9):143-145.

[4]蔡伟纲.NiosII软件架构解析(第一版)[M].西安:西安电子科技大学出版社,2007.

[5]Ning H W,Zhen G Y,Ren Y F.AN Optimal Design of LVDS Interface[J].Computer Science and Network Technology,2011(3):2024-2026.

Design of LVDS Image Data Storage and Retransmit System Based on NiosⅡ

MENG Ling-jun,LI Jia-chao,WEN Bo,ZHAO Pan-pan

(National Key Laboratory For Electronic Measurement Technology,North University of China,Taiyuan 030051,China)

In this paper,a design of LVDS image data storage and retransmit system based on NiosⅡ processor is presented.The method of LVDS image data storage and retransmit are completed a detailed explanation.In terms of hardware and software design,the discussion about the principium of each functional module is proposed.Functional realization of the system is tested one by one,the test results demonstrate the feasibility,reliability and high efficiency of this design.

NiosⅡprocessor,LVDS,ping-pong structure,DMA

TN402

A

1002-0640(2015)05-0143-03

2014-03-07

2014-04-21

国家自然科学基金资助项目(51275492)

孟令军(1969- ),男,山东青岛人,副教授,硕士生导师。研究方向:微纳仪器及测试技术、集成测试系统及仪器。